据报道,华为已开发了(并申请了专利)一种芯片堆叠工艺,该工艺有望比现有的芯片堆叠方法便宜得多。该技术将帮助华为继续使用较老的成熟工艺技术开发更快的芯片。 唯一的问题是华为是否真的可以利用其创新,因为没有美国政府的出口许可证,代工厂无法为该公司生产芯片。但至少华为自己当然相信它可以,特别是考虑到这项技术可以为基于不受美国如此严厉限制的旧节点的芯片提供性能提升。

保持竞争力的一种方式

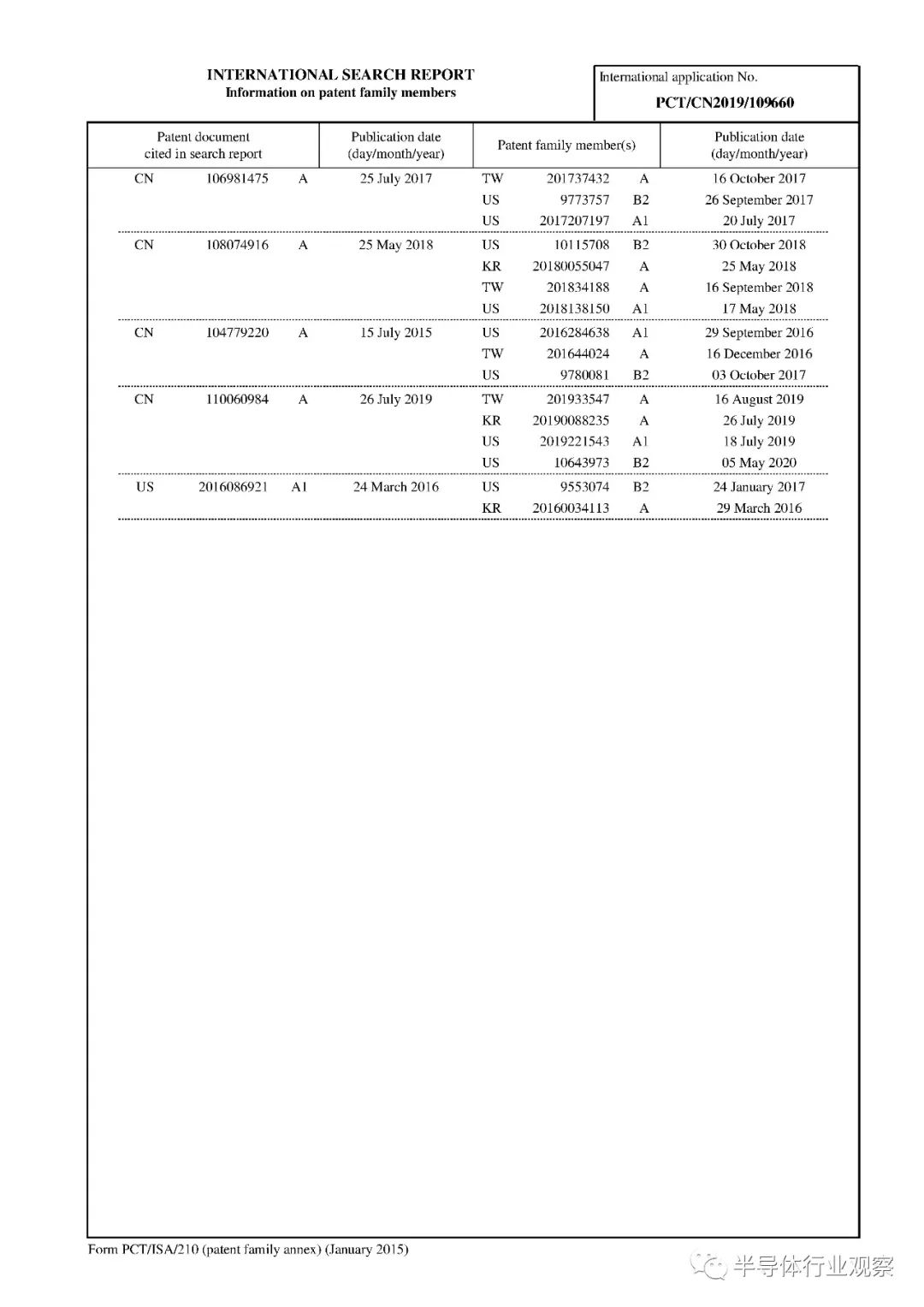

我们将在下面详细介绍这项新技术,但重要的是要了解华为为什么要开发这项新技术。 由于美国政府将华为及其芯片设计子公司海思列入黑名单,现在要求所有制造芯片的公司申请出口许可证,因为所有半导体生产都涉及美国开发的技术,华为无法进入任何先进节点(例如台积电的N5),因此必须依赖成熟的工艺技术。 为此,华为前任总裁郭平表示,创新的芯片封装和小芯片互连技术,尤其是 3D 堆叠,是公司在其 SoC 中投入更多晶体管并获得竞争力所需性能的一种方式。因此,该公司投资于专有的封装和互连方法(例如其获得专利的方法)是非常有意义的。 “以 3D 混合键合技术为代表的微纳米技术将成为扩展摩尔定律的主要手段,”郭说。 华为高层表示,由于现代领先的制程技术进展相对缓慢,2.5D或3D封装的多芯片设计是芯片设计人员不断在产品中投入更多晶体管,以满足他们客户在新功能和性能的预期,这也成为了产业界采用的一个普遍方式。因此,华为前董事长强调,华为将继续投资于内部设计的面积增强和堆叠技术。 华为在新闻发布会上公开发表的声明清楚地表明,公司旨在为其即将推出的产品使用其混合无 TSV 3D 堆叠方法(或者可能是类似且更主流的方法)。主要问题是该方法是否需要美国政府可能认为最先进且不授予出口许可证的任何工具或技术(毕竟,大多数晶圆厂工具使用源自美国的技术)。也就是说,我们是否会看到一家代工厂使用华为的专利方法为华为制造 3D 小芯片封装,这还有待观察。但至少华为拥有一项独特的廉价 3D 堆叠技术,即使无法使用最新节点,也可以帮助其保持竞争力。

无过孔堆叠

创新的芯片封装和多芯片互连技术将在未来几年成为领先处理器的关键,因此所有主要芯片开发商和制造商现在都拥有自己专有的芯片封装和互连方法。

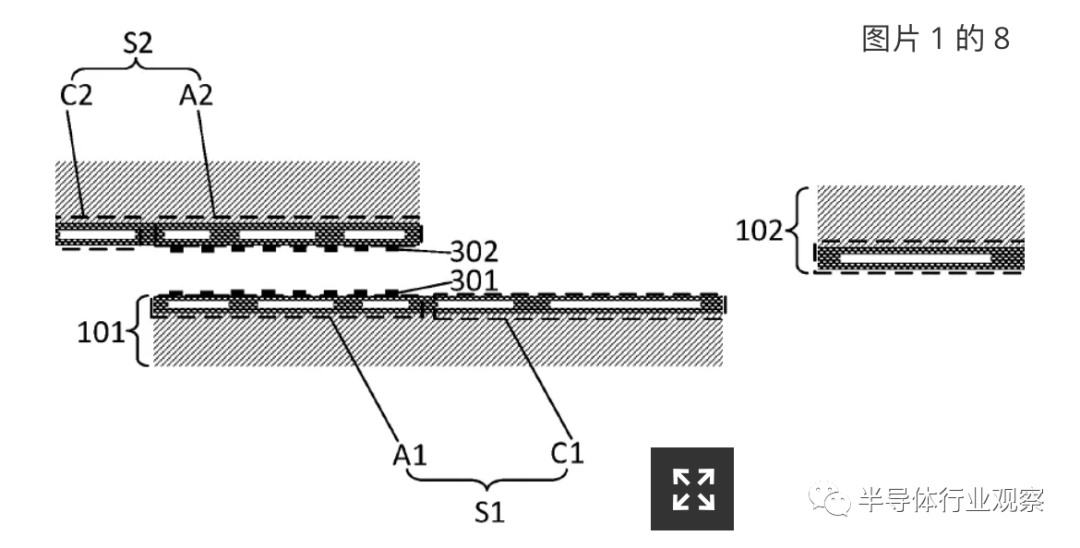

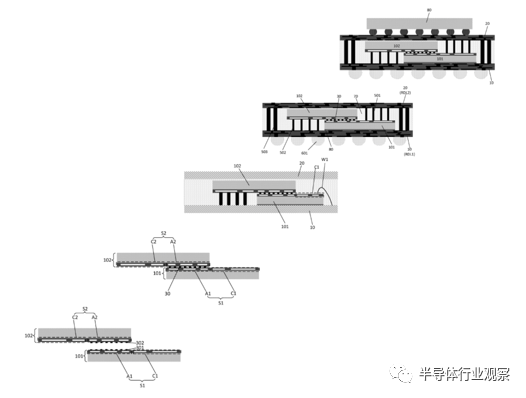

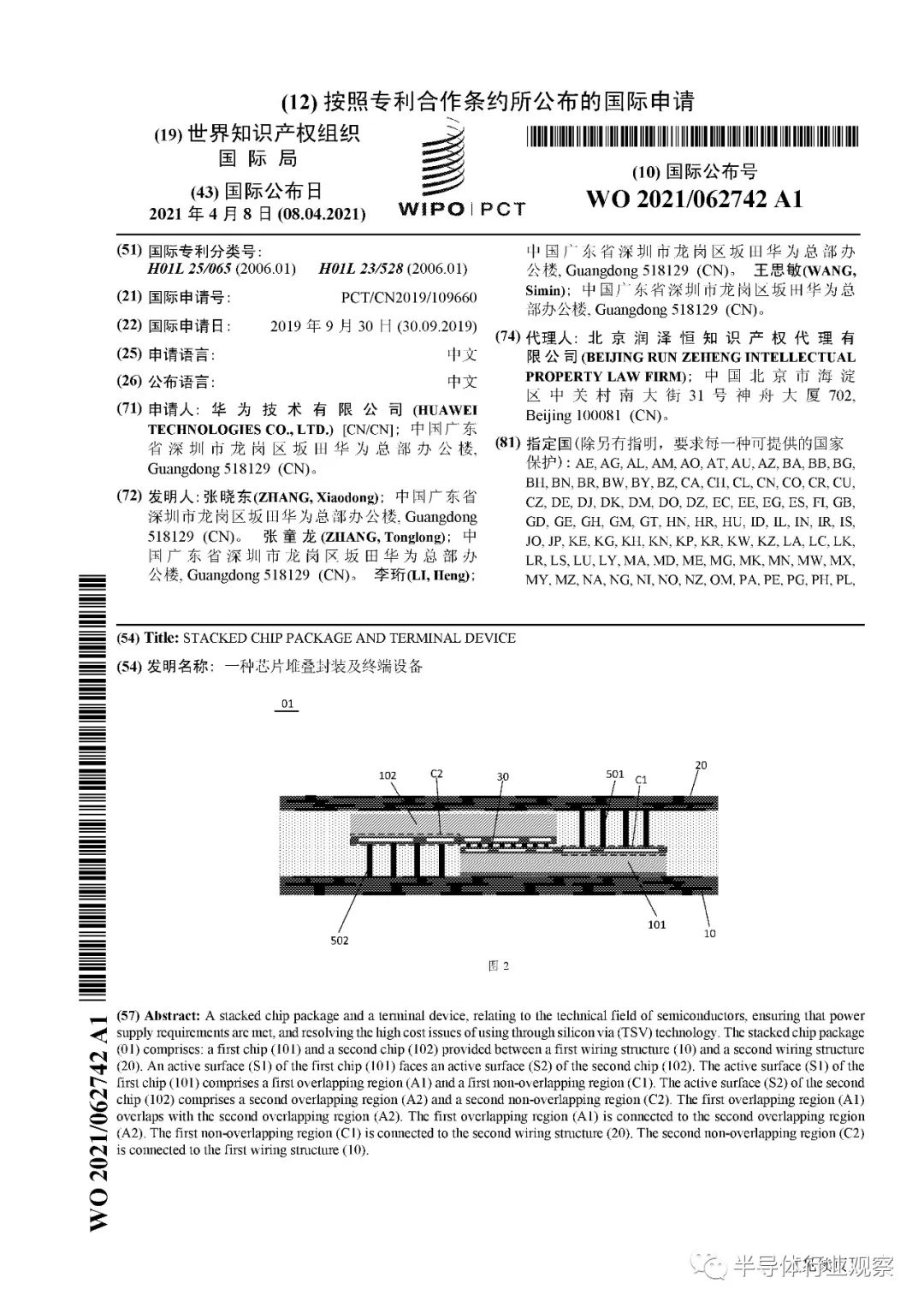

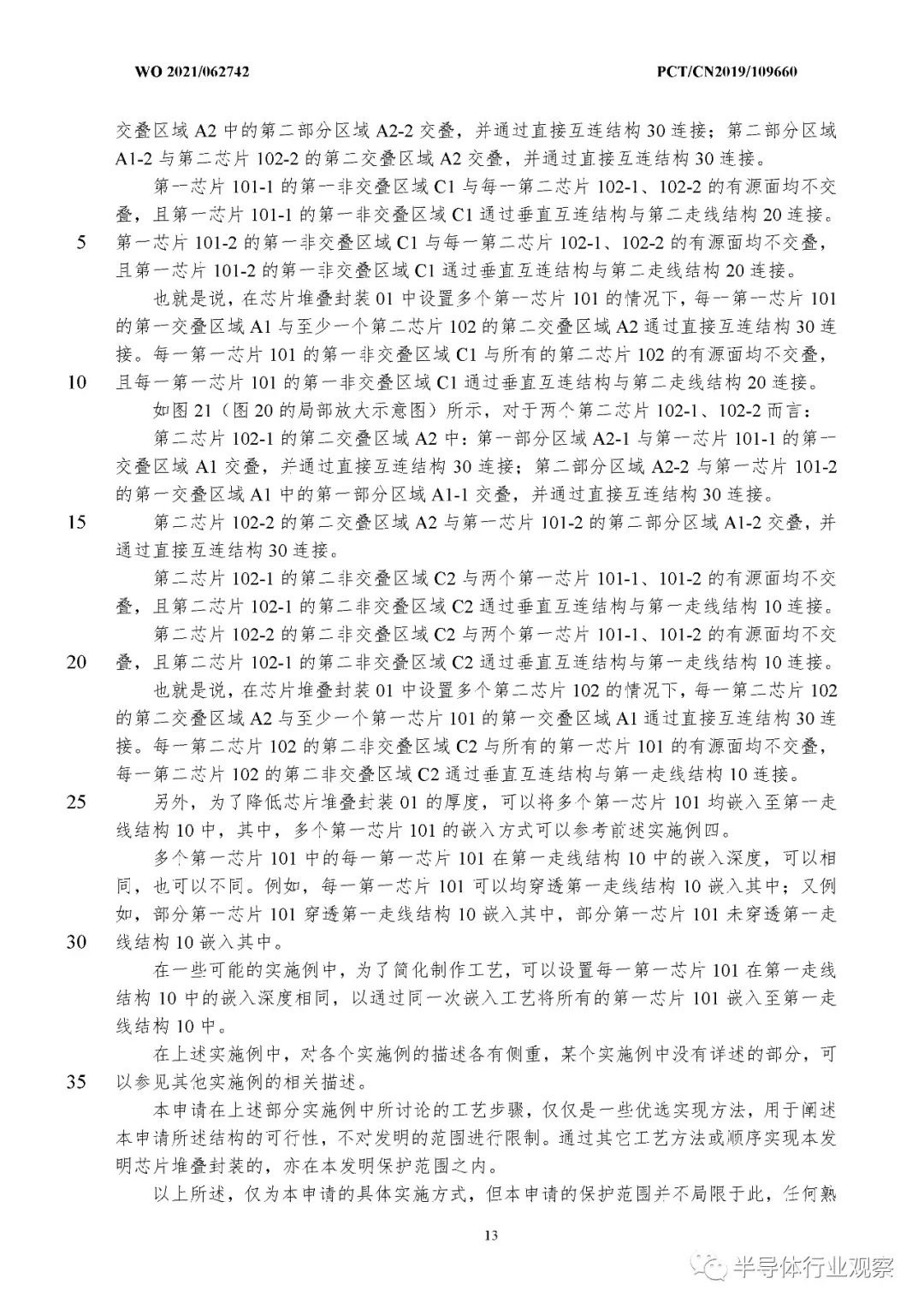

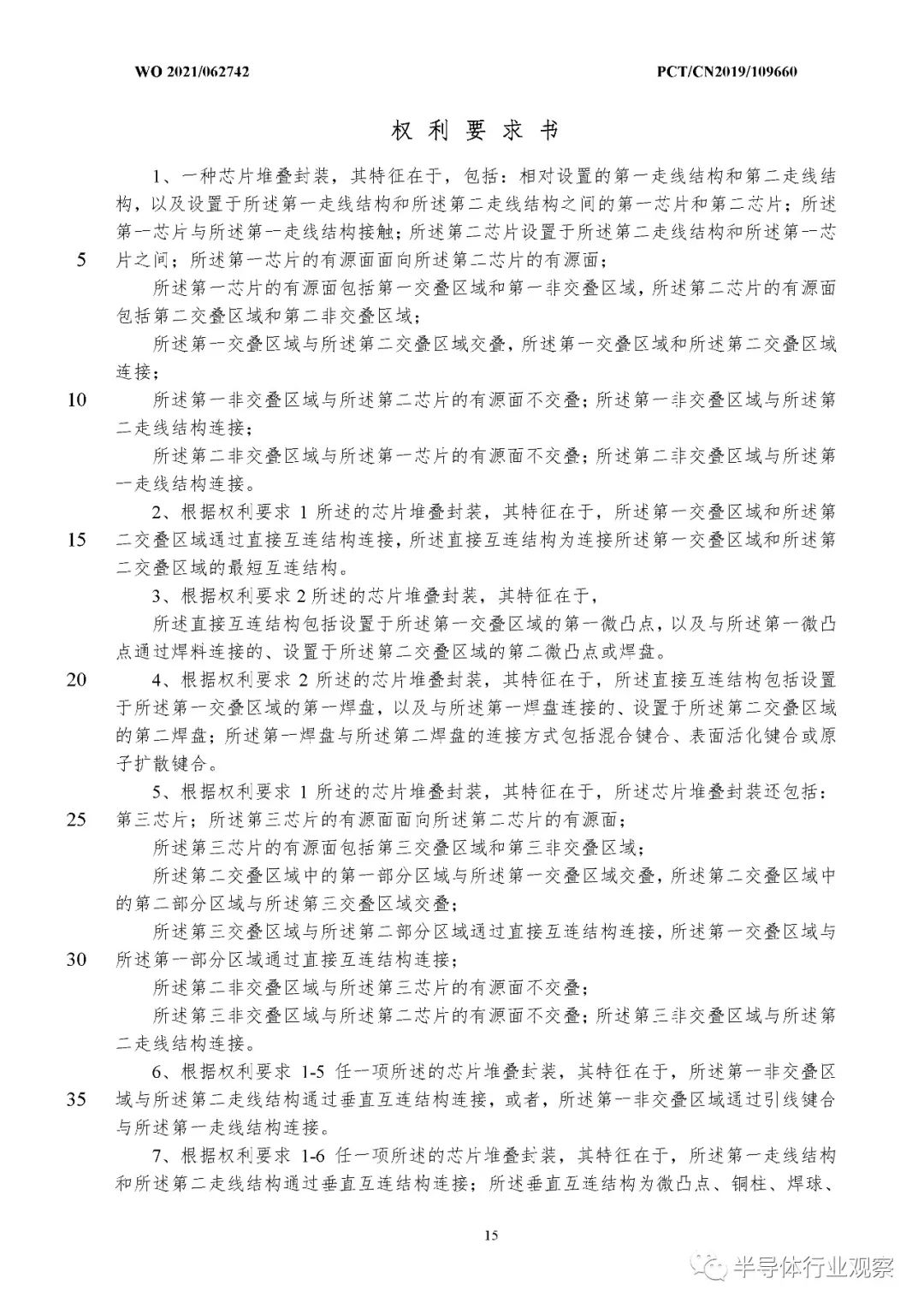

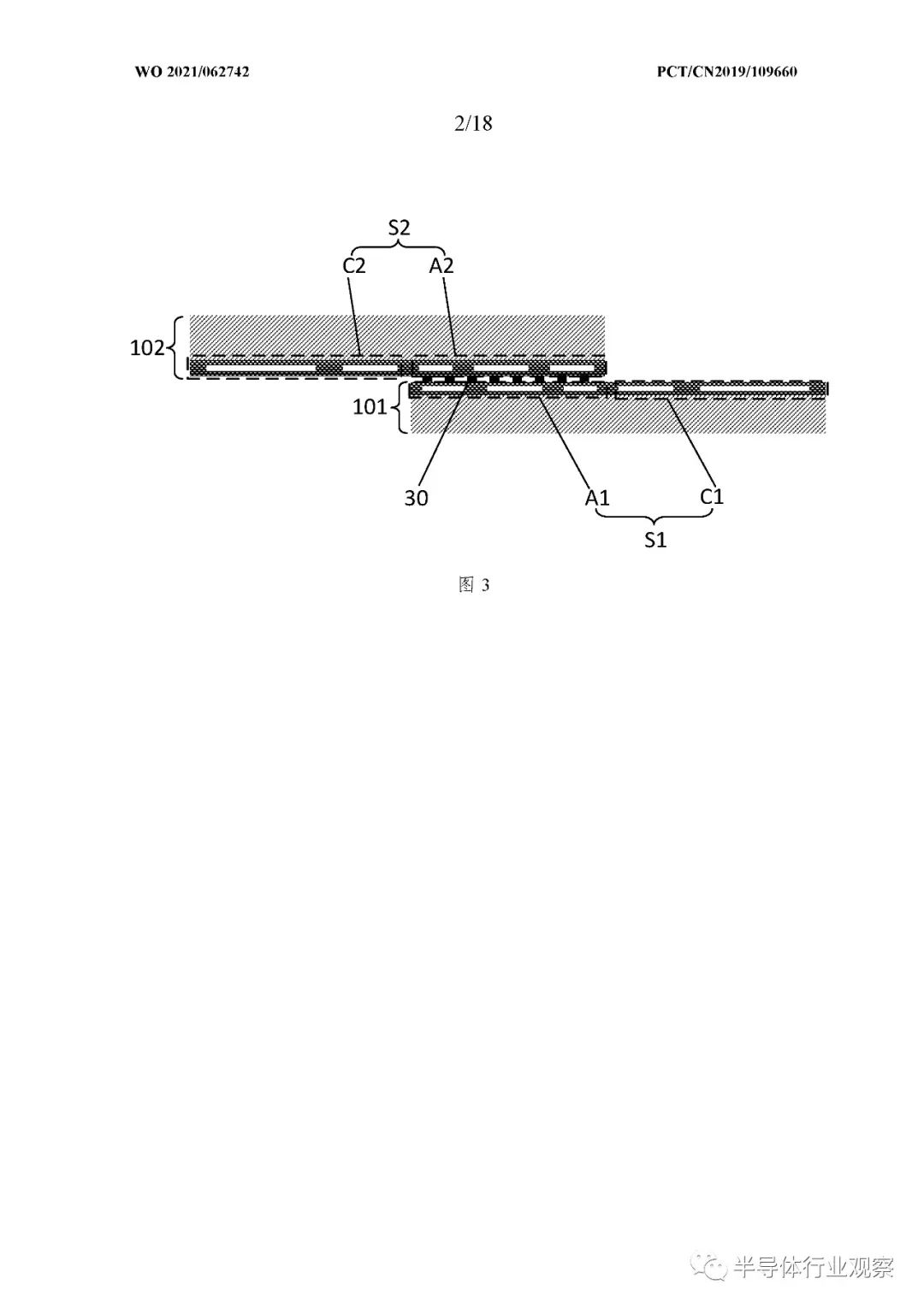

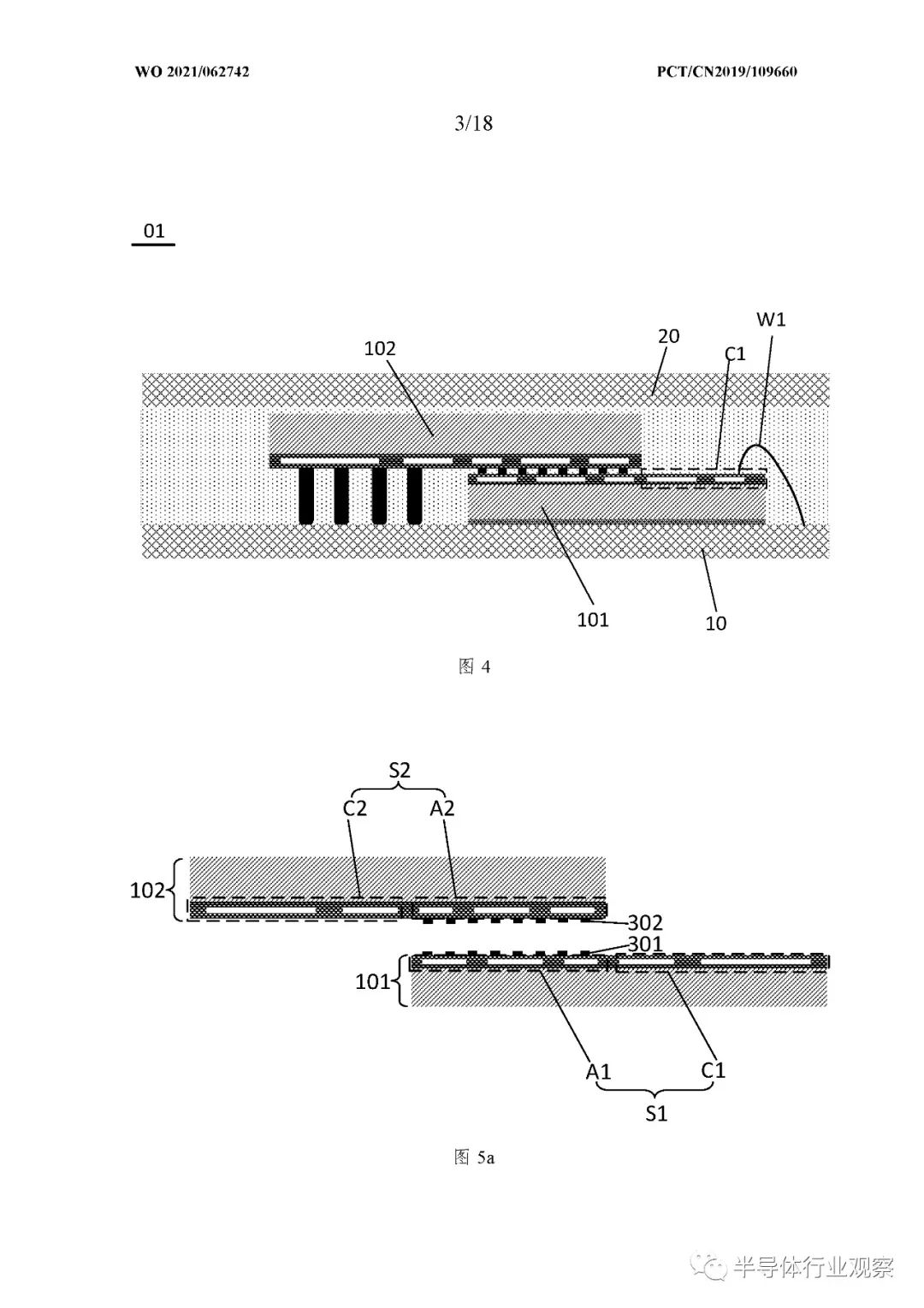

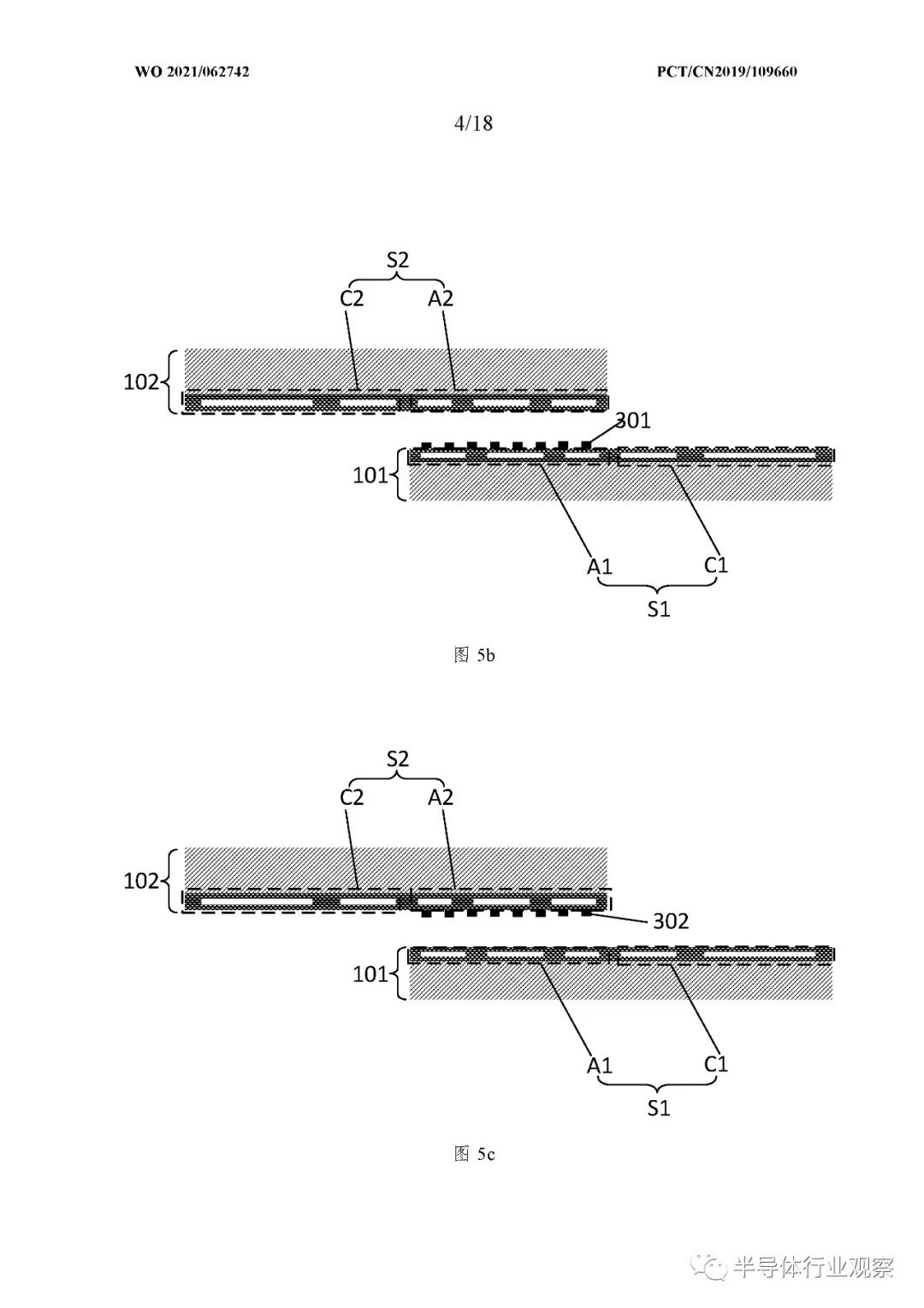

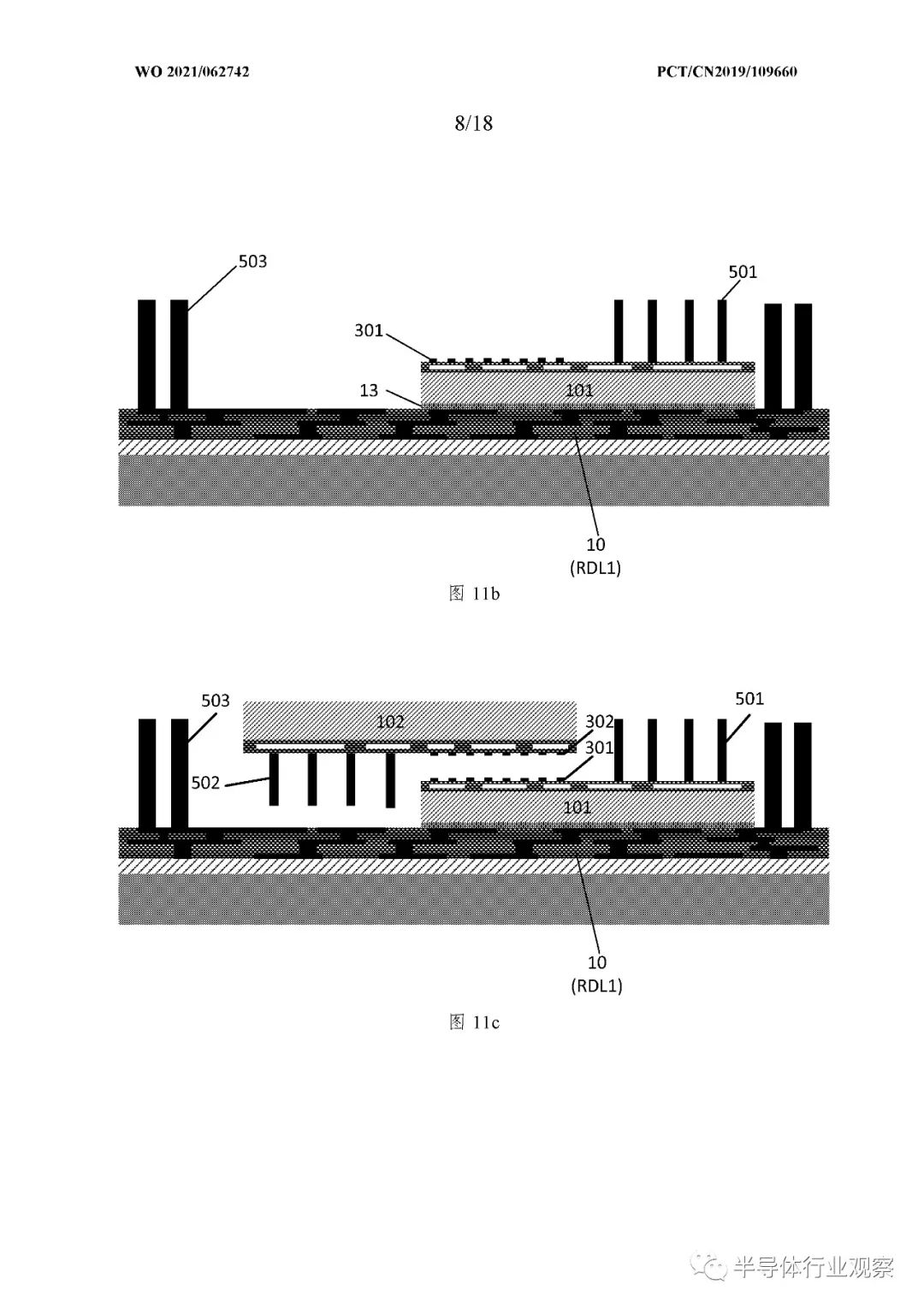

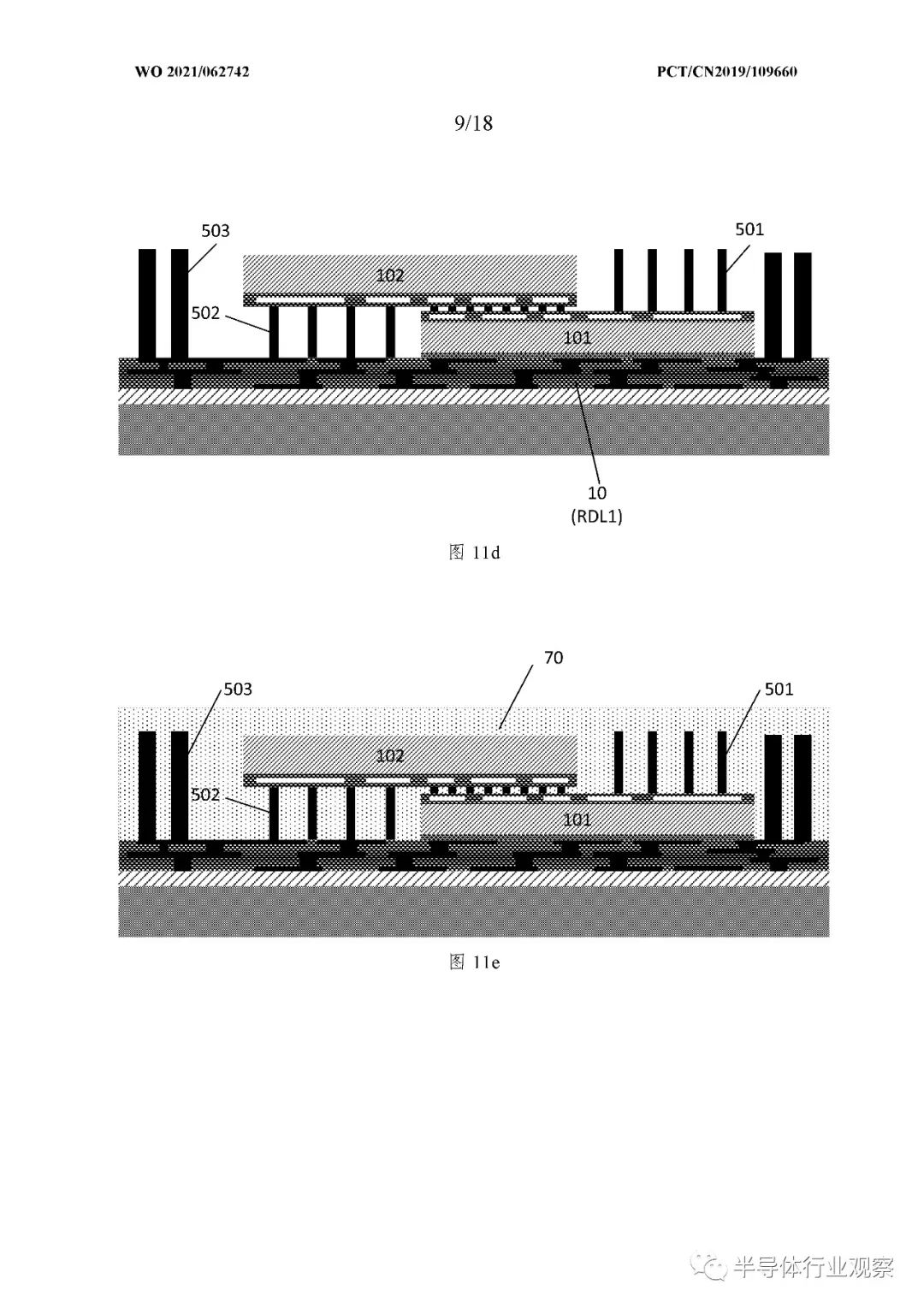

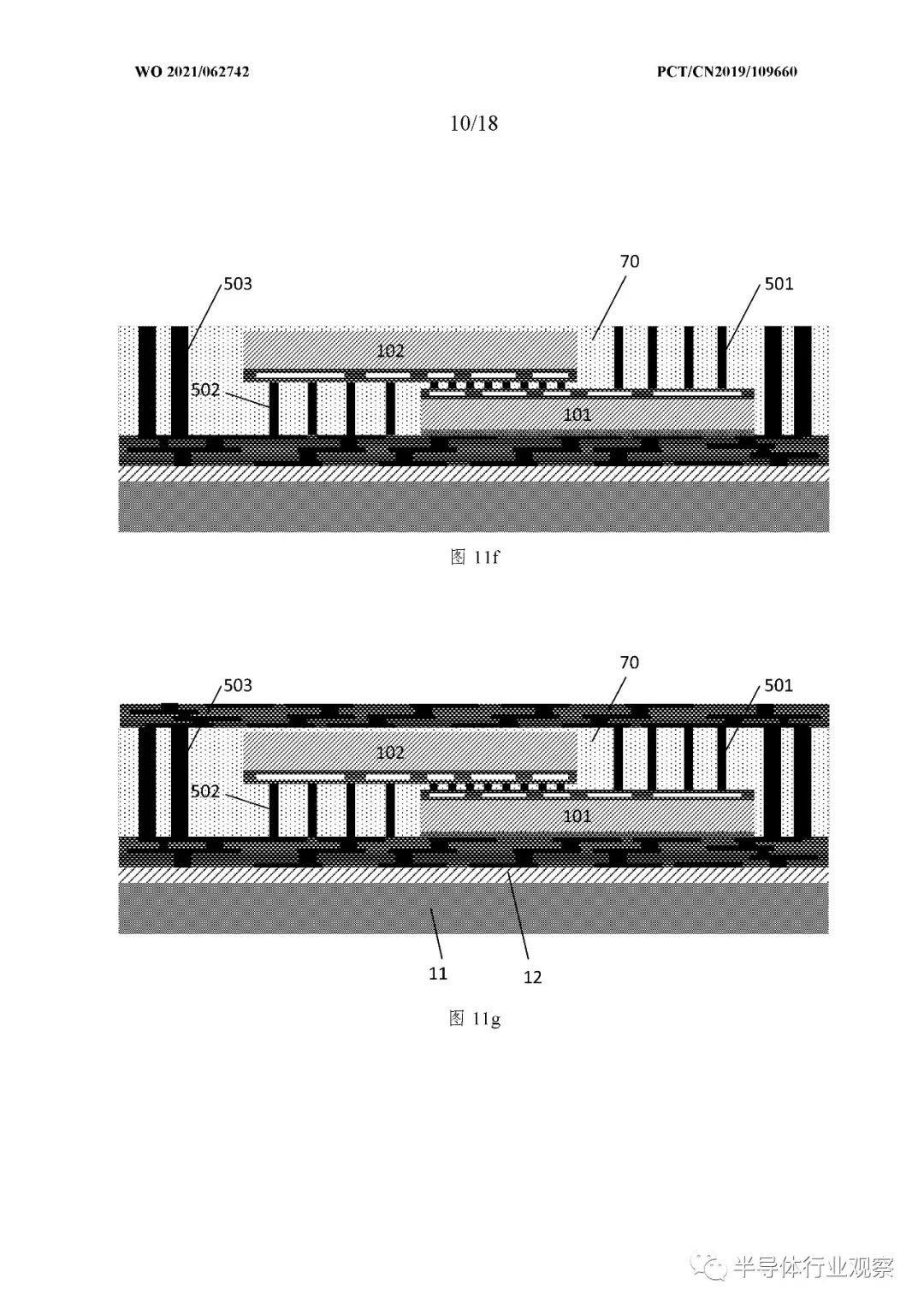

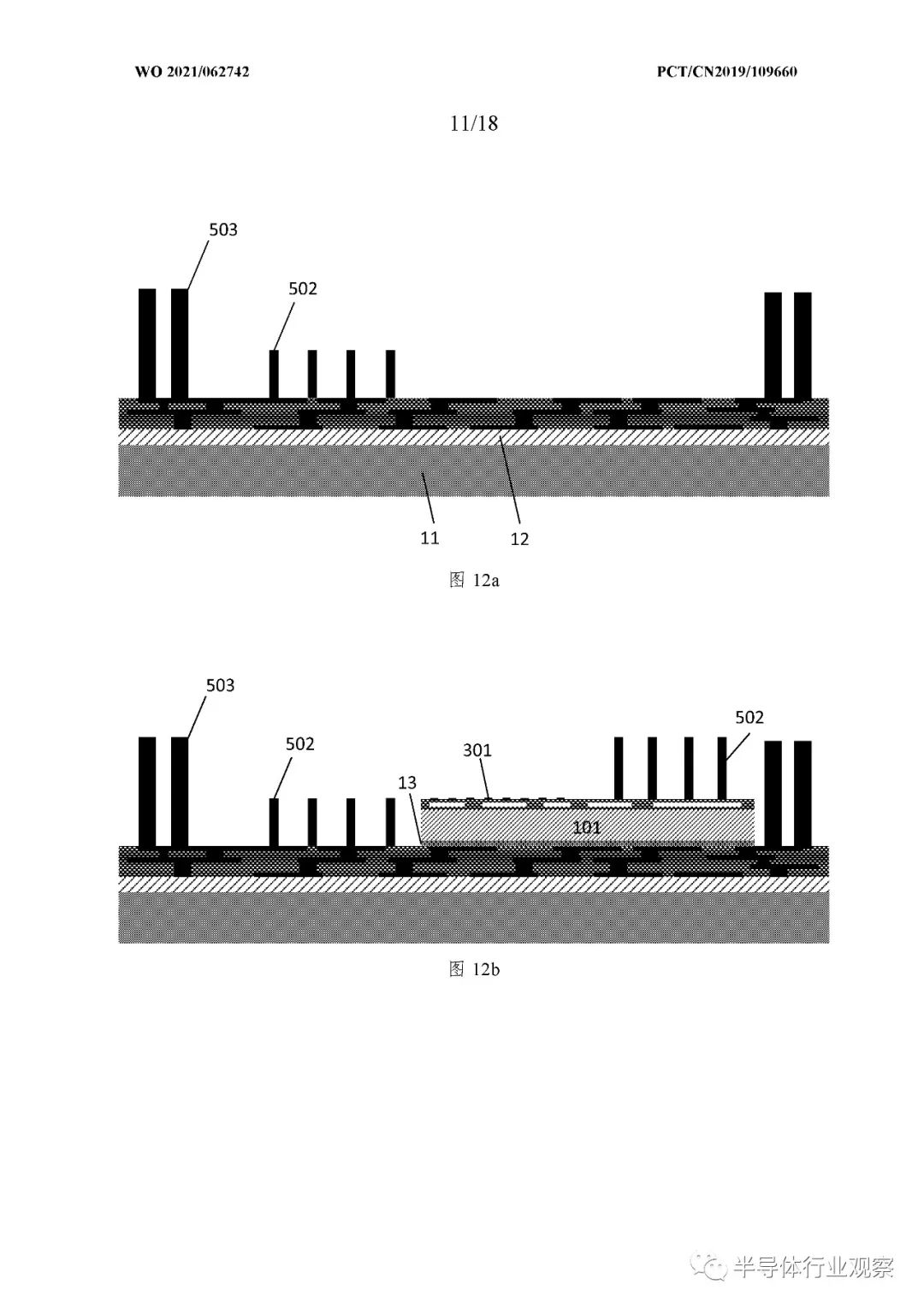

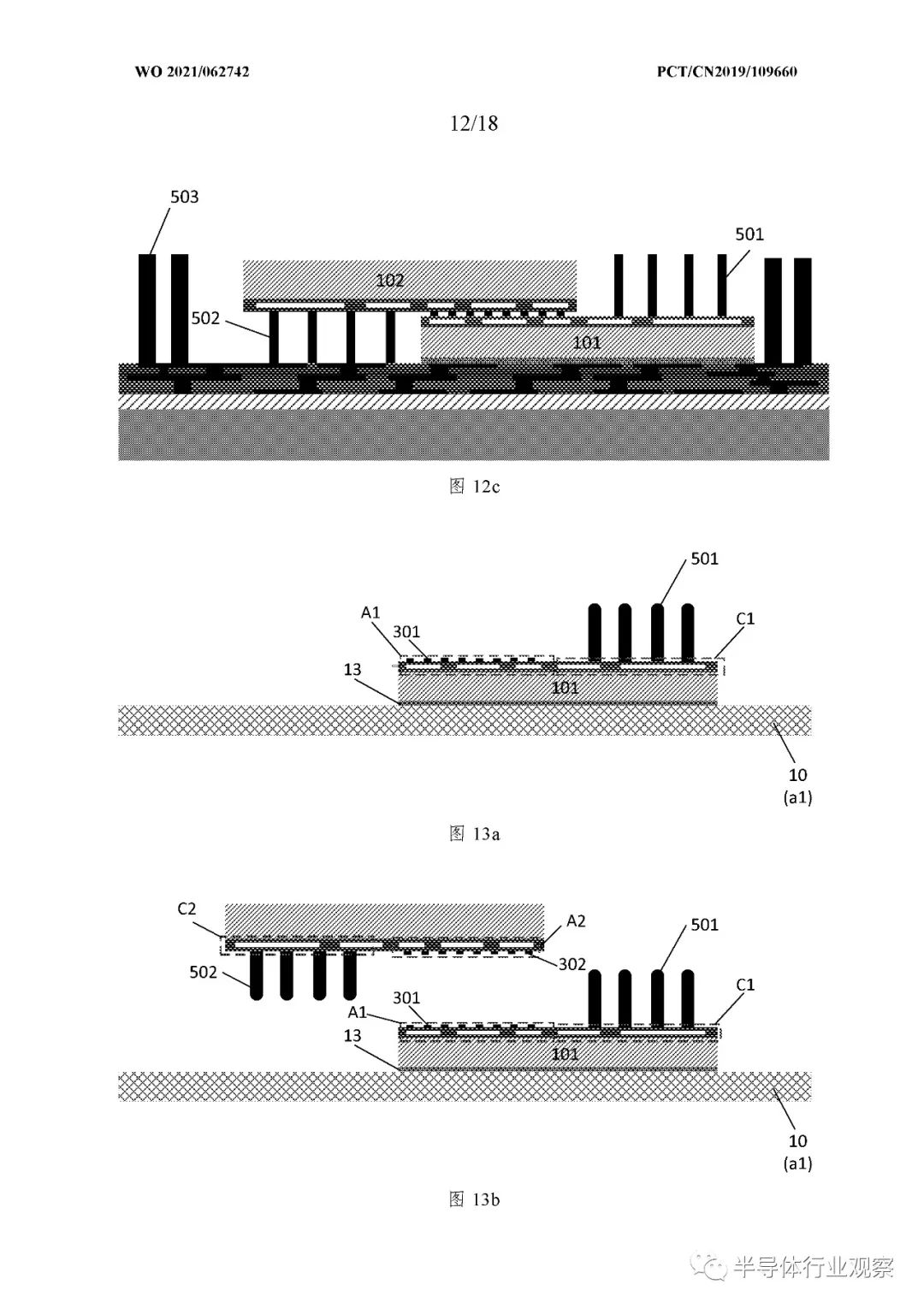

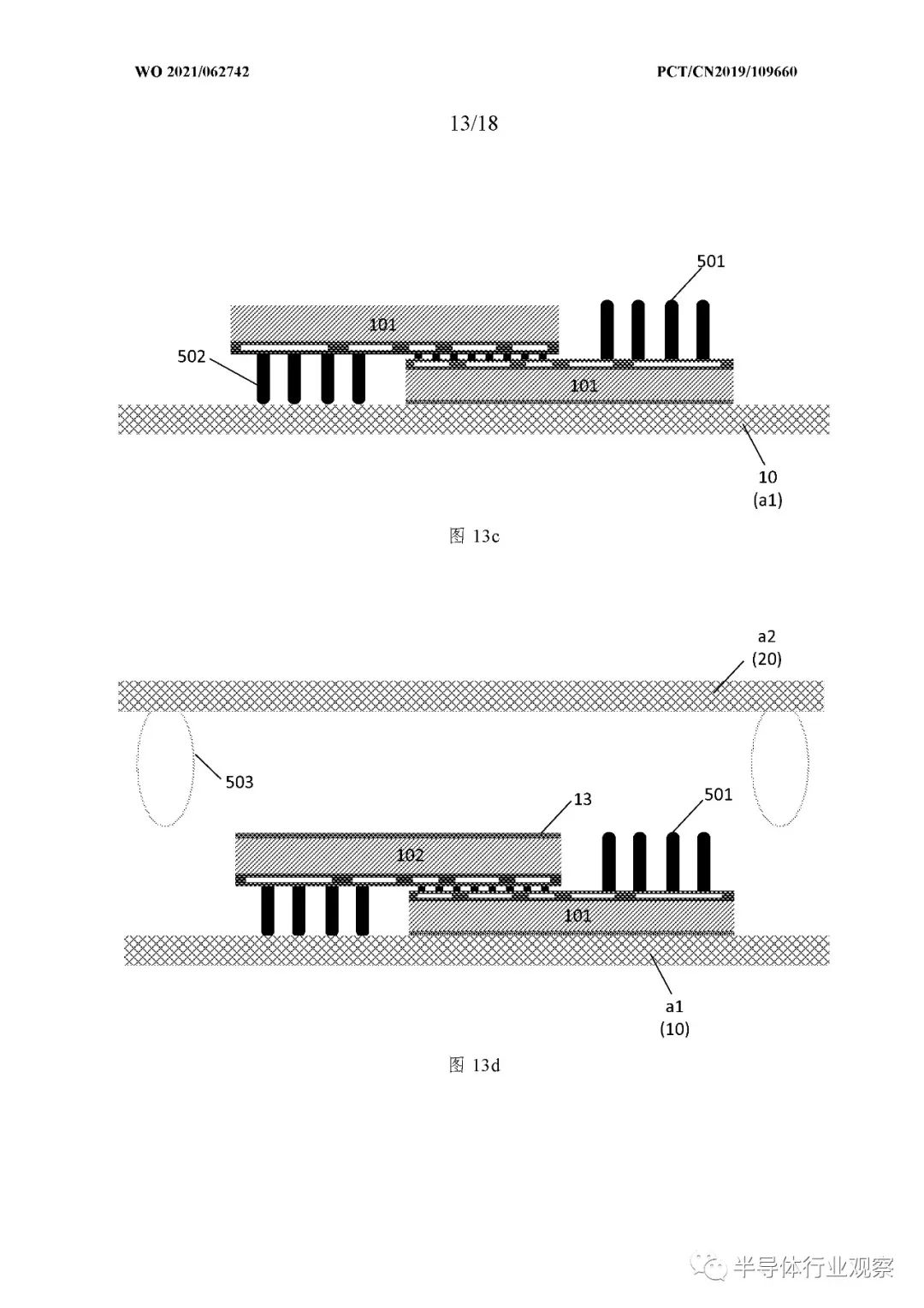

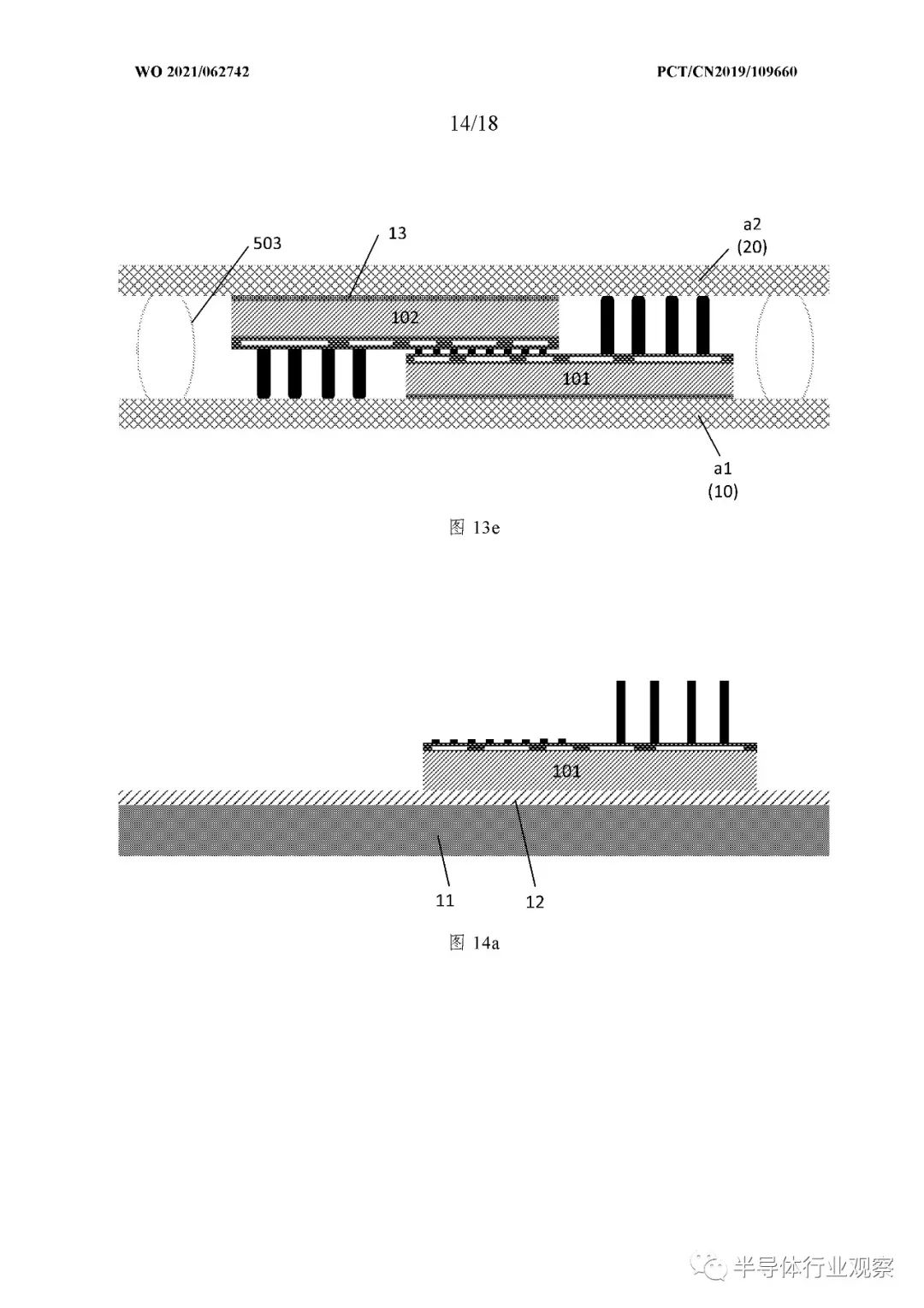

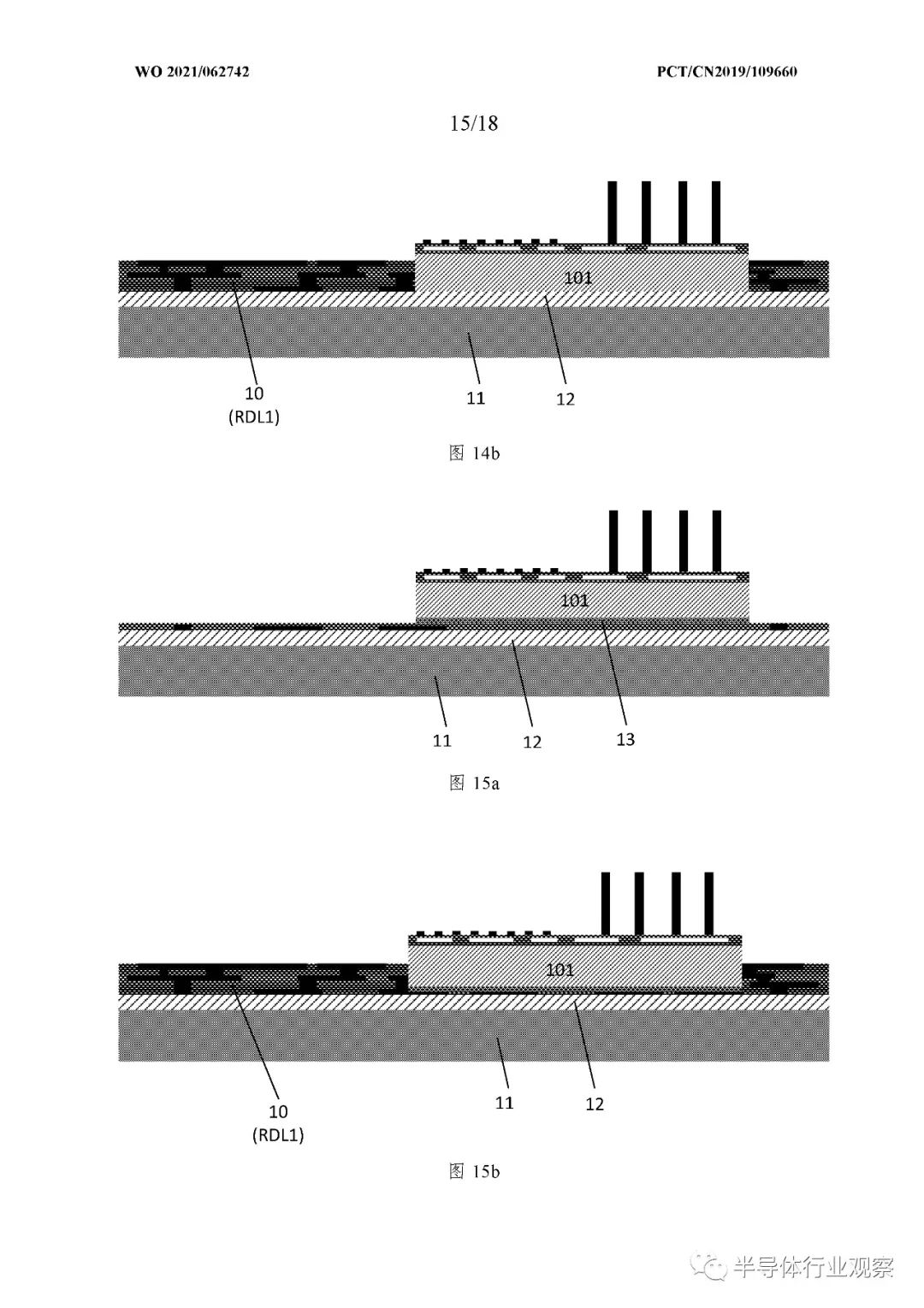

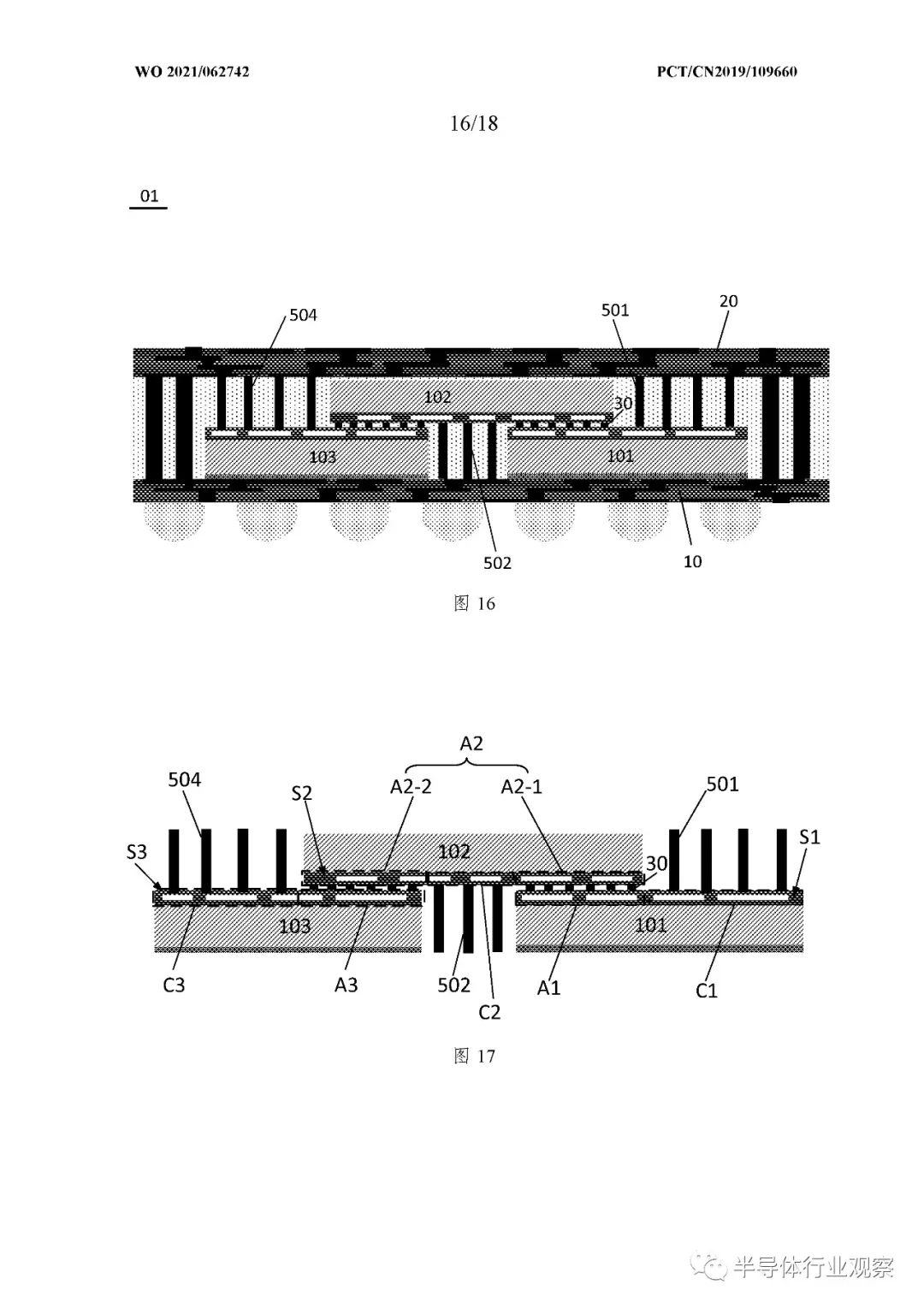

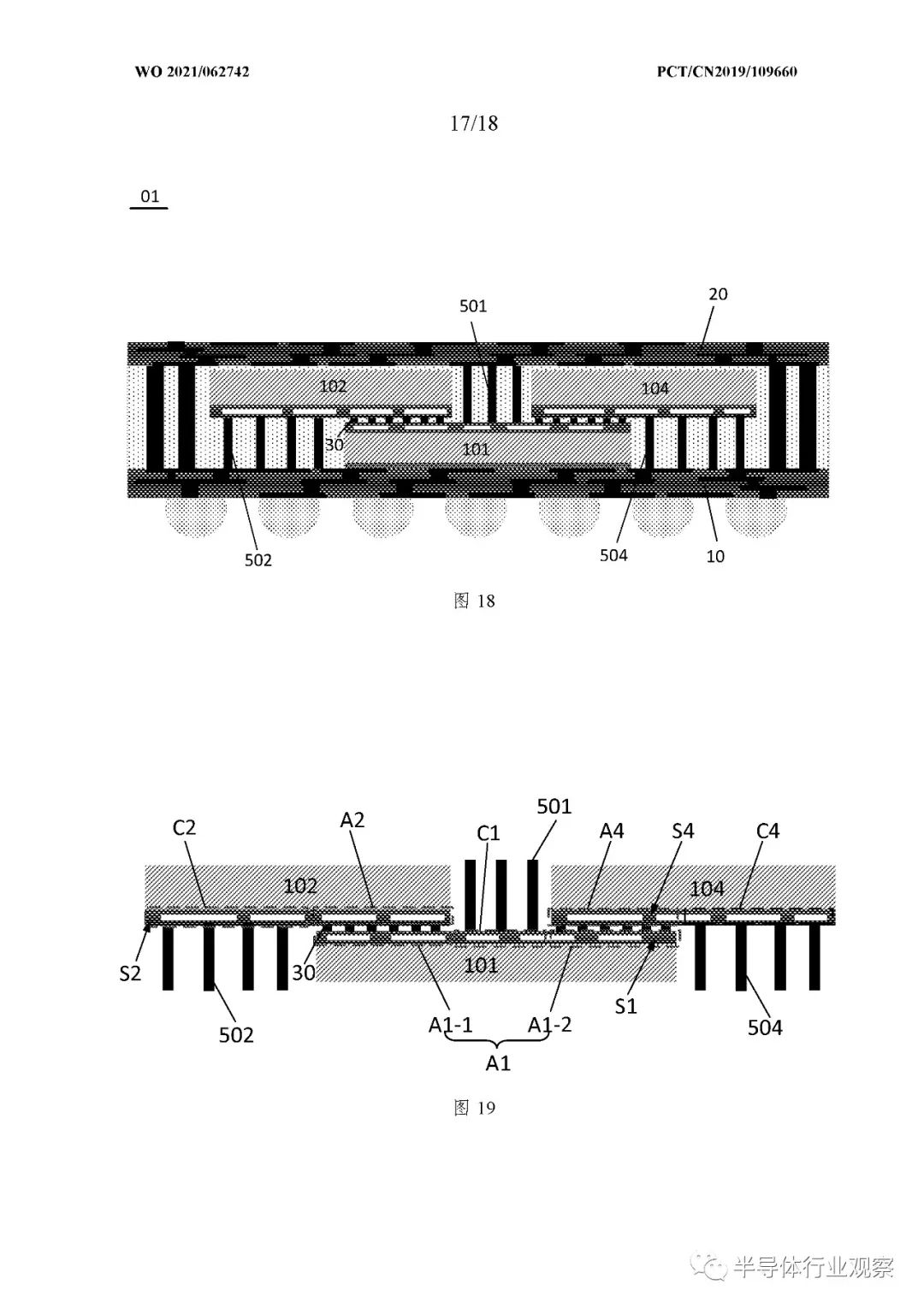

芯片制造商通常使用两种封装和互连方法:2.5D 封装为彼此相邻的小芯片实现高密度/高带宽的封装内互连,3D 封装通过将不同的小芯片堆叠在一起使处理器更小. 然而,3D 封装通常需要相当复杂的布线,因为小芯片需要通信并且必须使用 TSV 提供电力。 虽然 TSV 已在芯片制造中使用了十多年,但它们增加了封装过程的复杂性和成本,因此华为决定发明一种不使用 TSV 的替代解决方案。华为专家设计的本质上是 2.5D 和 3D 堆叠的混合体,因为两个小芯片在封装内相互重叠,节省空间,但不像经典 3D 封装那样完全叠放。

重叠的 3D 堆叠

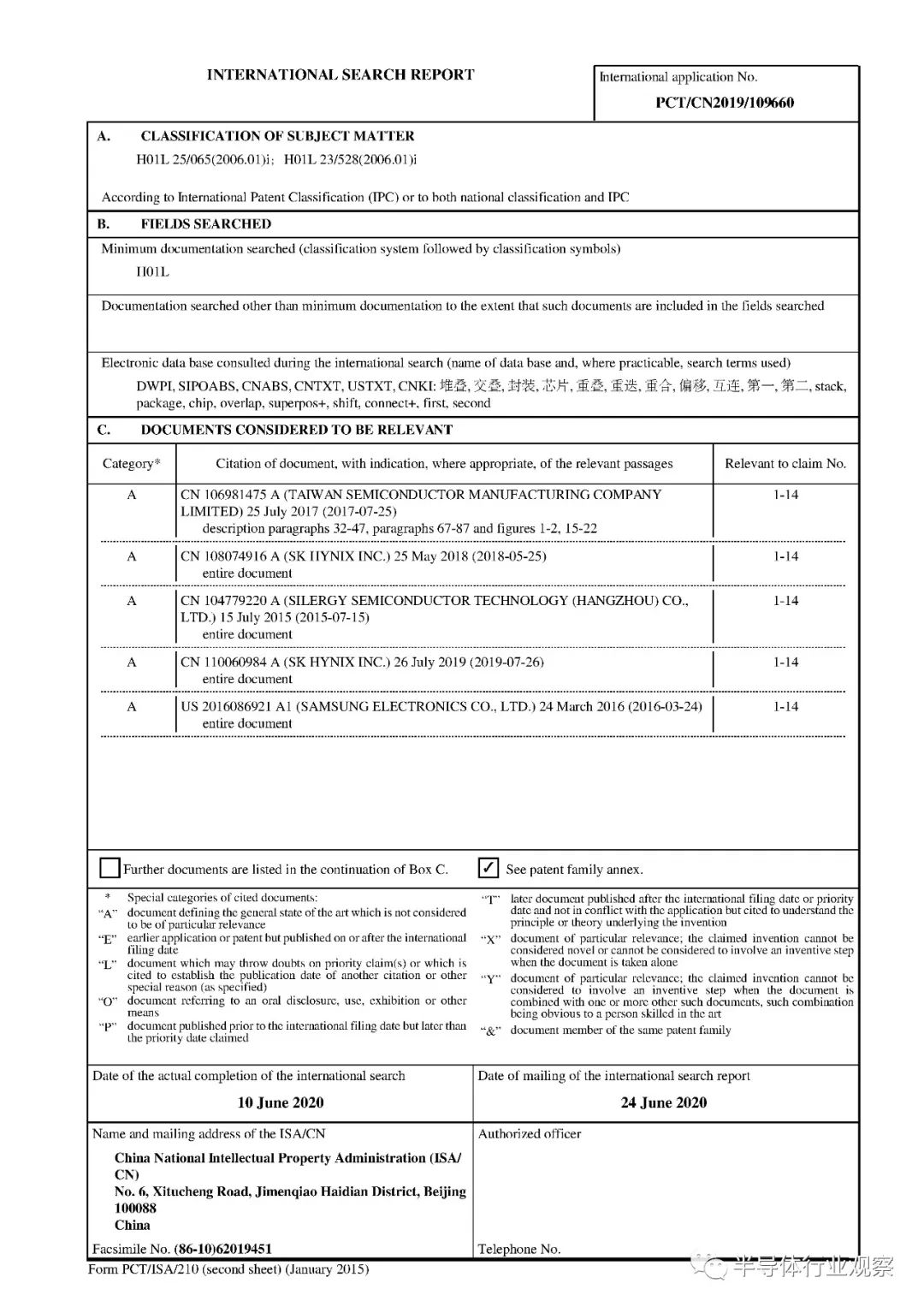

华为的方法使用小芯片的重叠部分来建立逻辑互连。同时,两个或更多小芯片仍然有自己的电力传输引脚,使用各种方法连接到自己的再分配层 (RDL)。但是,虽然华为的专利技术避免使用 TSV,但实施起来并不容易且便宜。

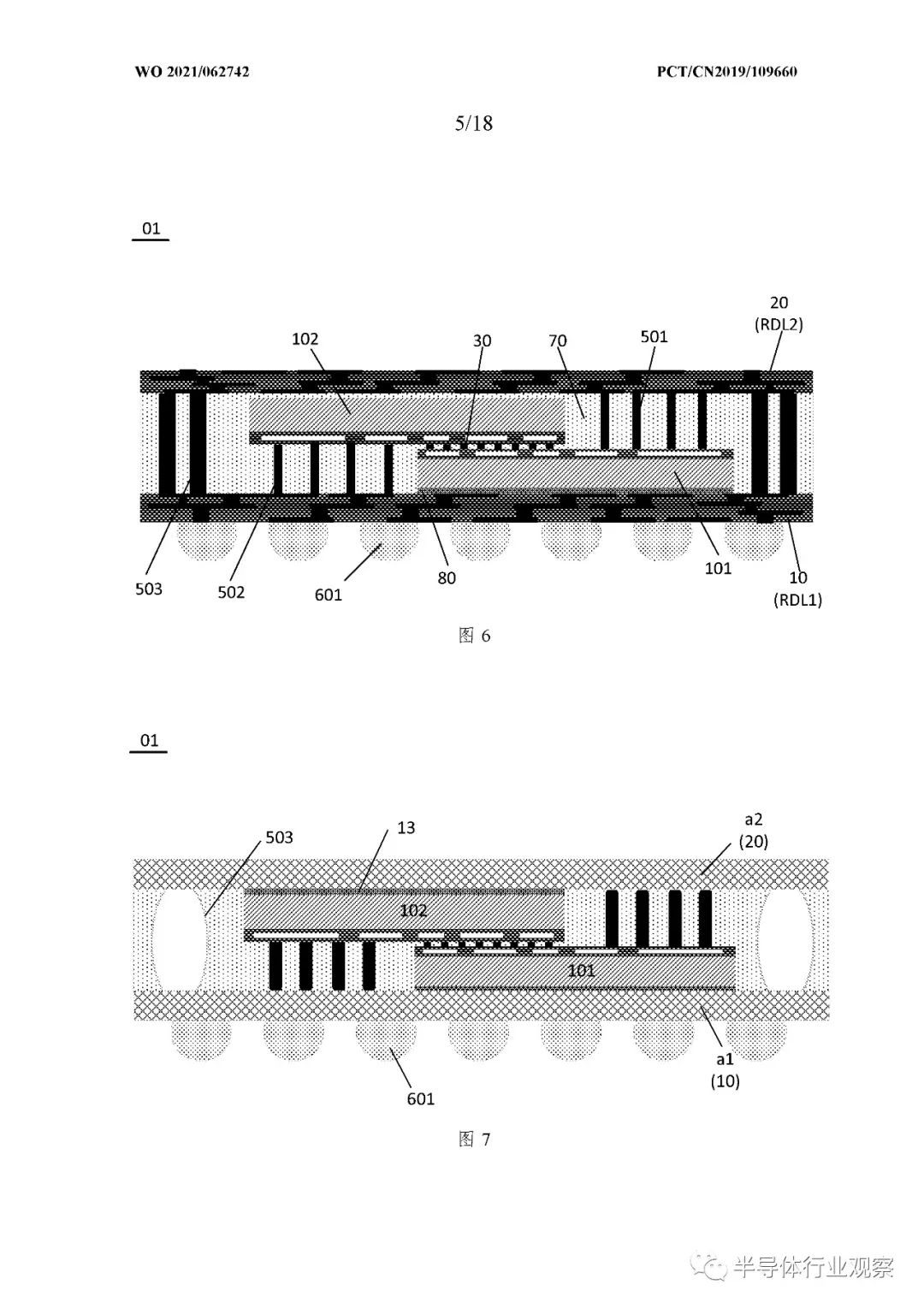

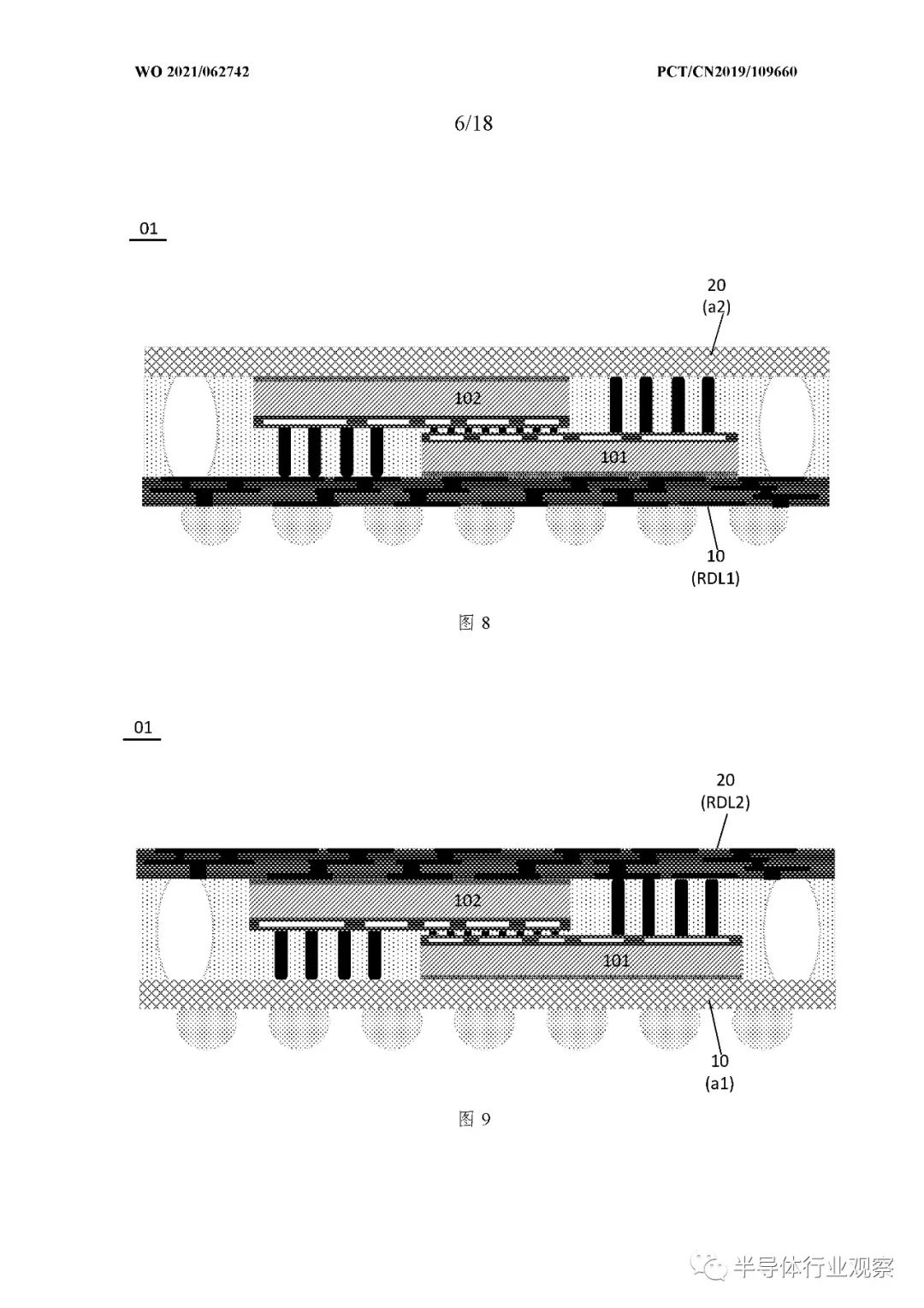

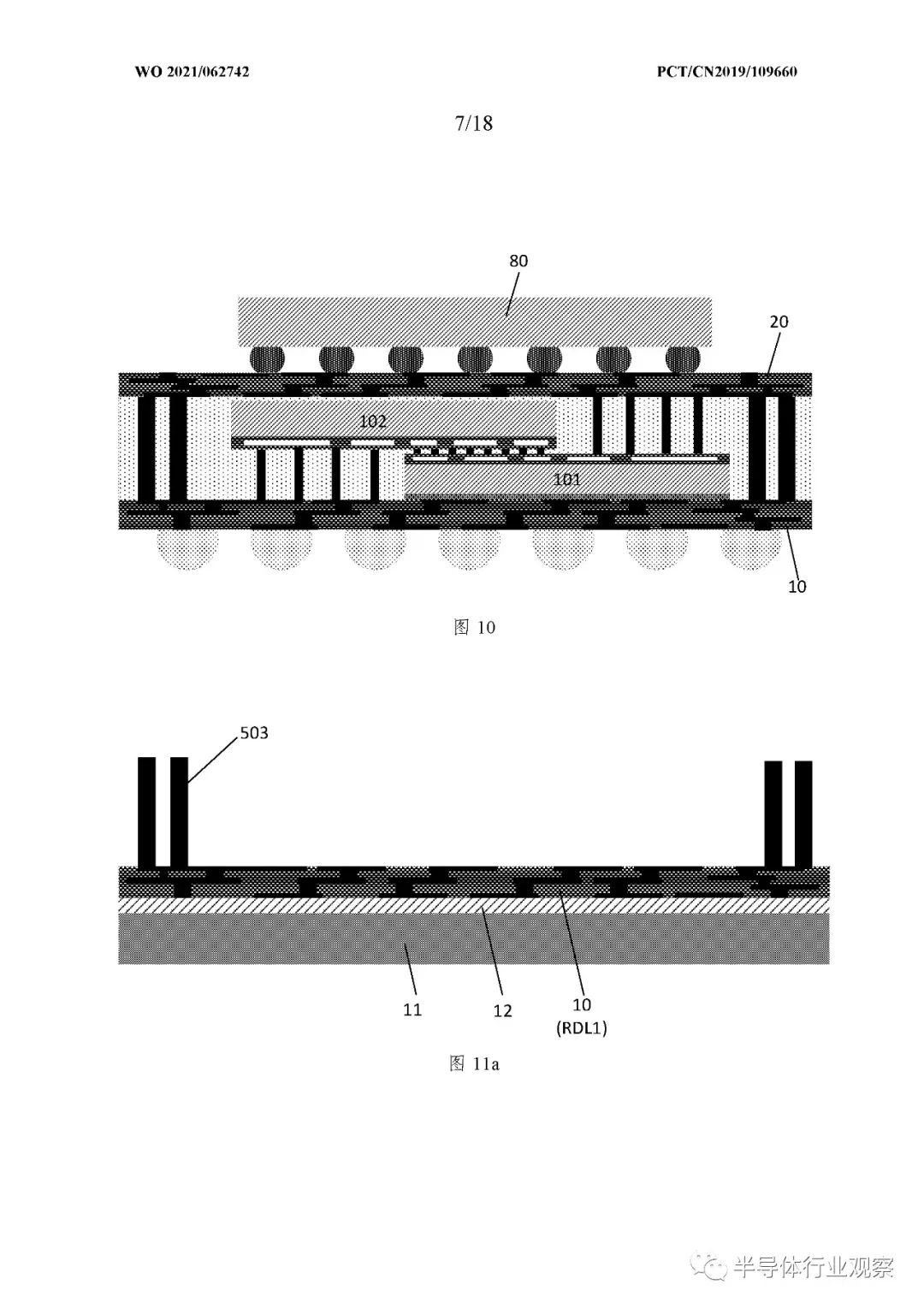

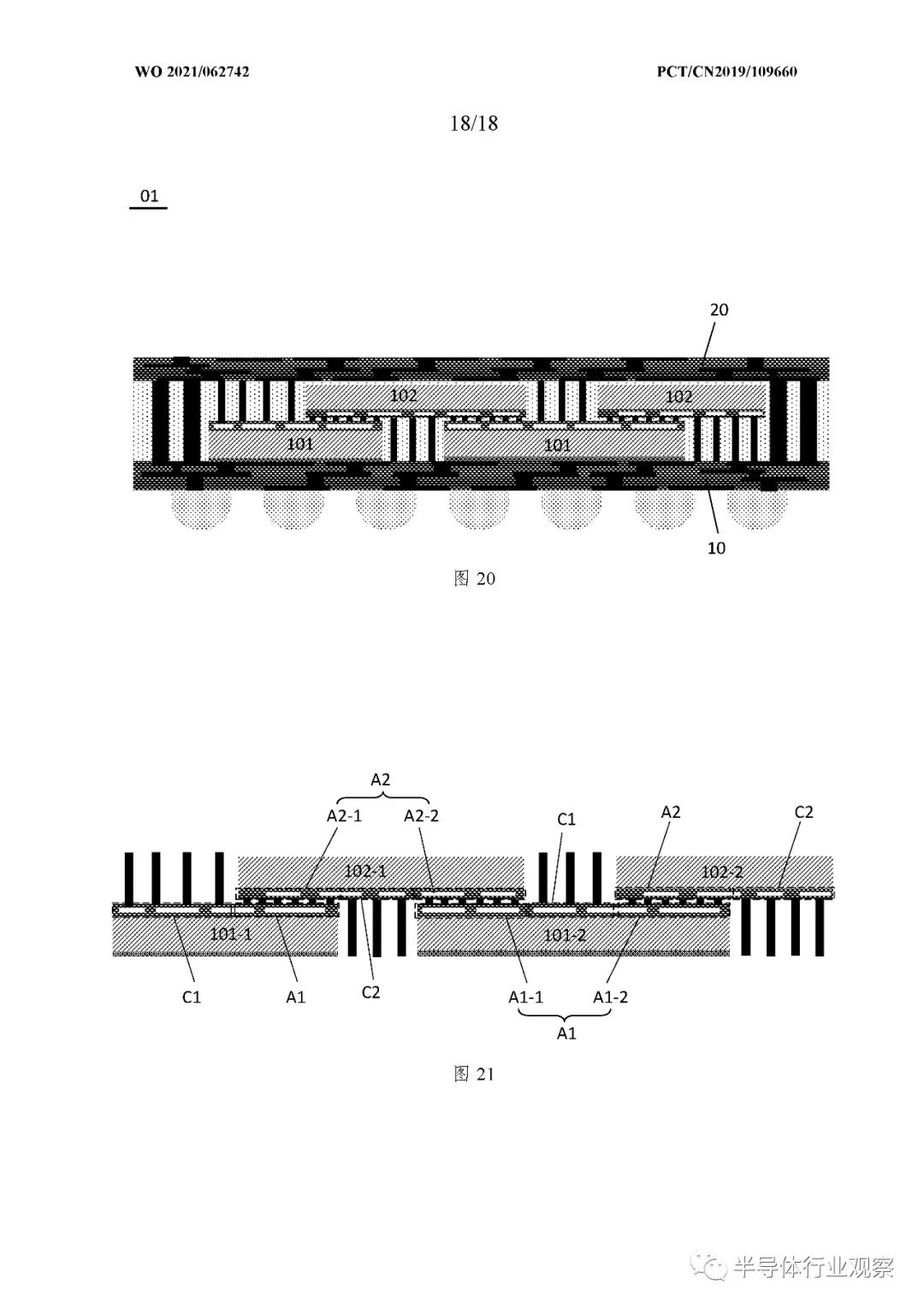

(图片来源:华为) 华为的流程涉及在连接到另一个(或其他)之前将其中一个小芯片倒置。它还需要构建至少两个重新分配层来提供电力(例如,两个小芯片意味着两个 RDL,三个小芯片仍然可以使用两个 RDL,所以四个,请参阅文章末尾的专利文档以了解详细信息),这并不是特别便宜,因为它增加了几个额外的工艺步骤。好消息是其中一个芯片的再分配层可以用来连接内存等东西,从而节省空间。

事实上,华为的混合 3D 堆叠方式可以说比其他公司传统的 2.5D 和 3D 封装技术更通用。例如,很难将两个或三个耗电且热的逻辑裸片堆叠在一起,因为冷却这样的堆栈将非常复杂(这最终可能意味着对时钟和性能的妥协)。华为的方法增加了堆栈的表面尺寸,从而简化了冷却。同时,堆栈仍然小于 2.5D 封装,这对于智能手机、笔记本电脑或平板电脑等移动应用程序很重要。 从产业来看,其他半导体合同制造商(台积电、GlobalFoundries)、集成设计制造商(英特尔、三星),甚至可以使用领先的晶圆厂工具和工艺技术的无晶圆厂芯片开发商(AMD)也开发了自己的 2.5D 和 3D 小芯片堆叠和互连方法为他们的客户或他们未来的产品提供服务。因此,华为只是顺势而为。

审核编辑 :李倩

-

处理器

+关注

关注

68文章

20332浏览量

255011 -

华为

+关注

关注

218文章

36190浏览量

262694 -

3D芯片

+关注

关注

0文章

52浏览量

19090

原文标题:华为3D芯片堆叠专利解读

文章出处:【微信号:ZHISHIKU-Pro,微信公众号:知识酷Pro】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

IDT产品工艺变更通知解读

ON Semiconductor 产品工艺变更通知解读

安森美半导体产品/工艺变更通知解读

Atmel产品胶带和卷轴标签工艺变更通知解读

从3D堆叠到二维材料:2026年芯片技术全面突破物理极限

SK海力士HBS存储技术,基于垂直导线扇出VFO封装工艺

【「AI芯片:科技探索与AGI愿景」阅读体验】+半导体芯片产业的前沿技术

一种基于红外吸收光谱技术的免校准气体传感芯片

NVIDIA B30芯片的核心解读

芯片晶圆堆叠过程中的边缘缺陷修整

华为一种芯片堆叠工艺解读

华为一种芯片堆叠工艺解读

评论