前言

为什么每次都将时钟和复位单独拿出来讲?

对于我们使用Xilinx或其他的成熟IP而言,IP相当于一个黑匣子,内部实现的逻辑功能我们知道,但是控制不了,只能默认OK;一般而言,成熟IP都是经过反复验证和使用,确实没有什么问题。所以,IP能不能用,首先要做的就是确保时钟和复位。

如果初始化不成功,我们也只能从这两个方面入手检查。

一、Aurora核的时钟

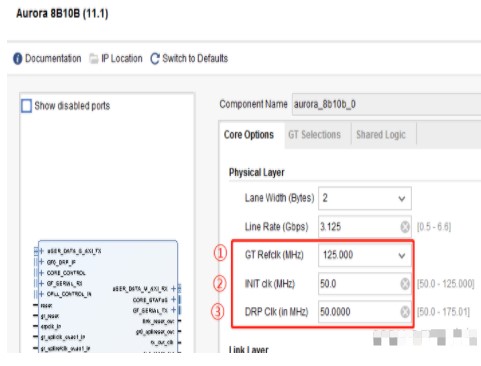

打开Aurora配置界面,我们可以看到有三个时钟:

参考时钟、init clock、DRP CLOCK,如下图所示:

对应到代码:

input INIT_CLK_P;

input INIT_CLK_N;

input DRP_CLK_IN;

input GTXQ0_P;

input GTXQ0_N;

1. GT Refclk : 上一篇我们介绍过,Aurora其实是基于GT作为物理层实现的,这个参考时钟就是GT的参考时钟,可以翻笔者之前介绍GTX时钟博文详细了解。由外部一对差分输入时钟而来,具体根据硬件而定。默认值:125Mhz。

2. INIT CLK :初始化时钟,之所以要INIT CLK,是因为在GT复位时,user_clk是停止工作的;Xilinx推荐的配置是INIT CLK时钟频率要低于GT参考时钟。另外,笔者在查看example design的时候,发现GT复位是工作在INIT CLK。默认值:50Mhz。

3. DRP CLK : DRP时钟,动态重配置,感觉没怎么用到,默认值:50Mhz。对于UltraScale器件而言,DRP CLK与INIT CLK相连接。

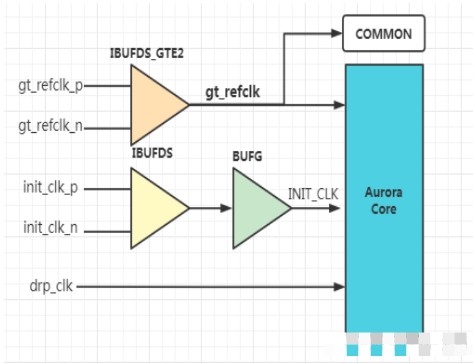

我们再打开example design,看看这几个时钟跟Aurora核是怎么连接的:

注意到没,差分时钟转为单端时钟,这里用了两个原语:IBUFDS_GTE2是GT专用;IBUFDS则是一般情况使用。

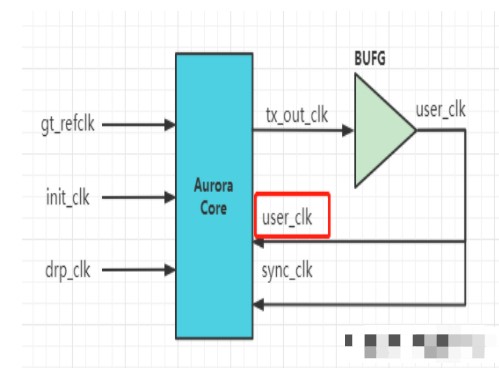

那么,用户逻辑时钟又是多少呢?继续上图:

user_clk, 即是用户逻辑时钟,我们设计的用户接口信号(AXI4-S接口)就是工作在该时钟域。

而tx_out_clk,其实就是GTX里所讲的gt_txoutclk。

这里一顿分析,只为了我们更好的了解Aurora核。如果只是使用,我们只需要按照IP配置界面选定的时钟频率给过去就好。

需要注意的是,参考时钟必须由专用GT差分输入时钟得到,而INIT_CLK和DRP_CLK可以由PLL输出。

二、复位设计

先来看下《PG046》文档对复位的描述:

复位信号是用来将 Aurora 8B/10B core置为一个已知的开始状态。在复位时,核停止当前所有操作然后重新初始化一个新的channel。

channel:两个Aurora所建立的链路,可以有多条lane,每条lane对应一个高速收发器GT,统称为channel。

在全双工模式下,复位信号对channel的TX和RX都进行复位。

在单工模式下,tx_system_reset复位TX链路,rx_system_reset复位RX链路。

而gt_reset则是复位高速收发器GT,最终也会复位Aurora核。(这说明GT复位更加底层,只要GT复位,就会对核进行复位,后面代码也会证实这一点)

再来看两个case:

CASE 1:全双工配置下的系统复位

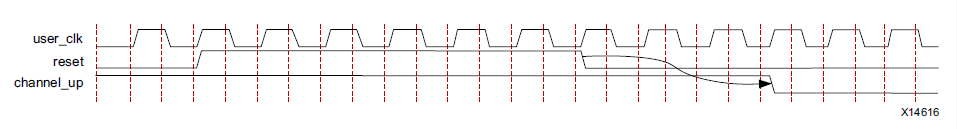

在全双工配置模式下,复位信号应至少保持6个时钟周期(user_clk)。channel_up在3个时钟周期(user_clk)后拉低,如下图所示:

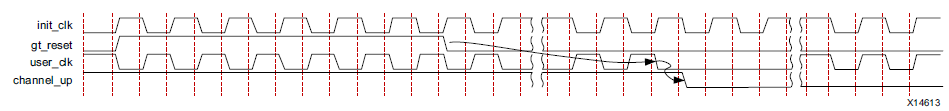

CASE2:全双工配置下的GT复位

在全双工配置模式下,GT复位信号应至少保持6个时钟周期(init_clk)。复位的结果user_clk会在几个时钟周期后停止,因为没有了来自GT的txoutclk。随后,channel_up也会跟着拉低。跟前文讲述一致。如下图所示:

其他的就不再展开了,感兴趣的可以详细查阅《PG046》。

我们再从代码的角度来看看复位:

Aurora复位信号有两个,一个是系统复位RESET,一个是GT复位GT_RESET;复位逻辑就如同前文描述,具体到代码,感兴趣的可以查阅示例工程的reset_logic.v;这里直接给出结论:

1. GT复位更加底层,优先级要高于系统复位RESET;也就是说,若GT复位,那么系统复位也拉高;《PG046》对复位的描述也是如此。

2. 当GT复位没有拉高时,根据输入的系统复位RESET,使用移位寄存器对其打拍,输出复位。

3. GT复位同步于INIT_CLK,所以先将其同步到user_clk时钟域,再对Aurora进行复位。

最后,Xilinx大佬操作来了!

①channel_up : 只要channel_up信号为高,那么说明核初始化完成,且建立了channel,在channel_up拉高之前,lane_up会拉高。我们逻辑设计可以直接使用该信号,在初始化完成之后,再进行逻辑操作。

②debug流程:具体查看P.105

后记

现在FPGA都集成了高速收发器硬核,各种协议的高速接口都是基于GT物理层来实现的。所以,在学习这些高速接口IP之前,最好先熟悉GT。后面就会发现很多东西都是通的。

审核编辑:汤梓红

-

Xilinx

+关注

关注

73文章

2206浏览量

131865 -

时钟

+关注

关注

11文章

1999浏览量

135228 -

复位

+关注

关注

0文章

179浏览量

25091

发布评论请先 登录

Xilinx FPGA中的混合模式时钟管理器MMCME2_ADV详解

RDMA设计52:构建RoCE v2 高速数据传输系统板级测试平台

无惧IP地址配置错误|FCU1501工业数据网关复位键高效兜底

Xilinx FPGA中IDELAYCTRL参考时钟控制模块的使用

使用Aurora 6466b协议实现AMD UltraScale+ FPGA与AMD Versal自适应SoC的对接

Xilinx FPGA串行通信协议介绍

E203移植genesys2(差分时钟板)生成比特流文件全过程

Aurora接口的核心特点和应用场景

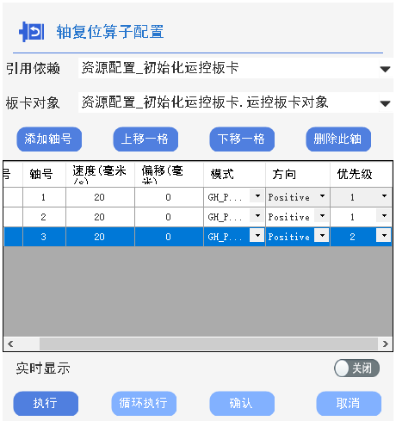

GraniStudio零代码平台轴复位算子支持多少个轴同时复位,有哪些回零模式?

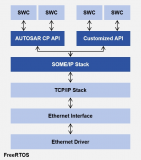

光庭信息SOME/IP平台融合解决方案介绍

Xilinx Shift RAM IP概述和主要功能

智多晶FIFO_Generator IP介绍

Xilinx平台Aurora IP介绍(二)时钟与复位

Xilinx平台Aurora IP介绍(二)时钟与复位

评论