采用SystemVerilog进行仿真则更容易生成随机数,而且对随机数具有更强的可控性。对于随机变量,在SystemVerilog中可通过rand或randc加数据类型的方式定义。rand表明该变量为随机变量,且在指定范围内服从均匀分布;randc是在rand的基础上要求当生成的随机数已经在指定范围内完成一次遍历之后,将重复遍历,c为cyclic(循环)。声明随机变量后,需要通过constraint限定随机数需要满足的条件。这些都需要在class中声明。

案例1:用小于号《 大于号 》 小于等于号 《= 大于等于号》=创建限定条件

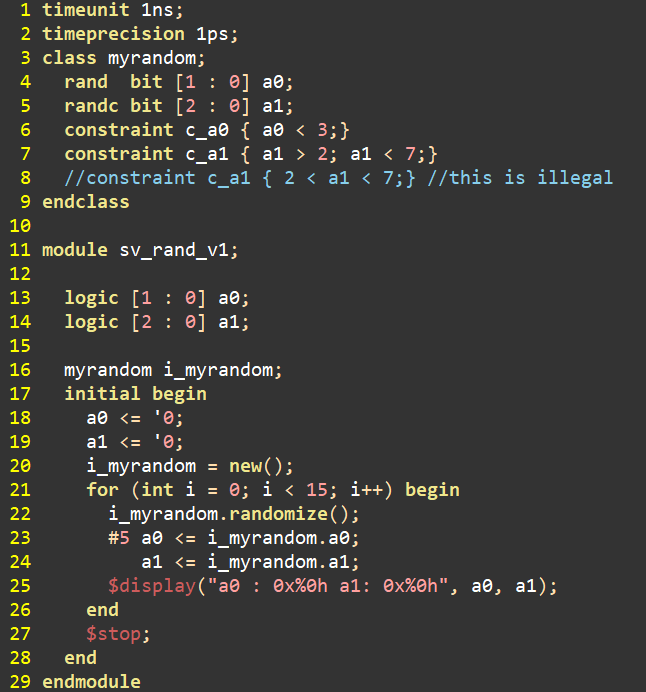

代码如下图所示。代码第6行限定了a0必须小于3,第7行限定了a1必须大于2且小于7。注意,这4个关系运算符不能连写,如代码第8行是不合法的。代码第16行对class实例化,代码第20行为class对象分配内存空间并完成class对象的初始化。代码第22行用于判定随机数是否成功生成,若成功则返回1,否则返回0。

编辑:jq

-

仿真

+关注

关注

53文章

4404浏览量

137644 -

Verilog

+关注

关注

30文章

1370浏览量

114106 -

System

+关注

关注

0文章

166浏览量

38444 -

代码

+关注

关注

30文章

4940浏览量

73116

原文标题:SystemVerilog仿真如何生成随机数

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于RNG90的真随机数生成器技术解析与应用指南

凌科芯安LCSHA204安全加密芯片介绍

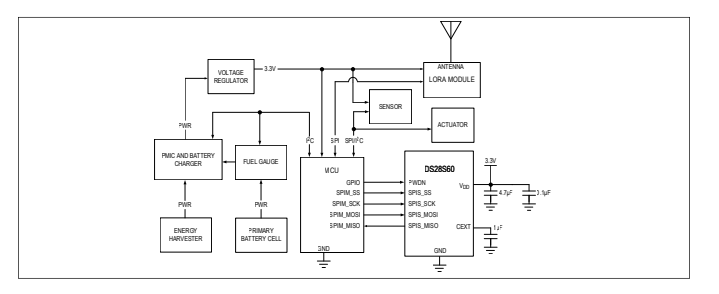

DS28S60具有ChipDNA的DeepCover加密协处理器技术手册

labview求助:想写一个labview输出不重复随机数的程序,有没有大佬帮忙看看这个假分支要怎么写?

“Quantum Origin”成首个获NIST验证的软件量子随机数生成器

开源随机数生成器库OpenRNG助力实现移植到Arm平台时的最佳性能

如何利用SystemVerilog仿真生成随机数

如何利用SystemVerilog仿真生成随机数

评论