自去年起,台积电和三星等晶圆代工厂纷纷推出了5nm的工艺,如今更是在钻研5nm以下的先进制程。但制程的提升不单单只靠EUV光刻机就能轻易实现的,短沟道效应使得传统的FinFET技术已经满足不了更高的半导体工艺。

目前的工艺水平在深度学习、图形分析等基础AI应用上已经可以满足要求,但在神经形态芯片和量子计算上,仍需要更先进的制程来提供支持。面对这些挑战,三星、台积电和英特尔纷纷选择了GAA技术来突破这一壁障。

GAA何时面世?

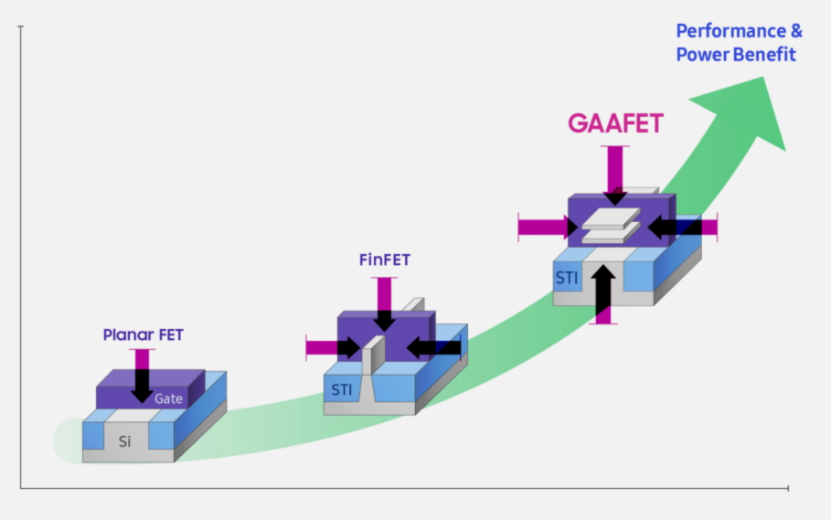

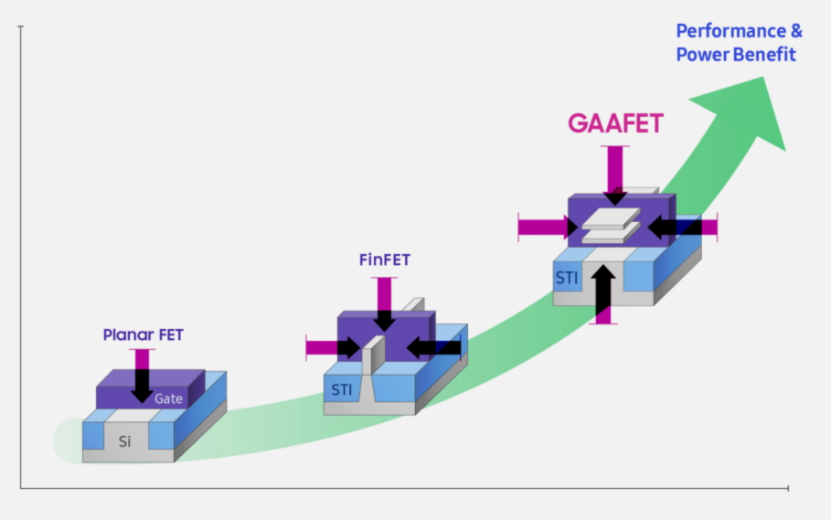

晶体管结构的演进 / 三星

三星在2019年就公布了其GAA 技术MBCFET,并发布了初版PDK。GAA结构进一步提到了栅极与沟道之间的接触面积,并支持垂直堆叠的方式来获得更强的载流能力,而非像FinFET一样横向堆叠鳍片。三星也同时宣布,将在3nm工艺节点引入GAA技术。根据三星给出的PPA数据,先进节点的MBCFET与7nm的FinFET相比,功耗减少50%,性能提升30%,面积减小了50%。

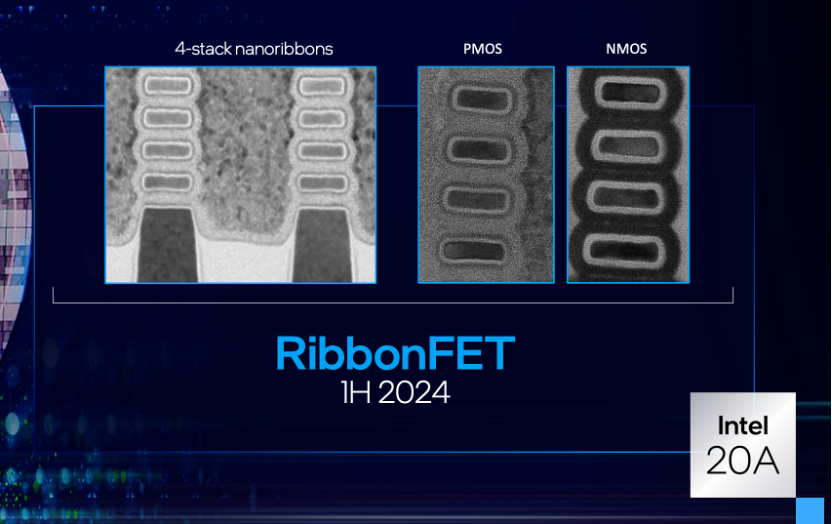

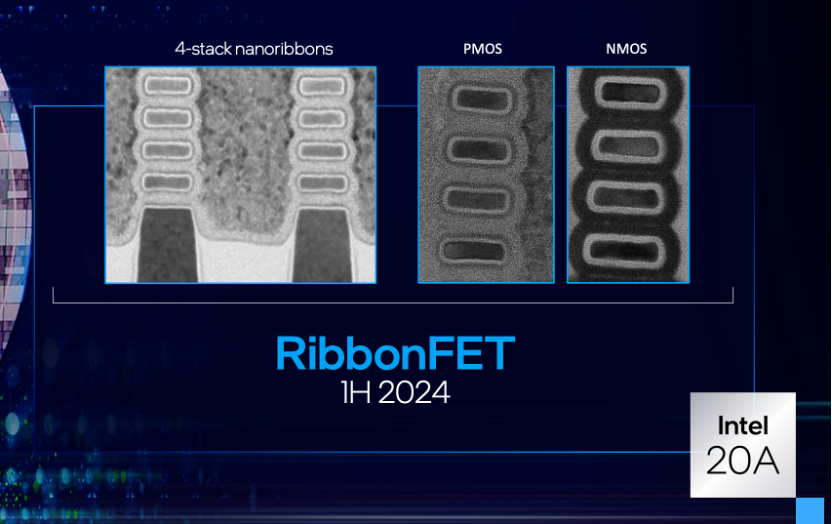

堆叠四层纳米带的RibbonFET / 英特尔

IBM全球首发的2nm芯片上,也用到了纳米片GAA技术。今年6月底,三星宣布与新思合作的3nm GAA试产芯片已经成功流片。根据目前的消息来看,预计三星会在2022年推出早期GAA技术的制程3GAE,在2023年推出基于MBCFET的3GAP。英特尔也在近期的Intel Accelerated发布会中宣布,将在其20A工艺节点中引入其GAA技术RibbonFET,预计2024年上半年推出。而台积电则在今年的技术论坛上宣布,FinFET技术只会用到3nm,2nm将用纳米片晶体管来取代现有结构。

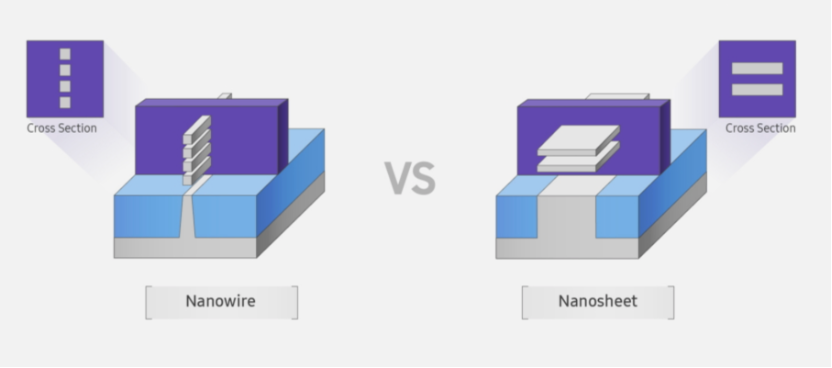

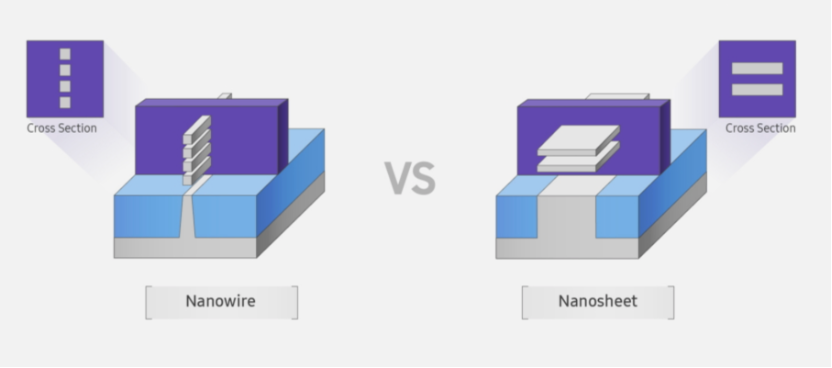

然而令许多人不解的是,GAA中通道的命名有纳米线、纳米片和纳米带,这些究竟是营销术语不同,还是另有玄机呢?

纳米线、纳米带与纳米片

其实这些并不是花哨的营销术语,而是对通道物理特质不同的描述。纳米线的宽度和通道厚度基本相近,而纳米片则选择了更大的宽度,纳米带则是一个折中的方案,也可以看做是宽度更小的纳米片。那么不同的通道对其性能又有何影响呢?由于2D结构约束所带来优秀的短沟道特性,纳米线在低功率应用上的表现更好。而纳米片因为更大有效宽度实现了更大的接触面积,载流性能要更为优异,适合一些高性能的应用,

纳米线与纳米片的截面对比 / 三星

虽然通道有所差异,但三星等厂商都不约而同的采用了堆叠通道的方式来继续增加GAA结构的载流性能。不过FinFET中的鳍并不能无限叠加,GAA中的通道也是如此。这种载流能力的提升速度会随着源极/漏极外延处的寄生电阻而减慢,不仅如此,栅极电容也会随着通道数的增加而增大,因此为了保证最小的RC延迟,GAA一般会选择3或4的通道数。

2nm及之后的晶体管结构

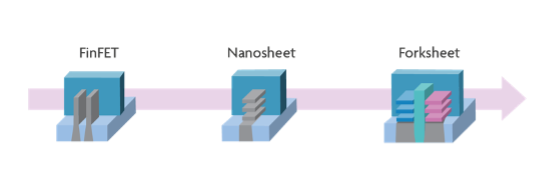

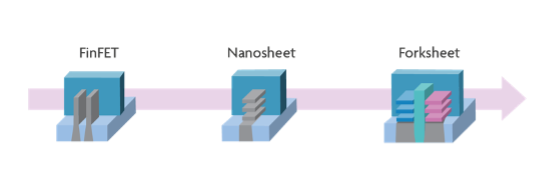

分叉片结构 / IMEC

至于2nm及之后的晶体管结构,比利时微电子研究中心(IMEC)提出了一种新的替代结构,名为分叉片(Forksheet)。该结构中,这些纳米片由分叉式的栅极结构来控制,这种结构在栅极图案化之前,为pMOS和nMOS之间引入了一个绝缘强,将p栅极沟道和n栅极沟道隔绝开来,提供了比FinFET和纳米片都要窄的np间距。由此,分叉片可以提供更好的面积和性能扩展能力,并将单元高度从5T减小至4.3T,也实现了更低的寄生电容。

FinFET、纳米片、CFET单元高度对比 / IMEC

为了挺进1nm这一制程,单元高度的要求也减小至了3T,但由于布通率的限制,即便是分叉片也无法满足这一条件。因此,IMEC又推出了名为CFET的技术,一种互补的FET。CFET的概念就是将nFET叠在pFET上,从而提供了更多内部单元布线的自由,并减小了单元面积。在IMEC的初步评估中,运用CFET技术的4T FinFET在功耗和性能的表现上,可以打平甚至超过5T的标准FinFET,而且占用面积还要小25%。至于运用了CFET的纳米片晶体管,不仅逻辑单元高度可以做到3T,还能提供额外的性能提升。

结语

就像平面晶体管自然演进至FinFET一样,FinFET也将让位给GAAFET。CMOS器件在结构上演化的过程,也是半导体不断挑战摩尔定律的过程。除此之外,其实也有不少公司正在探索CMOS之外的晶体管方案,试图消除CMOS本身的一些缺点,比如英国公司Search For The Next推出的Bizen。但从现在追求PPA的潮流来看,这些方案还远远不能成为市场主流。2022年之后的半导体市场,高NA的EUV光刻机和GAAFET必将成为5nm制程以下的关键因素。

目前的工艺水平在深度学习、图形分析等基础AI应用上已经可以满足要求,但在神经形态芯片和量子计算上,仍需要更先进的制程来提供支持。面对这些挑战,三星、台积电和英特尔纷纷选择了GAA技术来突破这一壁障。

GAA何时面世?

晶体管结构的演进 / 三星

三星在2019年就公布了其GAA 技术MBCFET,并发布了初版PDK。GAA结构进一步提到了栅极与沟道之间的接触面积,并支持垂直堆叠的方式来获得更强的载流能力,而非像FinFET一样横向堆叠鳍片。三星也同时宣布,将在3nm工艺节点引入GAA技术。根据三星给出的PPA数据,先进节点的MBCFET与7nm的FinFET相比,功耗减少50%,性能提升30%,面积减小了50%。

堆叠四层纳米带的RibbonFET / 英特尔

IBM全球首发的2nm芯片上,也用到了纳米片GAA技术。今年6月底,三星宣布与新思合作的3nm GAA试产芯片已经成功流片。根据目前的消息来看,预计三星会在2022年推出早期GAA技术的制程3GAE,在2023年推出基于MBCFET的3GAP。英特尔也在近期的Intel Accelerated发布会中宣布,将在其20A工艺节点中引入其GAA技术RibbonFET,预计2024年上半年推出。而台积电则在今年的技术论坛上宣布,FinFET技术只会用到3nm,2nm将用纳米片晶体管来取代现有结构。

然而令许多人不解的是,GAA中通道的命名有纳米线、纳米片和纳米带,这些究竟是营销术语不同,还是另有玄机呢?

纳米线、纳米带与纳米片

其实这些并不是花哨的营销术语,而是对通道物理特质不同的描述。纳米线的宽度和通道厚度基本相近,而纳米片则选择了更大的宽度,纳米带则是一个折中的方案,也可以看做是宽度更小的纳米片。那么不同的通道对其性能又有何影响呢?由于2D结构约束所带来优秀的短沟道特性,纳米线在低功率应用上的表现更好。而纳米片因为更大有效宽度实现了更大的接触面积,载流性能要更为优异,适合一些高性能的应用,

纳米线与纳米片的截面对比 / 三星

虽然通道有所差异,但三星等厂商都不约而同的采用了堆叠通道的方式来继续增加GAA结构的载流性能。不过FinFET中的鳍并不能无限叠加,GAA中的通道也是如此。这种载流能力的提升速度会随着源极/漏极外延处的寄生电阻而减慢,不仅如此,栅极电容也会随着通道数的增加而增大,因此为了保证最小的RC延迟,GAA一般会选择3或4的通道数。

2nm及之后的晶体管结构

分叉片结构 / IMEC

至于2nm及之后的晶体管结构,比利时微电子研究中心(IMEC)提出了一种新的替代结构,名为分叉片(Forksheet)。该结构中,这些纳米片由分叉式的栅极结构来控制,这种结构在栅极图案化之前,为pMOS和nMOS之间引入了一个绝缘强,将p栅极沟道和n栅极沟道隔绝开来,提供了比FinFET和纳米片都要窄的np间距。由此,分叉片可以提供更好的面积和性能扩展能力,并将单元高度从5T减小至4.3T,也实现了更低的寄生电容。

FinFET、纳米片、CFET单元高度对比 / IMEC

为了挺进1nm这一制程,单元高度的要求也减小至了3T,但由于布通率的限制,即便是分叉片也无法满足这一条件。因此,IMEC又推出了名为CFET的技术,一种互补的FET。CFET的概念就是将nFET叠在pFET上,从而提供了更多内部单元布线的自由,并减小了单元面积。在IMEC的初步评估中,运用CFET技术的4T FinFET在功耗和性能的表现上,可以打平甚至超过5T的标准FinFET,而且占用面积还要小25%。至于运用了CFET的纳米片晶体管,不仅逻辑单元高度可以做到3T,还能提供额外的性能提升。

结语

就像平面晶体管自然演进至FinFET一样,FinFET也将让位给GAAFET。CMOS器件在结构上演化的过程,也是半导体不断挑战摩尔定律的过程。除此之外,其实也有不少公司正在探索CMOS之外的晶体管方案,试图消除CMOS本身的一些缺点,比如英国公司Search For The Next推出的Bizen。但从现在追求PPA的潮流来看,这些方案还远远不能成为市场主流。2022年之后的半导体市场,高NA的EUV光刻机和GAAFET必将成为5nm制程以下的关键因素。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

三星电子

+关注

关注

34文章

15897浏览量

183243 -

台积电

+关注

关注

44文章

5813浏览量

177111 -

intel

+关注

关注

19文章

3511浏览量

191690 -

晶体管

+关注

关注

78文章

10449浏览量

148733 -

FinFET

+关注

关注

12文章

262浏览量

92384

发布评论请先 登录

相关推荐

热点推荐

芯擎科技“龍鹰二号”:5nm舱驾融合芯片开启智能汽车AI新纪元

2026年4月25日,芯擎科技正式发布其新一代车规级舱驾融合芯片“龍鹰二号”。这款采用5nm先进制程工艺打造的芯片,以200 TOPS的算力峰值和7B大模型支持能力,直指AI舱驾融合市场的核心需求,并计划于2027年第一季度实现

芯擎首发5nm“龍鹰二号”! 200TOPS算力+7B大模型,2027年Q1量产适配

4月25日,芯擎科技发布5nm车规级舱驾融合芯片“龍鹰二号”,龍鹰二号正是为AI舱驾融合而生。该芯片为12核CPU和10核GPU,AI算力高达200 TOPS,内置多核CPU 360K

1600TOPS!美国新势力车企自研5nm芯片,转用激光雷达硬刚特斯拉

的2025 AI Day上,也首次公布了自研自动驾驶大模型,以及自研的5nm定制芯片,同时还明确了激光雷达是其下一代自动驾驶系统的核心传感器之一。 5nm芯片、高速互连、全新神经网

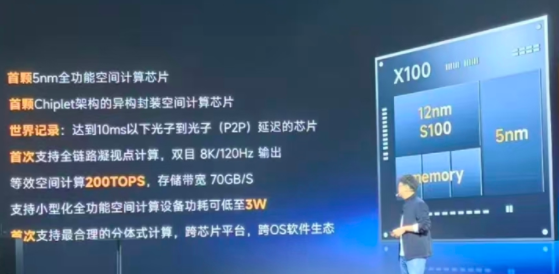

国内首颗5nm MR芯片问世: Chiplet架构、9ms P2P延迟打破纪录

)正式发布三款自主研发的空间计算芯片——极智G-X100、极眸G-VX100与极颜G-EB100。 其中,旗舰产品极智G-X100作为中国首颗5nm制程全功能空间计算MR芯片,填补了国产高端空间计算

国产芯片真的 “稳” 了?这家企业的 14nm 制程,已经悄悄渗透到这些行业…

最近扒了扒国产芯片的进展,发现中芯国际(官网链接:https://www.smics.com)的 14nm FinFET 制程已经不是 “实验室技术” 了 —— 从消费电子的中端处理器,到汽车电子

发表于 11-25 21:03

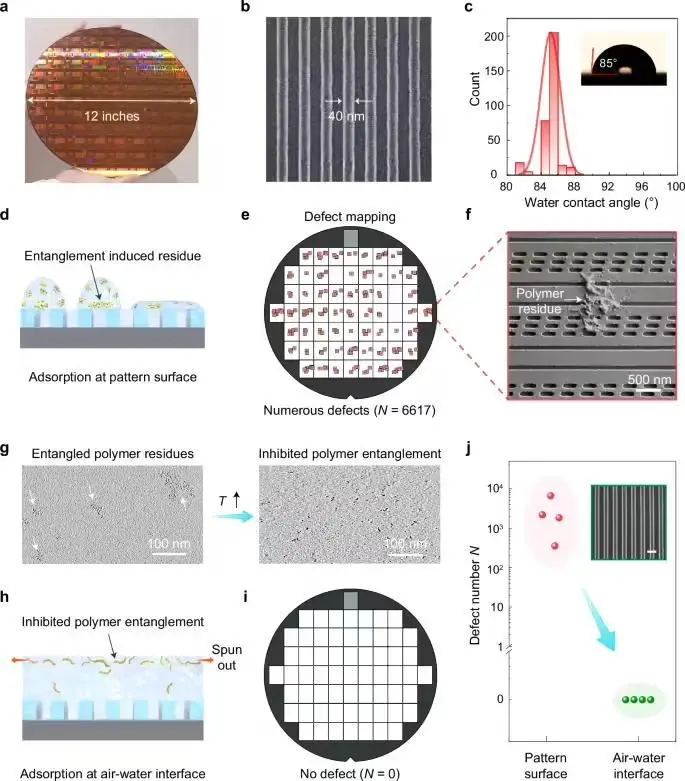

国产光刻胶重磅突破:攻克5nm芯片制造关键难题

分布与缠结行为,成功研发出可显著减少光刻缺陷的产业化方案。相关研究成果已刊发于国际顶级期刊《自然·通讯》,标志着我国在光刻胶关键材料领域取得实质性突破。 此次成果对国产芯片制造而言具有里程碑式意义:团队利用

【「AI芯片:科技探索与AGI愿景」阅读体验】+半导体芯片产业的前沿技术

%。至少将GAA纳米片提升几个工艺节点。

2、晶背供电技术

3、EUV光刻机与其他竞争技术

光刻技术是制造3nm、5nm等工艺节点的高端半导体芯片的关键技术。是将设计好的

发表于 09-15 14:50

【「AI芯片:科技探索与AGI愿景」阅读体验】+工艺创新将继续维持着摩尔神话

。

FinFET是在22nm之后的工艺中使用,而GAA纳米片将会在3nm及下一代工艺中使用。

在叉形片中,先前独立的两个晶体管NFET和PFET被

发表于 09-06 10:37

全球首款2nm芯片被曝准备量产 三星Exynos 2600

据外媒韩国媒体 ETNews 在9 月 2 日发文报道称全球首款2nm芯片被曝准备量产;三星公司已确认 Exynos 2600 将成为全球首款采用 2nm 工艺的移动 SoC

今日看点丨蔚来自研全球首颗车规5nm芯片!;沃尔沃中国区启动裁员计划

1. 蔚来自研全球首颗车规5nm 芯片!将对全行业开放 据了解,李斌在直播中介绍了蔚来自研神玑NX9031芯片,他表示:“这是全球首颗车规5nm的智驾

发表于 07-08 10:50

•2278次阅读

体硅FinFET和SOI FinFET的差异

在半导体制造领域,晶体管结构的选择如同建筑中的地基设计,直接决定了芯片的性能上限与能效边界。当制程节点推进到22nm以下时,传统平面晶体管已无法满足需求,鳍式场效应晶体管(FinFET

下一代高速芯片晶体管解制造问题解决了!

在半导体工艺演进到2nm,1nm甚至0.7nm等节点以后,晶体管结构该如何演进?2017年,imec推出了叉片晶体管(forksheet),作为环栅(GAA)晶体管的自然延伸。不过,产

发表于 06-20 10:40

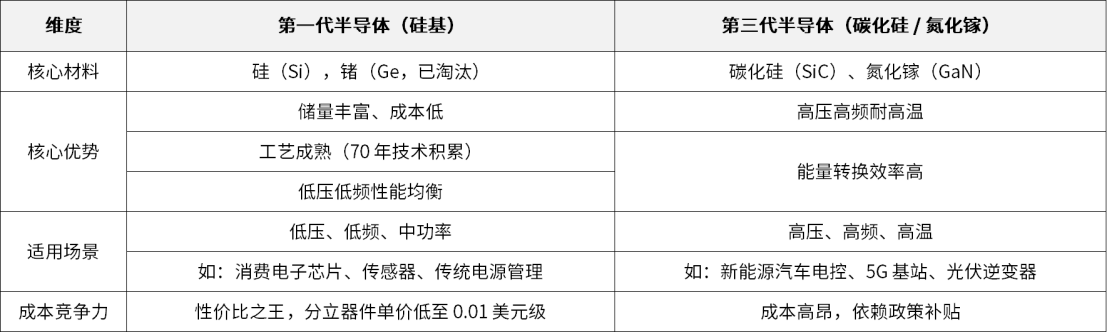

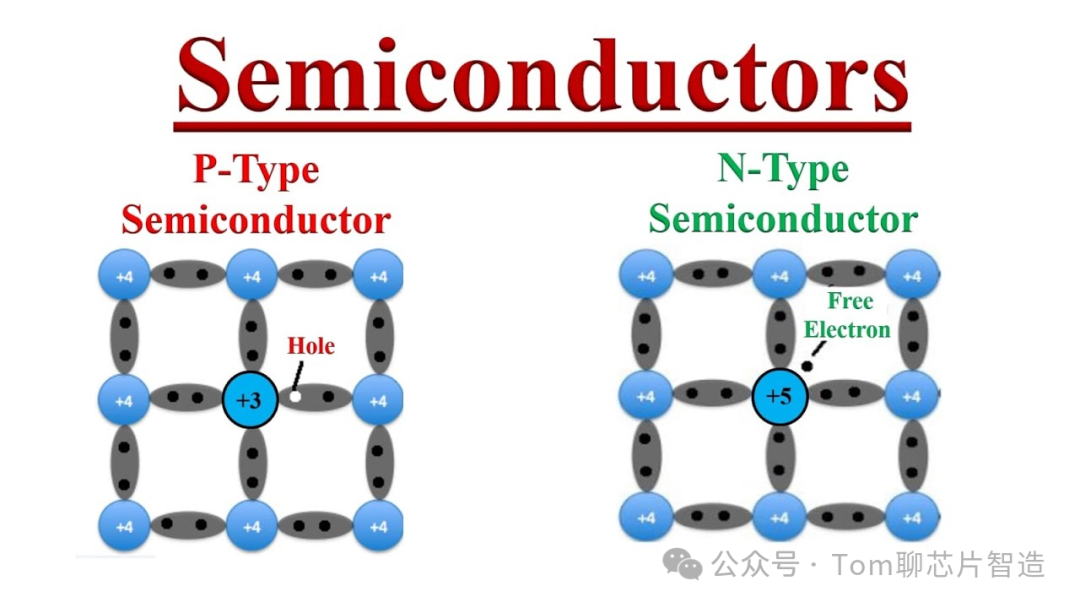

第一代半导体被淘汰了吗

在半导体产业的百年发展历程中,“第一代半导体是否被淘汰”的争议从未停歇。从早期的锗晶体管到如今的硅基芯片,以硅为代表的第一代半导体材料,始终以不可替代的产业基石角色,支撑着全球95%以上的电子设备

被淘汰的FinFET,5nm之后的芯片该如何制造?

被淘汰的FinFET,5nm之后的芯片该如何制造?

评论