本篇整理自Adam Taylor的设计教学博客。

在我写的大多数博客里,都演示或解释了FPGA/SoC的设计细节技术。但是这篇文章将有所不同,因为在这里我要提出另外一个问题。

你该如何开始做可编程逻辑设计的架构?

在我有一次同时在为三个FPGA项目设计架构(作为卫星开发的一部分)时,这个问题浮现在我的脑海中。当然,由于最终应用场景的原因,该架构受到了主承包商和航天局的多次审查。因此,我将尽可能详细的画出架构图,以便让我的设计团队可以很轻松地从中进行工作。

可编程逻辑的架构设计可能非常复杂,因此好的架构通常要定义以下几个元素:

1.模块需要实现所需的功能,当然,这些模块也可以包含层次结构。

2.每个模块接收时钟和时钟使能,必须考虑如果信号跨越多个时钟域时的跨时钟域需求。

3.每个模块收到的复位。就像时钟一样,必须考虑每个模块的复位要求。

4.架构中每个模块接口信号相互连接

高效的架构和实现应尽可能利用供应商的现有IP核。确定可以在整个体系结构中重用的模块也是明智的,例如控制算法或通信总线。我的设计中有3个FPGA需要构建,因此识别可以通用的模块将在开发和验证过程中节省大量时间。

接口重用十分划算,因为它是标准化模块。使用标准接口(例如AXI,AXI Stream和APB)作为模块接口,可以在多个设计中轻松复用。在我的这个项目中,可能不需要复用IP核,但在将来的开发中可能需要相同的功能。

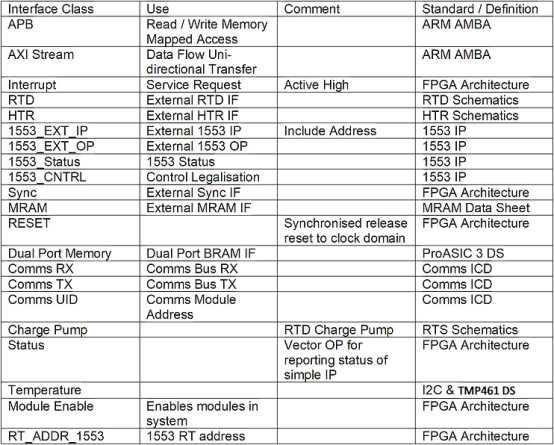

在我的复杂接口(如ADC/DAC接口、AXI或存储接口)架构图中,我更喜欢使用一类接口类型,该类型包含所有较低级别的信号。然后可以在体系结构文档中定义接口类和所有信号。这种方法有几个优点:它使架构图更简单,并使修改(例如 信号添加或重命名)只需要在一个位置进行。

在创建架构时,我的传统方法是从笔和纸开始,勾勒出主要的设计模块和关键界面。完成此操作后,我将使用Visio将其电子图形化,以使其添加在文档中时看起来更加专业。

当然,此图需要显示块之间的所有信号和信号类别。理想情况下,工程师应能够拾取架构和架构文档,并根据其角色开始开发或验证。

在研究架构时,我对其他工程师如何开发可编程逻辑架构感到好奇,因此我在多个FPGA讨论板/论坛上提出了问题并收到了很多有趣的回答。大多数受访者表示他们使用了常见的图纸设计套件。

我们可以使用这里所有的绘图包创建漂亮的架构图,有趣的是,有几个人回答说他们使用Symbolator,而我并不熟悉。

Symbolator是Windows和Linux中的命令行工具,它将读取VHDL、Verilog和组件声明然后生成组件图。然后可以在您首选的图纸包中使用这些symbol。

直接安装Symbolator。我们可以使用pip进行安装,并注意您安装的时候可能需要安装一些其他软件,包括Pycairo,PyGObject和Python-gi-cairo。完成此操作后,您可以使用各种不同格式和表示样式的组件声明创建组件symbol。

自从我学习到有关Symbolator的知识以来,我感觉这工具还挺好用,于是决定将它用到我正在设计的三个架构工作中。

Symbolator的介绍地址:https://kevinpt.github.io/symbolator/

我非常喜欢使用清晰的时钟和数据接口组定义来创建block。这一次,我使用Symbolator和Visio完成了架构设计,但对于各位架构师来说,每个人都有每个人的习惯。大家更习惯如何开展FPGA/SoC架构设计工作呢?

原文标题:你一般如何做可编程逻辑设计的架构?

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

FPGA

+关注

关注

1664文章

22537浏览量

640181 -

soc

+关注

关注

40文章

4647浏览量

230477

原文标题:你一般如何做可编程逻辑设计的架构?

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

深入解析IGLOO2 FPGA与SmartFusion2 SoC FPGA:特性、参数与应用

深入解析IGLOO2 FPGA与SmartFusion2 SoC FPGA:性能、规格与应用考量

深入解析IGLOO2 FPGA与SmartFusion2 SoC FPGA:性能、特性与应用

深入解析IGLOO2 FPGA和SmartFusion2 SoC FPGA:特性、参数与应用

XC7Z020-2CLG484I 双核异构架构 全能型 SoC

探索IGLOO2 FPGA与SmartFusion2 SoC FPGA的电气特性与应用潜力

Microsemi IGLOO2 FPGA与SmartFusion2 SoC FPGA深度剖析

【「龙芯之光 自主可控处理器设计解析」阅读体验】--LoongArch的SOC逻辑设计

AMD UltraScale架构:高性能FPGA与SoC的技术剖析

【VPX650 】青翼凌云科技基于 VPX 系统架构的 VU13P FPGA+ZYNQ SOC 超宽带信号处理平台

智多晶FPGA设计工具HqFpga接入DeepSeek大模型

Altera Agilex 3 FPGA和SoC产品介绍

如何开展FPGA/SoC架构设计工作?

如何开展FPGA/SoC架构设计工作?

评论