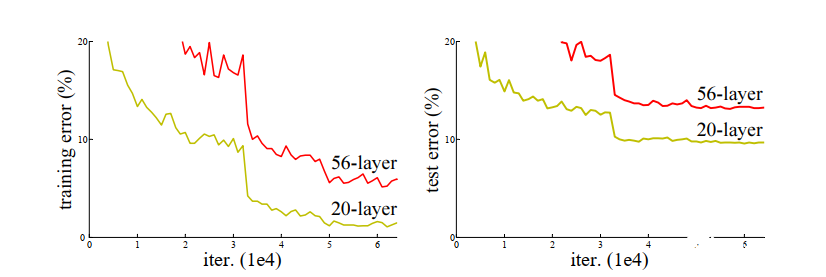

神经网络以其强大的非线性表达能力而获得人们的青睐,但是将网络层数加深的过程中却遇到了很多困难,随着批量正则化,ReLU 系列激活函数等手段的引入,在多层反向传播过程中产生的梯度消失和梯度爆炸问题也得到了很大程度的解决。然而即便如此,随着网络层数的增加导致的拟合能力退化现象依然存在,如下图所示

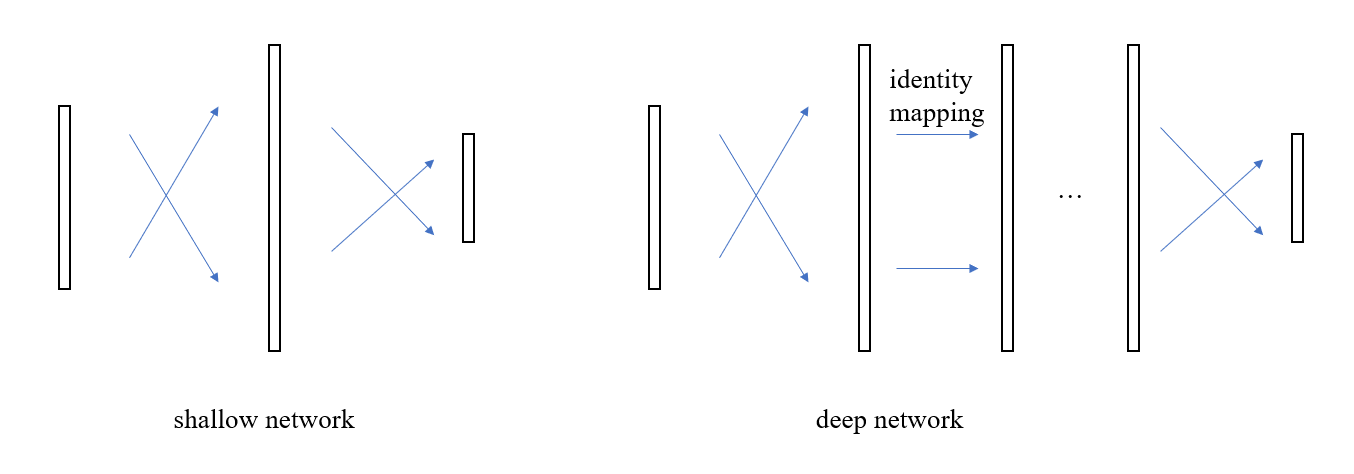

可以看到,训练误差和测试误差都随网络层数的增加而增加,可以排除过拟合造成的预测性能退化。所以这里存在一个逻辑上讲不通的问题,通常来说,我们认为神经网络可以学习出任意形状的函数,具体到这个问题上来,假如浅层网络可以获得一个不错的效果,那么理论上深层网络增加的额外层只需要学会恒等映射,即可获得与浅层网络相同的预测精度

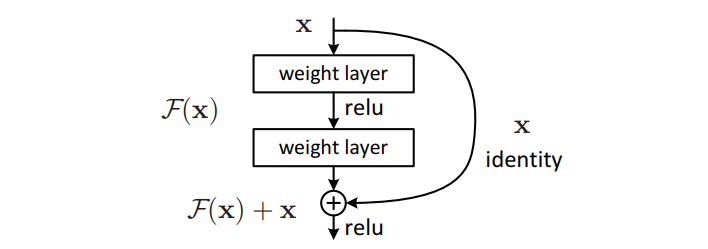

但实际情况根本不是这么回事儿,那么问题出在哪儿了呢?我们一厢情愿的认为中间层能够学会恒等映射,但事与愿违,这一假设不成立,也就是说,具有很强的非线性拟合能力的传统神经元结构却连最简单的恒等映射都模拟不了,抓住这一要点后,新的优化方向便映入眼帘了,既然这种交叉连接的神经元无法实现恒等映射,那么再增加一路恒等映射的连接不就行了

这样一来,假如两层之间的恒等映射是最优解,就像之前提到的那种情况,那么只需要权重层,即图中的 weight layer,学会把所有的权重都设为 0 就行了,而这种学习任务是很简单的。

所以可以总结道,resnet 的提出是因为发现了普通的神经网络连接方式无法实现有效的恒等映射,于是额外增加了一路恒等连接层来辅助学习。体现在最终效果上就是说普通神经网络的连接方式更容易学习到残差,所以这种方式就被称为残差学习。

编辑:jq

-

神经网络

+关注

关注

42文章

4827浏览量

106792 -

函数

+关注

关注

3文章

4406浏览量

66831

发布评论请先 登录

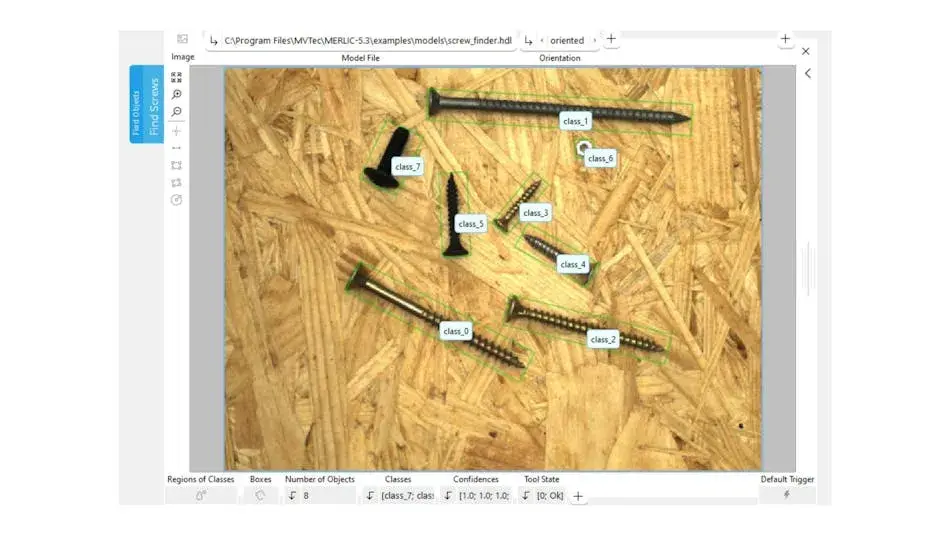

如何在机器视觉中部署深度学习神经网络

TFT液晶显示屏为什么会显示残影、如何解决

AI SoC #BK7258 AI能力和技术参数深度解读

直播 | GB/T 45086与ISO11451标准深度解读研讨会笔记请查收!

轮式移动机器人电机驱动系统的研究与开发

革命性神经形态微控制器 **Pulsar** 的深度技术解读

瑞萨365 深度解读

深度解读对残差网络动机的理解

深度解读对残差网络动机的理解

评论