最近有几个热点事件发生了,好像都跟CXL有关,小编前年也关注到这一点了,可以看下这篇文章“CXL高速互连技术成员数已从9名增加到33名”

美光退出3D Xpoint,移至CXL

首先第一件事大家有目共睹,那就是美光退出3D Xpoint,移至CXL。美光科技正在退出曾经有希望的3D Xpoint非易失性存储器市场,而是随着带宽需求的飙升,将其数据中心的工作重点放在新兴的Compute Express Link接口上。

美光公司总裁兼首席执行官Sanjay Mehrotra本周表示,这家内存制造商将停止3D Xpoint的开发,并将“研发投入重新分配”到基于新兴的CPU内存行业标准接口Compute Express Link(CXL)的新内存产品上。

美光在解释其停止3D Xpoint开发和制造的决定时指出,由于对内存容量和速度的限制将通过两种技术解决:高带宽内存(HBM)和CXL结构,因此未来对3D XPoint芯片的需求将不足。

美光的退出标志着3D Xpoint技术的转折点。尽管英特尔通过其Optane持久性内存系列将其内存技术版本提高了一倍,但美光科技却开始采用旨在缓解数据中心瓶颈的新兴CXL标准。言外之意,美光可以将其针对Xpoint开发的相变存储处理技术改编为CXL,并且CXL旨在处理异构存储器体系结构。

SK hynix CEO演讲提到CXL

仅次于三星的全球第二大内存制造商SK Hynix的首席执行官曾暗示RAM和CPU的合并以及Compute Express Link标准的兴起。

首席执行官Seok-Hee Lee在电气和电子工程师协会的国际可靠性物理研讨会(IRPS)上发表了主题演讲,他对存储器的未来以及依赖它的行业发表了自己的见解。演讲中并且还暗示苹果公司正在采用其M1设计将CPU,内存和更多功能整合到同一芯片上。

Seok-Hee Lee说:“我们正在改进DRAM和NAND每个领域的技术发展所需的材料和设计结构,并逐步解决可靠性问题。如果以此为基础成功地对平台进行创新,那么将来可以实现低于10纳米(nm)的DRAM工艺,并可以堆叠600多个NAND层。”

Astera Labs 发布CXL产品

数据的爆炸式增长以及诸如人工智能和机器学习之类的特殊工作负载的主流化,要求专用的加速器与同一主板或同一机架内的通用CPU并排工作,同时共享一个公共的内存空间。CXL 2.0互连对于启用此类缓存一致的系统拓扑。

作为CXL联盟的早期成员,Astera Labs发布了最新的CXL和PCIe连接解决方案,这对于实现云中人工智能的全部潜力至关重要,也开创了真正改变技术格局的专用解决方案。

Untether AI发布tsunAImi卡

一家名为Untether AI的加拿大初创公司已经构建了tsunAImi,这是一种PCIe卡,其中包含四个runA1200芯片,这些芯片将内存和分布式计算结合在一个裸片中。

tsunAImi卡最终会挂接到支持PCIe Gen 5的Compute Express Link(CXL)上,并因此提供一个共享的资源池,以加速AI处理。

Untether卡将微小的PE(处理元件)分布在整个SRAM中,计算被转移到数据中,这些PE不是通用CPU。它们旨在加速特定类别的AI处理。我们可以设想一个专用的AI系统,该系统具有一个主机CPU,该主机CPU通过PCIe总线控制加载到tsunAImi卡中的事物和数据,以进行相对即时的处理,而几乎不需要将数据移入PE的额外数据移动。

Untether设想将其tsunAImi卡用于加速各种AI工作负载,例如基于视觉的卷积网络,用于自然语言处理的注意力网络以及用于金融应用的时间序列分析。

总结

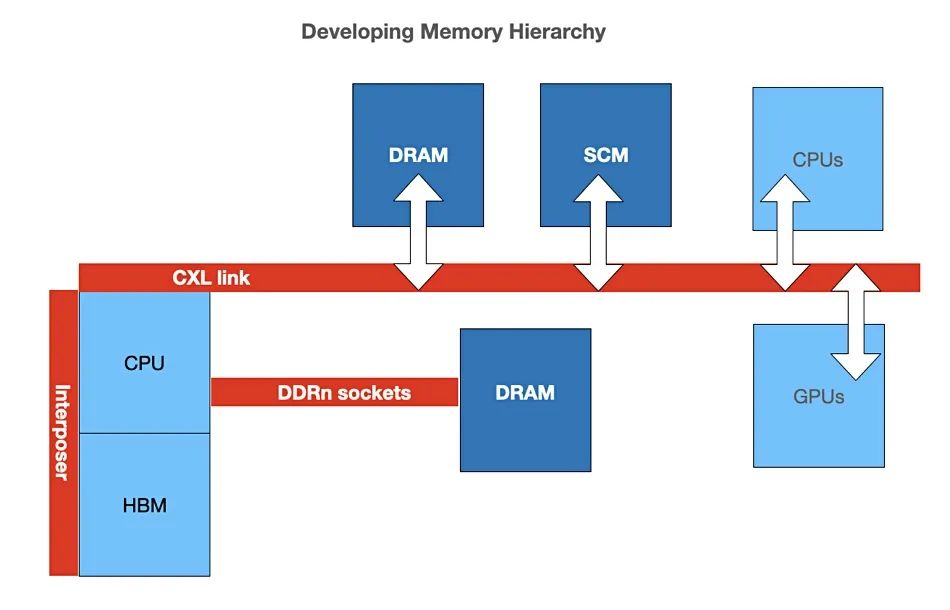

可以看到很多存储厂商都在基于CXL上面做文章,借用Google的资深工程师Roland Dreier的推文总结下:“ 将来的内存层次结构,其中CPU具有HBM封装,而另一层CXL连接的则是RAM,其中DDR总线将消失”

有人说CXL仅对“直接访问Host主存处理数据,或者Host直接访问设备存储器处理数据”模式的场景有提速作用,对于原本就必须进行数据拷贝之后本地处理的场景基本无效,看了这么多案例,你对CXL的前景和发展怎么看?

原文标题:Compute Exchange Link(CXL)为什么这么火?

文章出处:【微信公众号:存储社区】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

3D

+关注

关注

9文章

2990浏览量

113808 -

内存

+关注

关注

9文章

3173浏览量

76112 -

美光

+关注

关注

5文章

737浏览量

53248

原文标题:Compute Exchange Link(CXL)为什么这么火?

文章出处:【微信号:TopStorage,微信公众号:存储加速器】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

紫光国芯荣获2025年度CXL产品技术创新奖

请问bsp文件夹中各芯片厂商的外设drv文件都是由芯片厂商自己开发的吗?

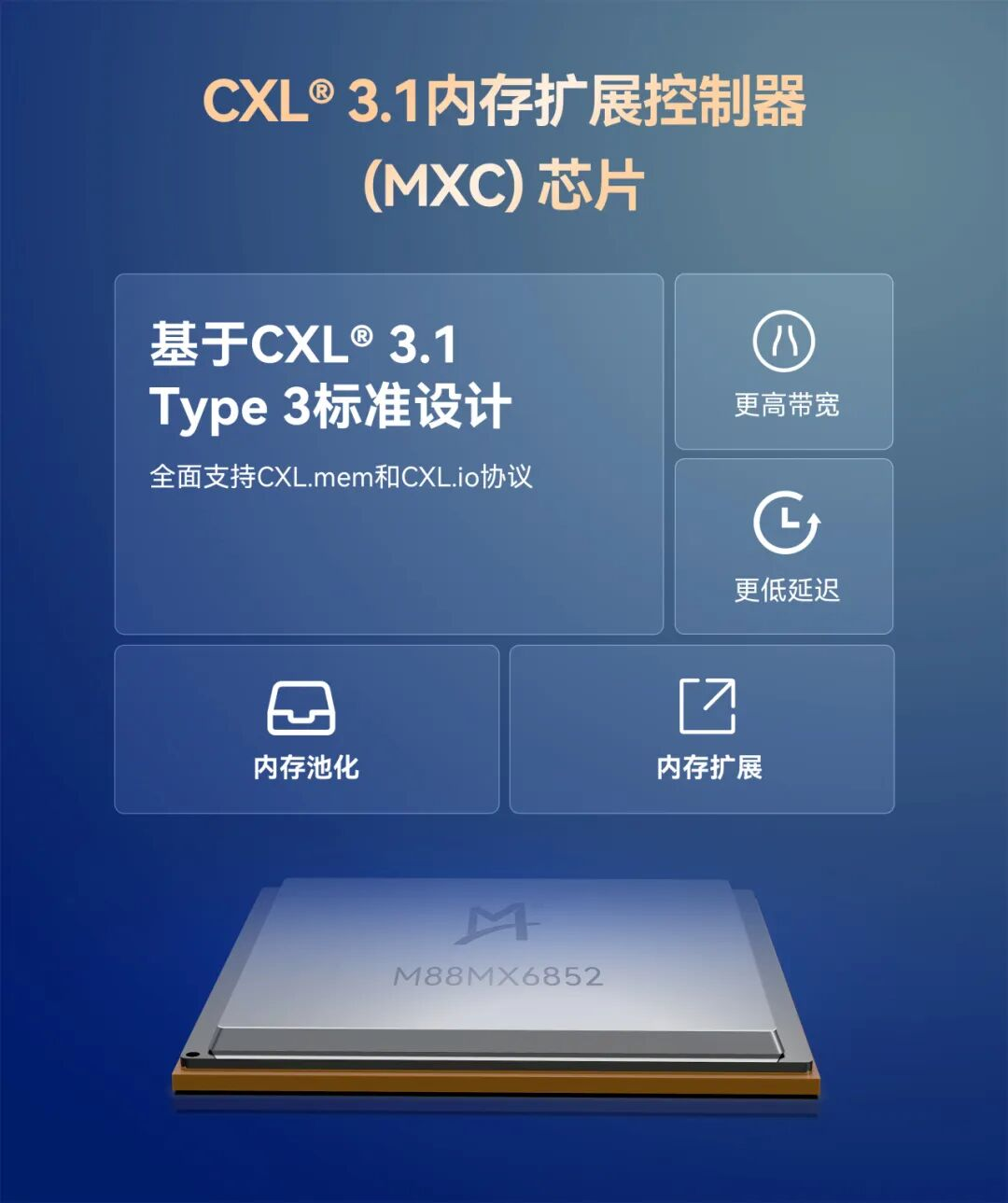

64GT/s+8000MT/s:澜起CXL 3.1芯片破解数据中心内存瓶颈

澜起科技推出CXL® 3.1内存扩展控制器,助力下一代数据中心基础设施性能升级

第二代AMD Versal Premium系列SoC满足各种CXL应用需求

Arm Neoverse CMN S3 推动Compute Express Link (CXL) 存储创新

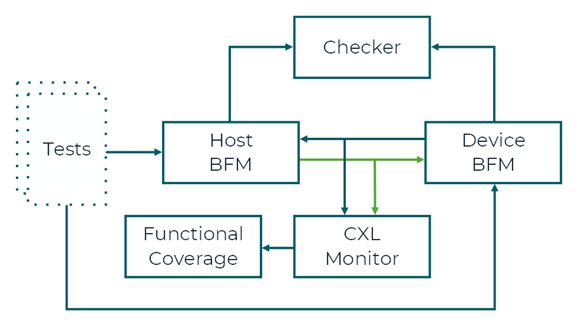

新思科技解读CXL 3.1标准

SMART Modular CXL AIC内存扩充卡获CXL联盟认证

SMART Modular世迈科技CXL内存扩充卡获CXL联盟认证

澜起科技PCIe 6.x/CXL 3.x Retimer芯片面世

澜起科技正式推出PCIe 6.x/CXL 3.x Retimer芯片

澜起科技推出PCIe 6.x/CXL 3.x Retimer芯片

澜起科技CXL®内存扩展控制器芯片通过CXL 2.0合规性测试

澜起科技MXC芯片列入首批CXL 2.0合规供应商清单

厂商基于CXL上面做文章的案例

厂商基于CXL上面做文章的案例

评论