在做系统级芯片(SoC)的设计规划时,需要考虑哪些主要因素?目前主流的SoC一般包括哪些功能模块或IP?有什么新的技术趋势值得关注?RISC-V与FPGA如何有机结合助力SoC设计?当前的SoC设计在性能、功耗和尺寸方面面临哪些挑战?有何解决方案?物联网和边缘计算等嵌入式系统对SoC设计提出了什么特别要求?

1.在做系统级芯片(SoC)的设计规划时,需要考虑哪些主要因素?

一定是先从市场需求以及相关需求的时间窗口作为起点,然后根据自身的人力与技术资源,结合开发的金钱成本、时间成本和维护成本,考虑工艺和IP的选择。举例来说,现在如果还在用40nm的工艺技术来设计SoC,将很难应对市场普遍需要低功耗的趋势。可是采用先进工艺的SoC的话,新工艺下IP的可选择度相对较低、费用较高昂、可靠性与相互适配性也都存在不确定性。可见一款SoC是否可以一次成功,里面潜伏着众多相互影响的风险,对掌控整体的投入与产出带来不小的挑战。因此,就衍生出了降低风险、加快上市时间,这个非常重要的因素。

利用现有的相对性能不高但低功耗的处理器,将已经验证过的高性能IP模块(甚至多个软核处理器)用低功耗、小面积的FPGA来实现,再利用先进的封装技术进行集成,就有了可以随时更新的可编程(Programmable)SOC。例如,易灵思的“易构”平台就是一种非常好的,可以降低风险、加快上市时间的方案。

2.目前主流的SoC一般包括哪些功能模块或IP?有什么新的技术趋势值得关注?

以AIoT、云端以及手持消费产品应用为例,可以说需要的功能模块非常多,例如ADC,ARM的多核处理器,以及高速收发器等。对于适合无线应用的SoC,需要模拟和数字模块的合成,而对于协议的处理还要加入ARM处理器。对于AIoT以及手持类别的SoC,最重要的就是低功耗。现在我们比较关注的还是跟视频处理相关的SoC,这个领域里面一个明显的趋势就是把高性能的视频处理功能从处理器中剥离出来,用专门的硬件电路实现,比如将视频编解码功能的H.264/H.265硬核化。最具代表的就是某知名企业的35xx系列:他们将已经固定的算法尽可能硬核化,以此带来功耗的降低;同时留有一定的接口可以接入来自多个Sensor或其它器件里的音视频数据与控制数据;并采用内置的AI,来扩大系统的性能和适配性。

易灵思的FPGA,具备硬核的MIPI和DDR控制器,以及众多LVDS和通用IO。相比一般的SoC,能扩大Sensor的接入种类、数量和带宽,以及提高图像处理能力。并且对于高端的SoC,也可以补充其原有接口的不足,并提供协处理,来提高系统性能和灵活性,为更高的产品性能、更宽的市场覆盖和更快的上市时间提供广阔的空间。

3.RISC-V与FPGA如何有机结合助力SoC设计?

RISC-V拥有非常丰富的生态资源,而且其软核形态是依托FPGA的,使得FPGA立即能拥有这些丰富的生态资源。经过优化的RISC-V,不单降低了对FPGA的资源消耗,还通过外设的多样性,赋予FPGA在并行算法应用中对各功能模块更快捷的调度和配置能力。FPGA擅长高性能的并行应用,加入RISC-V就可以完成多映像加载、网络协议的缝合,甚至是多个独立RISC-V集成的应用。

当前的软核RISC-V,在平台的移植性方面也非常轻松。有很多嵌入式应用,例如基于ARM Cortex M4的应用,要集成在低成本的FPGA中还有一定难度。好消息是,易灵思16nm工艺的Titanium系列第二代FPGA,内核可以轻松达到450Mhz,让软核的RISC-V处理器可以跟硬核的Cortex M4处理器分庭抗礼。而在性能相当的情况下,RISC-V所有总线以AXI的形式内置于FPGA,可以带来高度灵活性、快速上市时间和极低的IP集成风险等额外的价值。

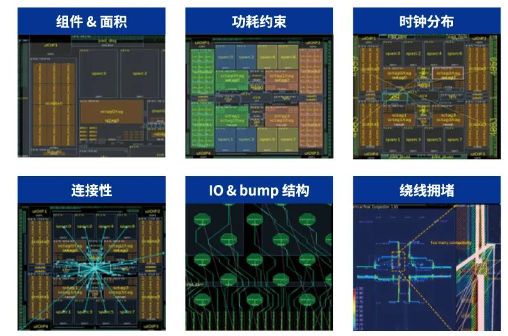

4.当前的SoC设计在性能、功耗和尺寸方面面临哪些挑战?有何解决方案?

一般来说,SoC想在性能、功耗和尺寸方面均表现出色,就必须在芯片工艺上不停采用更高级的工艺。但是不断上涨的研发与流片费用,产品面世时间的不确定性,和现今市场需求的加速度变化,给设计者带来了巨大的挑战。

从提高性能的角度来看,设计者要使功耗和尺寸不增加太多,同时能控制研发成本并让产品快速面市,我们推荐以下几种方案。对于较低端的应用,可以采用低功耗、小面积的FPGA来内嵌RISC-V处理器和其相关外设,并加入逻辑电路实现高性能模块。易灵思40nm的Trion系列就是很好的选择。还以易灵思的FPGA为例,若需要再高一点的性能,可以采用先进的封装技术,将硬核处理器裸片与Trion FPGA的裸片合封,或者直接采用16nm的Titanium系列更高性能、更低功耗和更小尺寸的FPGA。如果在这个基础上,希望尺寸再小一点,就可以考虑直接把现有处理器与Trion或者Titanium的FPGA内核,在版图一级进行合成,成为单一的晶片,不但尺寸得到高度缩减,功耗和性能也会有不错的优化。

如果希望最优的性能、功耗、和尺寸的组合,同时保持较快速的面市时间和对需求变化的高度适应性,就可以定制FPGA的规格,并嵌入到整个SoC的设计中。这样的单一晶片SoC,虽然研发和时间的成本要比前面几种方案稍高,但在同等性能下,它的单片功耗和尺寸的优势是最高的。而且有了内嵌的FPGA模块,就可以非常有效地抵御市场需求在前期的不确定和后期的变化所导致的问题、面市时间拖长以及产品生命周期缩短的风险。它能先于竞争对手面市、在市场竞争力和长久性方面强于竞争对手,是非常适合高端且量大市场的。

5.物联网和边缘计算等嵌入式系统对SoC设计提出了什么特别要求?

首先来讲,边缘计算和物联网领域的重点是低功耗和低成本。边缘计算早已经不是新鲜的话题,从宏观上来看早就开始商业化,比如高通和华为的NPU。但是很多物联网设备里用不上这么高的算力,而且这些器件还远远不能满足这些场景的低功耗要求。而单一的MCU大部分又都算力太低,跑不了边缘计算中推理的应用。也有很多项目曾经试图通过MCU+DSP或者DSP+FPGA等组合实现算力提升,但在算力、功耗、成本方面都无法达到一个理想的平衡点。

易灵思的Quantum架构所带来的低功耗,低成本和高密度的优势,配合针对Quantum架构优化后的RISC-V软核,能够在满足算力的前提下兼顾低功耗和低成本,并且还能提供相当程度的灵活性,会对物联网与边缘计算的发展起到重要的推动作用。

责任编辑:lq

-

物联网

+关注

关注

2939文章

47365浏览量

408672 -

SoC设计

+关注

关注

1文章

151浏览量

19481 -

边缘计算

+关注

关注

22文章

3477浏览量

52761

原文标题:系统级芯片(SoC)的复杂设计选择:FPGA

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

BMS设计中如何选择MOSFET——关键考虑因素与最佳实践

科研级相机是什么?以及影响信噪比的主要因素

浅谈常见芯片失效原因

影响电解电容寿命的主要因素及其详细分析

制定芯片封装方案的主要步骤和考虑因素

做系统级芯片(SoC)的设计规划时,需要考虑哪些主要因素?

做系统级芯片(SoC)的设计规划时,需要考虑哪些主要因素?

评论