关注高速先生的Layout攻城狮们最近普遍感到焦虑,都在默默祈祷客户不要看到高速先生最近一期的B站视频——Tabbed Routing,因为大家都很清楚客户看到之后的需求。

为了文章的完整性,我们还是从头捋一捋。Tabbed routing是指将特定形状和尺寸的铜皮,按照一定的规则添加到走线上的一种布线处理方法。该方法是由Intel公司于2015年提出,主要适用于DDR4的数据信号走线。

密集恐惧症患者可能会问,原本清清爽爽的走线,为什么非要整出一身“鸡皮疙瘩”呢?大家都知道,BGA器件或其它管脚密集区域的布线空间有限,寸土寸金,为了能顺利出线,减小线宽并缩小间距是常规操作,比如常用的neck模式走线,这样一来,线是拉出来了,阻抗却被卡了脖子,一路飘高,此外,随着走线间距的减小,串扰也随之增加。于是,Tabbed routing应运而生。

Tabbed routing设计可以增加两根线之间的互容而保持其互感几乎不变,而增加的容性可以有效降低走线的阻抗,减小表层线的远端串扰。换言之,Tabbed routing一方面可以改善走线因线宽减小而造成的阻抗不连续,另一方面还能减小表层走线的远端串扰。

听高速先生这么一分析,是否觉得原本犬牙交错的Tab设计瞬间变得凹凸有致了呢?至于是阻抗控制的福音,还是远端串扰的克星?Tabbed routing是否有效?不要看广告,高速先生带你看测试报告。

为了研究Tabbed routing对通道性能的影响,高速先生曾专门设计过相关的测试板,测试结果也可以从一定程度上说明问题。先来看看带状线的情况,DUT(Device Under Test)设计如下,通过比较测试过孔密集区域的内层弧形走线添加Tab前后的参数差异,来检验Tabbed routing的效果。

阻抗测试的结果显示,Tabbed routing对于neck走线偏高的阻抗有一定的拉低作用,可以改善阻抗的连续性。

再来看看万能的S参数,添加Tab的通道由于阻抗的优化,反射减小,回波损耗整体也有所改善,不过,在我们所关注的频段内,串扰却没有明显的变化。

仍然是过孔区域的neck模式走线,继续比较表层线Tabbed routing设计与普通走线的区别。

从阻抗测试的结果可以看出,tab对于阻抗连续性的改善作用依然在线。

相比于添加Tab前后内层走线串扰的基本不变,Tabbed routing表层走线远端串扰的降低肉眼可见。

不过凡事有利就有弊,Tabbed routing虽然对于走线的阻抗和串扰有一定的改善,但是由于添加tab后走线的容性增加,导致信号的延时也会随之增加。这也解释了为什么对于同一等长组的走线,需要保证tab数量的一致。

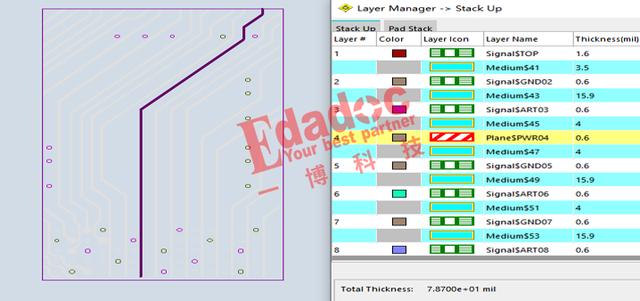

需要注意的是,tab加在不同区域的走线上有着不一样的效果,加在走线的单侧还是双侧,最后的结果也不相同。因此,在实际设计中,要根据具体的层叠,走线等因素来确定tab的尺寸、间距,必要的时候,还要通过仿真确认。

审核编辑:符乾江

-

阻抗

+关注

关注

17文章

983浏览量

48745 -

TAB

+关注

关注

0文章

17浏览量

11809

发布评论请先 登录

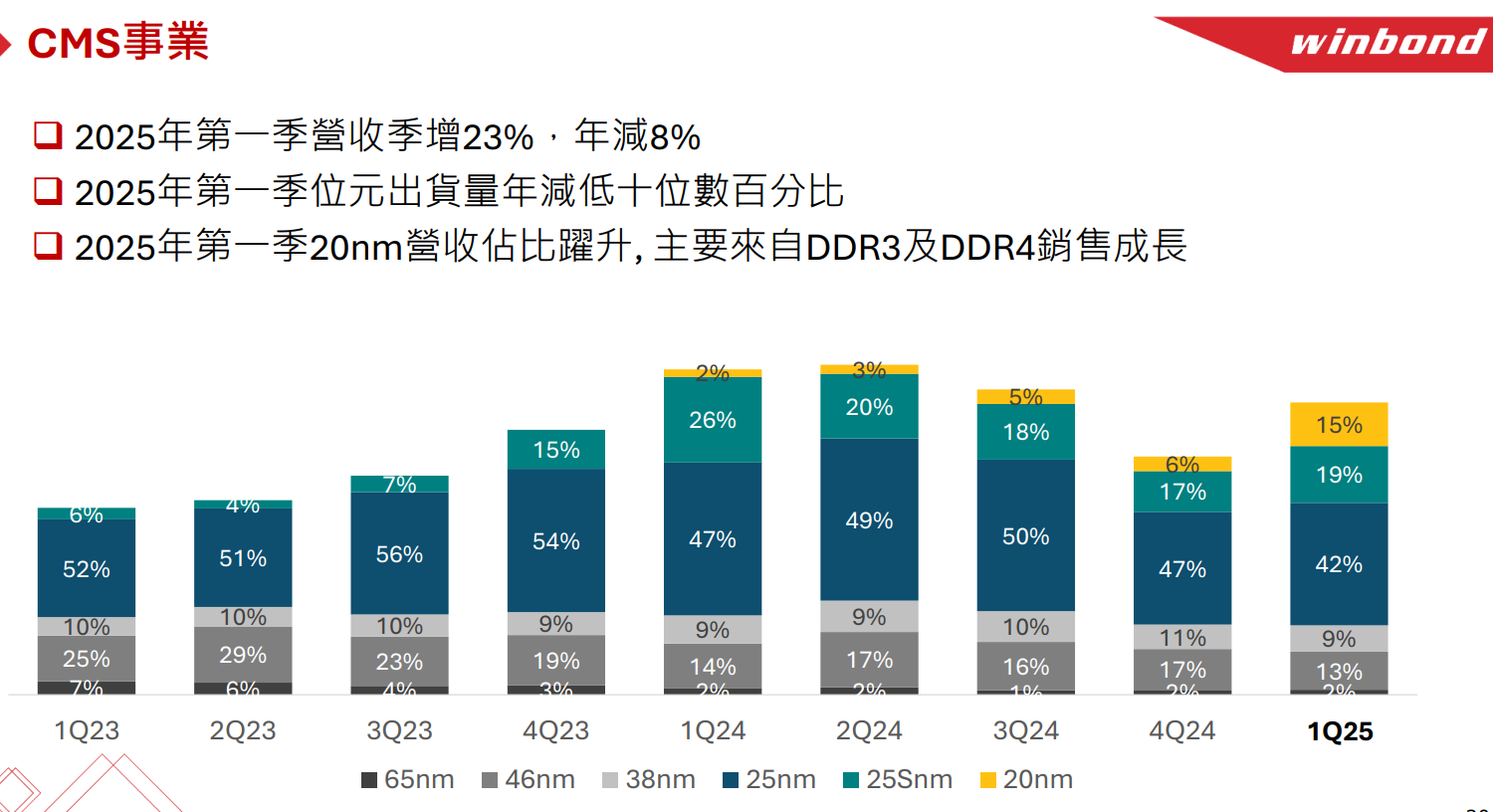

DDR4价格疯涨!现货市场狂飙!

华邦电子推出先进 16nm 制程 8Gb DDR4 DRAM 专为工业与嵌入式应用而生

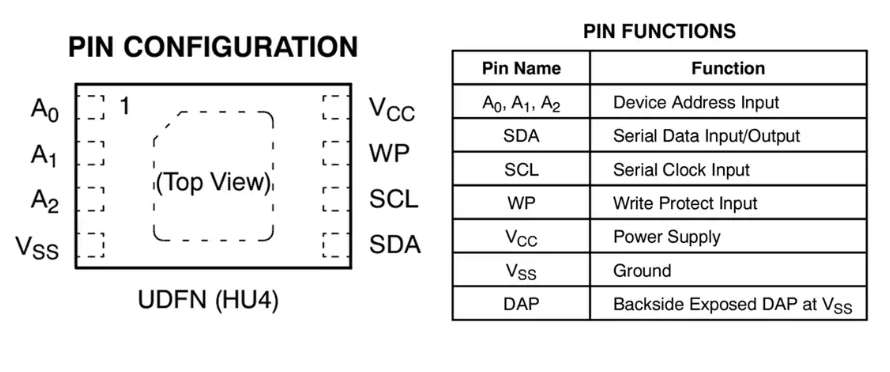

N34C04 EEPROM:DDR4 DIMM的理想SPD解决方案

到底DDR走线能不能参考电源层啊?

三星正式启动DDR4模组停产倒计时,PC厂商加速转向DDR5,供应链掀抢货潮

高速PCB板DDR5数据信号的长STUB要背钻吗?

AD设计DDR3时等长设计技巧

涨价!部分DDR4与DDR5价差已达一倍!

低功耗、低功耗前端模块,适用于蓝牙®信号范围扩展应用 skyworksinc

看点:三星DDR4内存涨价20% 华为与优必选全面合作具身智能

DDR4涨价20%,DDR5上调5%!

VIAVI Xgig4K-PCIe-X4-FL飞行引导插入器适用于PCIE4.0在被测设备和VIAVI协议分析仪机箱箱之间提供数据信号连接

Tabbed routing主要适用于DDR4的数据信号走线

Tabbed routing主要适用于DDR4的数据信号走线

评论