作者: DEAN BANERJEE,MOHAN RUDRAPPA,UDAY MEDA和AJEET PAL,德州仪器(TI)

在大多数锁相环(PLL)合成器应用中,相位噪声是一个关键参数。例如,在雷达中,低偏移频率的相位噪声转化为辨别彼此靠近的两个物体的能力。数据转换器时钟应用还需要低相位噪声,以实现低信噪比。对于接收器,相位噪声有助于检测微弱的信号。对于测试设备,相位噪声有助于测量较低噪声的信号。

领先于性能的应用程序将需要更好的相位噪声,即使它会转化为更多的组件和复杂性。改善相位噪声的一些尝试包括使用带乘法器的固定频率源和使用窄带压控振荡器(VCO),但要以降低频率覆盖范围和下变频VCO频率为代价。在本文中,我们将讨论下变频PLL的VCO频率的方法,并将该方法的仿真结果与实际测量结果进行比较。

PLL理论基础

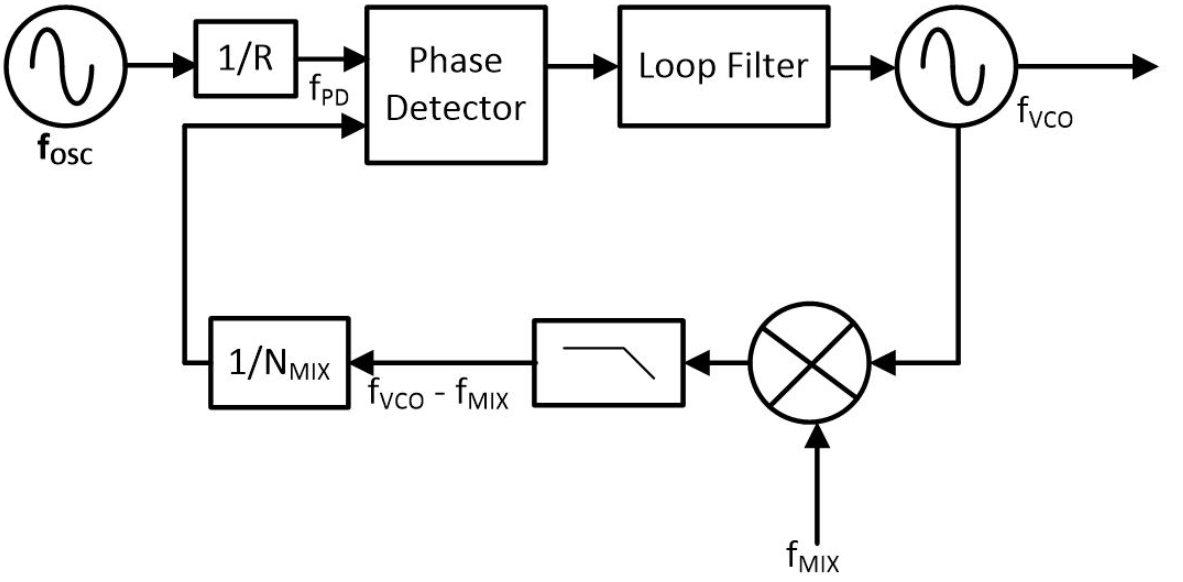

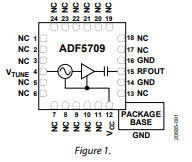

在解释如何下变频信号之前,让我们回顾一下PLL理论的一些基础知识。可以使用PLL从稳定源产生一定范围的频率。图1显示了PLL的传统架构。

图1该框图显示了传统的PLL架构。资料来源:德州仪器(Texas Instruments)

PLL中的相位噪声会严重影响指标,例如接收机灵敏度,误码率和信噪比。影响相位噪声的一个关键参数是通过公式1计算得出的反馈分频器值N。

VCO频率fVCO除以鉴相器频率fPD会产生N,它乘以PLL的分频器和电荷泵。如果可以减小该值,则还可以降低噪声性能。从理论上讲,可以在不增加fPD的情况下将N减小2倍,从而将相位噪声提高到6 dB。如果通过将fPD加倍将N减小2倍,则PLL 1 / f噪声不会提高,但是PLL噪声会提高到3 dB。无论哪种情况,减少N对相位噪声都是有益的。

但是,很少有因素会限制您减少N的程度:

fPD的最大值受到限制;限制fPD的一件事是输入频率fOSC。通常,除非存在乘数,否则fPD不能大于fOSC。许多设备具有一个非常有用的x2乘法器,但是大于该值的分频器通常会比低N所实现的改进增加更多的噪声。除了受fOSC限制之外,最大fPD通常限于几百兆赫兹由于电荷泵的架构。

N的最小值可以被限制。对于更高频率的PLL,N被设计为在非常高的频率下运行,这需要可以对最小N施加限制的预分频器。此外,如果N支持小数,则该小数电路可以对N施加其他限制。

下变频以获得更好的相位噪声

图2显示了一种方法,该方法可以通过添加稳定且非常低的噪声频率fMIX来降低N而又不增加fPD。

图2下变频架构可以帮助实现更好的噪声相位。资料来源:德州仪器(Texas Instruments)

公式2将减少的N表示为:

公式3显示了此架构在环路带宽内的理论PLL相位噪声改善:

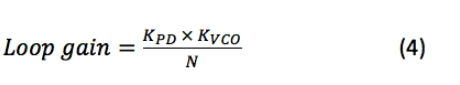

环路增益常数将影响环路动态,如公式4所示:

当环路增益发生显着变化时,环路带宽也将发生变化,从而导致不稳定或更大的环路带宽(具有很高的峰值)。调整电荷泵增益KPD会使环路增益保持相对恒定,就像重新设计环路滤波器一样。

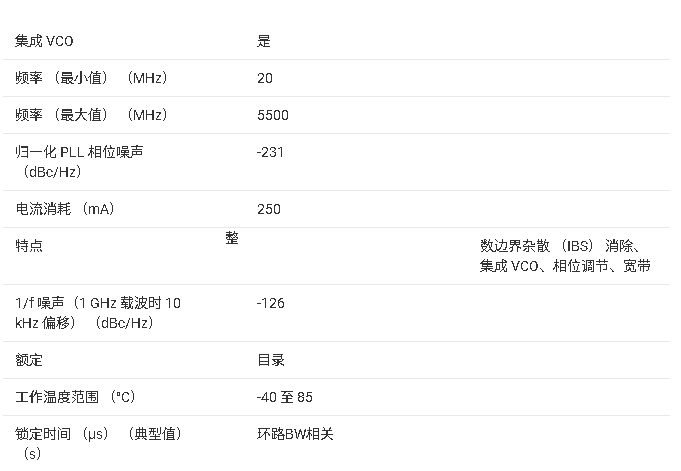

图3显示了理论分析,其中忽略了混频器和用于混频的本地振荡器的噪声以及PLL的任何实际限制。本示例中的默认曲线适用于LMX2820宽带射频合成器。该器件具有200 MHz的fPD和9 GHz的输出频率,因此N为45。从理论上讲,增加的FPD曲线用于将fPD增加到9 GHz。

图3理论分析显示PLL N从45降低到1。来源:德州仪器(Texas Instruments)

下变频曲线显示了使用图2所示的架构将9 GHz输出与无噪声8.8 GHz输出混频器混频至0.2 GHz时的理论相位噪声。对于这些仿真,重新设计环路滤波器可保持类似的效果。环路带宽。

当fPD增加45倍时,PLL噪声平稳性提高,而PLL 1 / f噪声却没有。相位噪声仍然是一个很好的改善,但是当输出进行下变频时,相位噪声性能会大大提高。

默认设置下的相位噪声测量

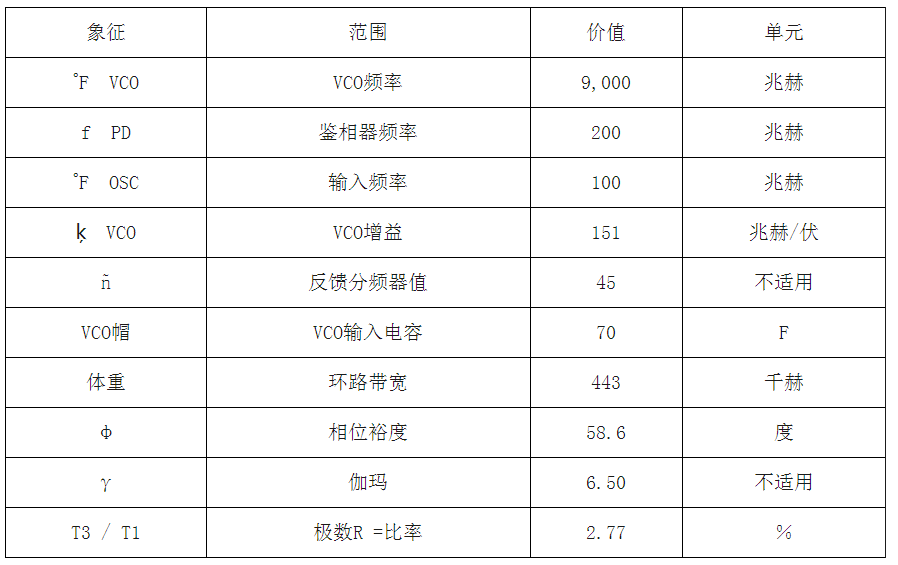

对下变频的理论分析显示出令人鼓舞的结果,但是有必要通过实际测量来证明这一点。因此,在基于LMX2820的评估板的测试中使用了图3中的结果,条件如图4和表1所示。

图4设计示例显示了传统的PLL设置。资料来源:德州仪器(Texas Instruments)

表1播种了环路滤波器参数以进行实际测量。资料来源:德州仪器(Texas Instruments)

我们将来自100 MHz振荡器的相位噪声添加到仿真中。图5比较了测量值和模拟值。尽管模拟中的遥远相位噪声似乎略有偏离,但近距离相位噪声显示出接近的一致性,这表明即使经过1 MHz的偏移,PLL噪声仍在环路带宽内的相位噪声中占主导地位。

图5图形表示形式比较了测量值和模拟值。资料来源:德州仪器(Texas Instruments)

由于PLL噪声主导着近相噪声,因此通过减小N来改善PLL噪声有很多潜在的好处。在这种特殊情况下,已经使用x2输入乘法器将fPD最大化至200 MHz。尽管LMX2820芯片确实具有更高的输入倍增器值,但使用这些更高的倍增器会增加噪声,而噪声的减小幅度要比减小的N值大。因此,在这种情况下,x2输入乘法器是最佳选择。

通过下变频测量相位噪声

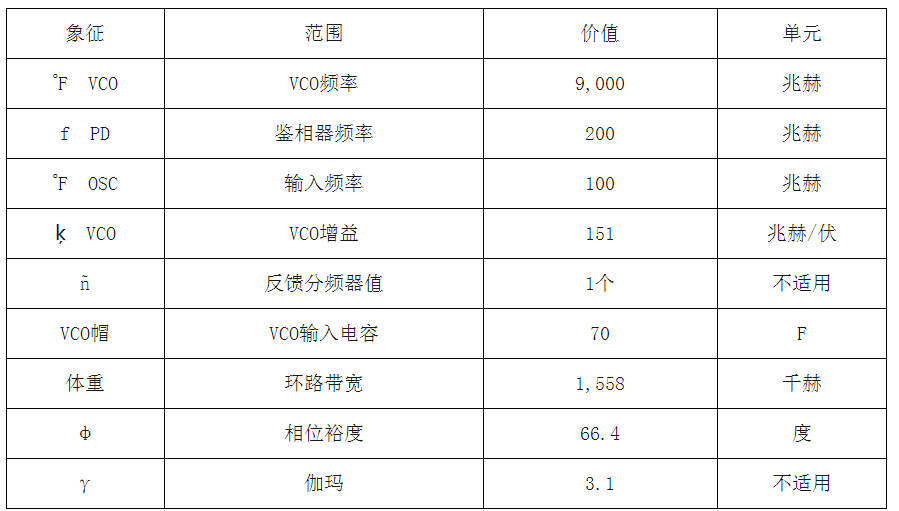

在使fPD最大化的情况下,改善相位噪声的另一种方法是通过下变频降低N。此设计任务需要干净的信号源(通常是固定频率的晶体或该晶体的倍频版本)。但是,对于此设置,为方便起见,我们使用了信号发生器。图6和表2显示了设置条件。

图6这是下变频器架构设置的外观。资料来源:德州仪器(Texas Instruments)

表2显示了下变频架构的环路滤波器参数。资料来源:德州仪器(Texas Instruments)

图7显示了从LMX2820芯片获得的测量结果和仿真,该芯片具有用于下变频频率的独立输入引脚。出于仿真目的,从整个噪声分布图中减去38.9 dB,将本地振荡器(在这种情况下为信号发生器)的相位噪声从8.8 GHz降低至100 MHz。如果混频器具有明显的噪声分布,则可以用相同的方法将其缩小。在这种情况下,无源混频器的噪声远低于系统中的其他噪声源。

图7从宽带射频合成器设备获得的测量结果和仿真。资料来源:德州仪器(Texas Instruments)

我们针对LMX2820器件进行了其他调整。在此器件上使用外部混频器输入引脚需要使用单相频率检测器模式,这有效地使电荷泵增益减半,并使PLL的品质因数降低3 dB。我们将此数字作为模拟因素。

正如公式3所预测的,相位噪声的好处不是20log(45)= 33-dB的好处。无法获得全部理论收益的原因是它受到混频器本地振荡器噪声的限制。通过使用较干净的本地振荡源,可以大幅降低相位噪声。无论如何,如图8所示,相位噪声的改善仍然很大。

图8对于下变频架构,相位噪声的改善仍然很大。资料来源:德州仪器(Texas Instruments)

下转换方法和刺激

除了改善相位噪声外,下变频理论上还可以改善杂散。通过下变频,工程师可以使用混合频率使fVCO偏离fOSC的近整数倍,从而改善整数边界杂散。此外,通过减少N,理论上电荷泵的整数PLL杂散将减少20log(N)。

马刺很复杂,有多种原因,因此很难不经过测试就知道马刺的全部收益。但是,如果使用正确的方式,则降频转换方法理论上可以改善某些杂讯。

编辑:hfy

-

振荡器

+关注

关注

28文章

4195浏览量

143190 -

分频器

+关注

关注

43文章

537浏览量

53769 -

电荷泵

+关注

关注

3文章

435浏览量

30868

发布评论请先 登录

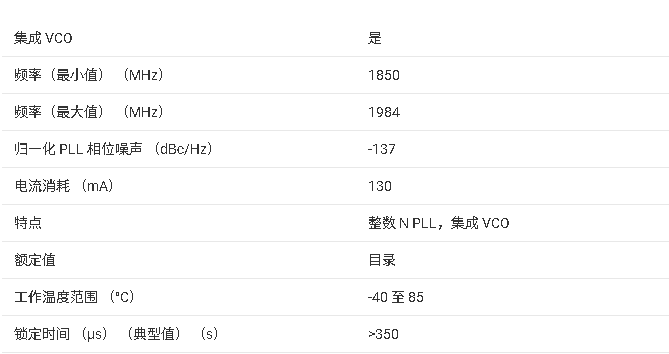

ADF4196:低相位噪声、快速稳定的6 GHz PLL频率合成器

低相位噪声、快速稳定PLL频率合成器ADF4193的设计与应用

相位噪声分析仪(相噪仪)使用与选型指南

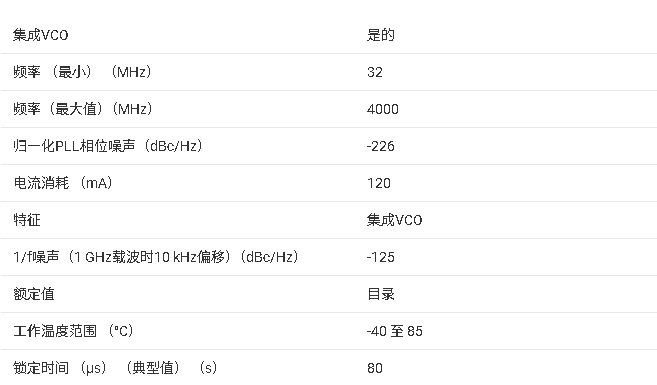

LMX2492/LMX2492 - Q1:14 GHz低噪声分数N PLL的全面解析

是德频谱分析仪N9322C相位噪声测量的实用指南

TRF3761-F 低噪声整数N PLL频率合成器技术手册

LMX2541 超低噪声频率合成器技术文档总结

LMX2582高性能宽带RF合成器(集成VCO)技术文档总结

APPH信号源分析仪-雷达脉冲调制信号的绝对相位噪声和加性相位噪声测量解决方案

通过变频PLL的VCO频率仿真测量获得更好的相位噪声

通过变频PLL的VCO频率仿真测量获得更好的相位噪声

评论