在2020年国际互连技术大会上,imec首次展示了采用钌金属(Ru),具备电气功能的双金属层级结构(2-metal-level)互连技术。该金属是使用特殊的半镶嵌和气沟(Air Gap)技术生产,具有更好的使用寿命和更佳的物理强度(mechanical strength)。

透过一个12层金属分析,证实了这个半镶嵌技术可带来系统级的优势,包含降低阻容(resistance-capacitance,RC)、功耗和IR-Drop。此外,钌金属也展现了绝佳的潜力,可望作为先进制程的中段(MOL)接触插塞(contact plugs)的替代方案。

目前,替代性的金属化材料(例如钌)和替代性的金属化制程(例如半镶嵌),正被密集的研究中,以前进2纳米或者以下制程技术的前段(BEOL)和中段(MOL )互联。

在前段设计中,imec提出了一种半镶嵌(semi-damascene)整合技术,作为传统的双重镶嵌(dual-damascene)的替代方案。为了能够完全的发挥这种结构技术的潜力,需要有除了铜(Cu)或钴(Co)以外的其他金属,它们可以被沉积而无扩散阻挡层,且具有高的体电阻率,并可以被图模式的使用,例如:减成蚀刻。

这个结构也可以增加互连的高度,并结合气隙作为电介质,将有望减少阻容(RC)延迟,这是后段制程的主要瓶颈。

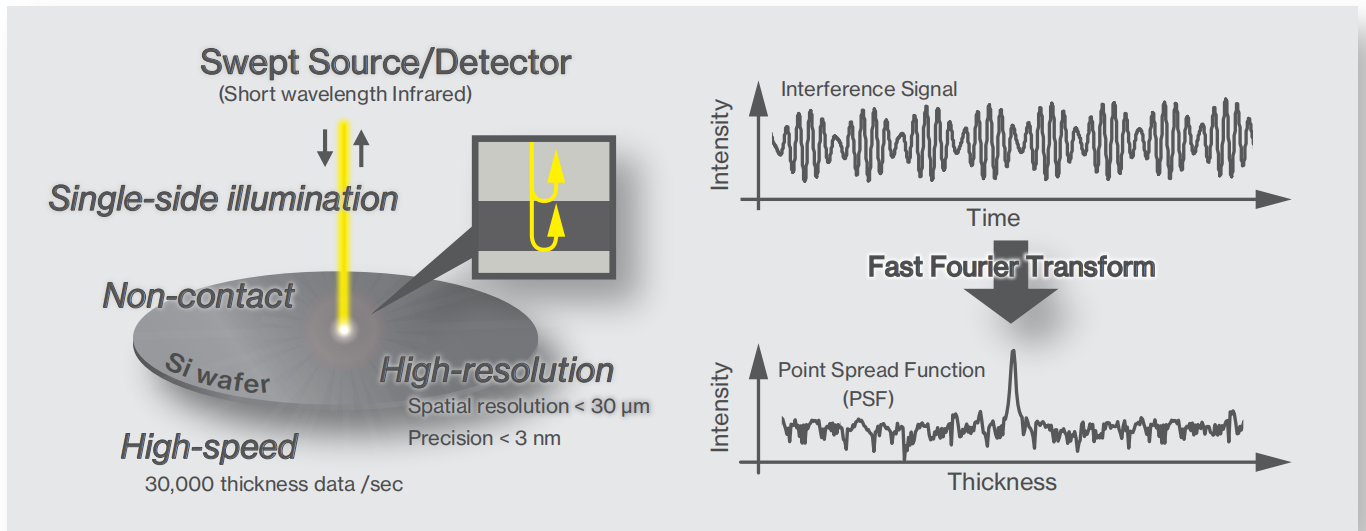

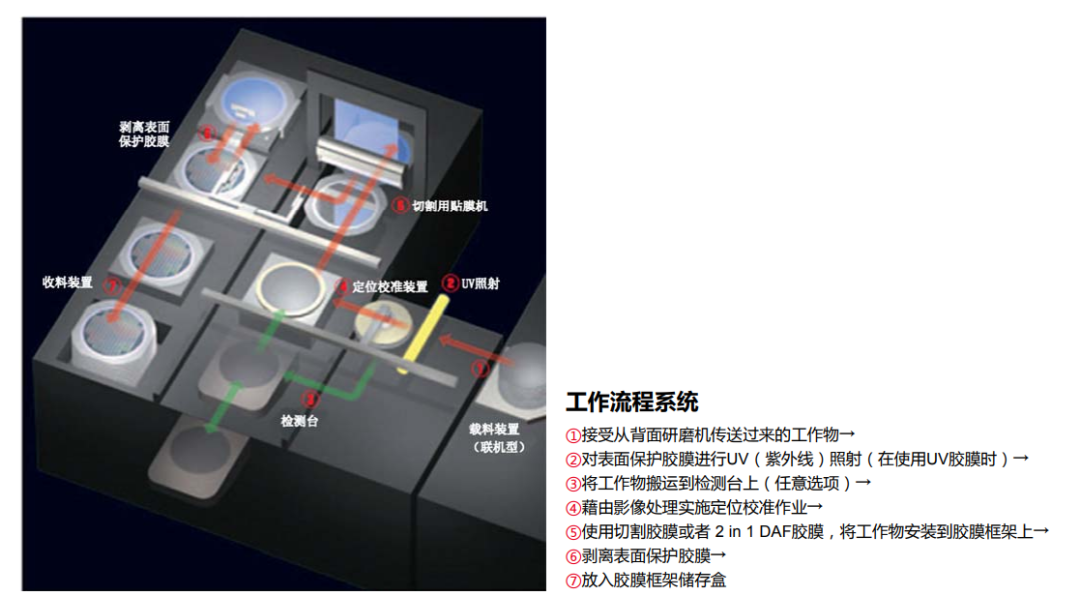

Imec首次使用「钌」进行金属化,并在300mm晶圆上制造并特性化了双金属层的半镶嵌模组。在30纳米金属间距线的测试结构显示,有超过80%以上的可重复性(无短路迹象),且使用寿命超过10年。同时钌的气隙结构的物理稳定性可与传统的铜双重镶嵌结构相比。

Imec纳米互连专案总监Zsolt Tokei表示,结果显示,半镶嵌与气隙技术相结合不仅在频率和面积上优于双镶嵌,而且为进一步的性能强化提供了可扩展的途径。气隙技术则显示出将性能提高10%,同时将功耗降低5%以上的潜力。使用高深横比的电线,可将电源线路中的IR下降减少10%,进而提高可靠度。在不久的将来,为半镶嵌模组开发的光罩组(Mask set)将能够进一步改善半镶嵌的整合,并通过实验验证去达成预期的性能改进。

Imec还展示了在先进MOL接触插塞中,使用「钌」替代钴或钨的优势。imec CMOS元件技术总监Naoto Horiguchi指出,无阻绝层的钌,有潜力进一步减小因缩小接触面积而产生的接触电阻。

在一项评测研究中,imec评估了钌和钴,结果表明钌是替代MOL狭窄沟槽中的钴,最有希望的候选方案。在0.3纳米氮化钛(TiN)内衬(无阻挡层)的孔洞,填充钌的电阻的性能,优于在相当的制程中填充钴(有1.5纳米氮化钛阻挡层)。研究还证明,钌作为源极和汲极接触材料,在p-硅锗(SiGe)和n-硅(Si)上的接触电阻率都较低,约为10-9Ωcm-2。

责任编辑:tzh

-

电阻

+关注

关注

88文章

5735浏览量

178570 -

晶圆

+关注

关注

53文章

5344浏览量

131690 -

制造

+关注

关注

2文章

547浏览量

24707

发布评论请先 登录

12寸晶圆的制造工艺是什么

清洗晶圆去除金属薄膜用什么

TC Wafer晶圆测温系统——半导体制造温度监控的核心技术

MICRO OLED 金属阳极像素制作工艺对晶圆 TTV 厚度的影响机制及测量优化

Imec将在300mm晶圆上制造双金属层的半镶嵌模组?

Imec将在300mm晶圆上制造双金属层的半镶嵌模组?

评论