手机、数码相机、MP3播放器和PDA等手持设备的设计工程师,正不断地面临着在降低整个系统成本的同时、又要以更小的体积提供更多功能的挑战。集成电路设计工程师通过在减少硅片空间大小的同时提高设备的速度和性能,以此来推动这一趋势。

为了使功能和芯片体积得到优化,IC设计工程师要不断地在他们的设计中使功能尺寸最小化。然而,要付出什么代价呢?IC功能尺寸的减少使得器件更易受到ESD电压的损害。这种趋势对终端产品的可靠性会产生不利的影响,并且会增加故障的可能性。因此,手持设备的设计工程师就要面对找到一种具有成本效益的ESD解决方案的挑战,这种方案能把电压箝位到更低水平,以便使那些采用了对ESD越来越敏感的IC的终端产品保持高可靠性。

ESD波形

以系统级的方法来定义典型的ESD事件所采用的最常见的波形,是以其亚纳秒上升时间和高电流电平(参见图1)为显著特征的IEC61000-4-2波形。这种波形的规范要求采用四级ESD量级。大部分设计工程师都要求把产品限定到最高级的8kV的接触放电或15kV的空气放电。当进行元器件级测试时,因为空气放电测试在这样的小型元器件上是不能重复的,接触放电测试则是最适合的测试方式。

ESD方面所需考虑因素

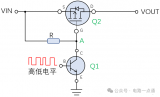

ESD保护器件的目的是把数千伏电压的ESD输入电压降低到所保护的IC所能承受的的安全电压,并能把电流从IC旁路。虽然所需ESD波形的输入电压和电流在过去的几年没有出现变化,但要求保护IC的安全电压电平却降低了。过去,IC设计在ESD防护方面更具鲁棒性,而且能够承受更高电压,因此,在选择能符合IEC61000-4-2第4级的要求的保护二极管时有充分的选择余地。而对于如今ESD更敏感的IC,设计工程师就必须不仅要确保保护器件能够符合IEC61000-4-2第4级标准,而且还要确保该器件能够将ESD脉冲钳制到足够低的电平,从而确保IC不受损坏。在为给定的应用选择最佳保护器件的时候,设计工程师们必须要考虑到ESD保护器件能够把ESD电压控制到多么低的电平。

选择最有效的保护方案

保护二极管的关键DC指标是击穿电压、漏电和电容。大部分数据页也会说明IEC61000-4-2的最大额定电压,该电压指的是二极管在该电压上不会被ESD冲击损坏。所存在的问题是,大部分数据页中没有任何针对像ESD这样的高频率、高瞬态电流的箝位电压方面的信息。可是要详细说明,要在IEC61000-4-2规范中硬性规定箝位电压不是一件简单的事情,这是因为该规范的初衷是用来检验系统是否合格,并且频率是如此高。要把这种规范来检验保护器件,关键的是不仅要检查保护二极管是否合格/不合格,还要检查它能把ESD电压箝位到多么低的电平。

比较保护二极管箝位电压的最好途径是采用一台示波器抓取保护二极管两端在ESD产生期间内的实际电压波形。在观察经受IEC61000-4-2标准测试的ESD保护器件的电压波形时,通常初始电压峰值之后紧随着第二峰值,并且最终电压将会稳定下来。初始峰值是由IEC61000-4-2波形的初始电流峰值和由测试电路中存在的电感所导致的过冲相结合所造成的。初始峰值的持续时间很短,因此限定了传输到IC的能量。图中曲线上显示了保护器件的箝位性能,其位于第一个过冲之后。应该重点关注第二个峰值,这是因为该峰值的持续时间较长,被测IC承受的能量将因此增加。在以下的讨论中,箝位电压被定义为第二峰值的最大电压。

罗姆的ESD保护二极管推荐

罗姆的BZX84B10VL齐纳二极管具有高可靠性和封装小的特点,适用于ESD保护电路。

审核编辑黄宇

-

二极管

+关注

关注

149文章

10453浏览量

179528 -

电路

+关注

关注

173文章

6086浏览量

178827 -

ESD

+关注

关注

50文章

2424浏览量

180406

发布评论请先 登录

ESD防护设计的核心准则

探索ESD562-Q1:汽车应用中的ESD保护解决方案

合科泰揭秘电路设计中的可制造性原则

HDMI接口的ESD器件选择(二):闩锁效应的防范及解除

扬杰科技分享如何通过硬件电路优化降低ESD干扰

【深度解析】硬件电路设计:如何确保嵌入式数据可靠性?

IGBT驱动与保护电路设计及 应用电路实例

电路板ESD保护优化指南

【干货】ESD如何选型

如何学好电路设计?(文末分享电路设计资料合集)

半导体芯片的ESD静电防护:原理、测试方法与保护电路设计

电路设计中如何防范ESD

电路设计中如何防范ESD

评论