在功率变换器应用中,宽带隙(WBG)技术日益成为传统硅晶体管的替代产品。在某些细分市场的应用场景中,提升效率极限一或两个百分点依然关系重大,变换器功率密度的提高可以提供更多应用优势,在这种情况下采用基于氮化镓(GaN)晶体管的解决方案意义重大。与传统硅器件相类似,GaN晶体管单位裸片面积同样受实际生产工艺限制,单个器件的电流处理能力存在上限。为了增大输出功率,并联配置晶体管已成为设计工程师可以考虑的选项之一。应用晶体管并联技术在最大限度提升变换器输出功率的同时,也带来了电路设计层面的挑战。

并联晶体管的设计挑战

在应用晶体管并联技术时,首先需要考虑的是并联晶体管的通态电阻(RDS(on))。理想情况下,所选器件应均匀匹配,以确保静态电流在并联晶体管之间平均分配。其次,在动态开关过程中,如果晶体管栅极缺乏对称性,不仅会导致流经晶体管的电流分配不平衡,动态电流和电路寄生参数将会导致高频振荡电压。如果这些无法解决这些问题,将可能导致晶体管损坏。

尽管传统硅晶体管的并联配置技术已经十分成熟,但对于GaN器件并联技术研究还鲜有涉及。考虑到GaN器件驱动的特殊性以及其高速开关特性,我们将首先从GaN器件驱动电路设计开始介绍。

正确设计驱动电路

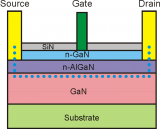

诸如英飞凌科技 CoolGaN™600 V HEMT之类的GaN晶体管采用了栅极p型掺杂工艺,这会将器件的栅极阈值电压转换为很低的正向电压(1.0V~1.5V)。该结构中栅极形成的pn结正向电压(VF)约为3.0 V,电阻为几欧姆,与栅极电容CG并联。因此,CoolGaN™晶体管驱动电路与传统硅晶体管存在很大差异。栅极驱动过程中,一旦达到Miller平台,栅极电压就被钳位到接近VF的值,这意味着在硬开关应用中需要负电压来关断晶体管。同时,CoolGaN™ 器件在稳态导通状态和开关瞬态所需驱动也有所不同。

针对CoolGaN™晶体管特性设计的栅极驱动电路如图1所示。为确保栅极驱动正常,驱动电压VS的峰值需要超过VF的两倍(通常使用8V~10V),通过Ron提供了一条瞬态低阻抗高速AC路径来为Con和CGS充电,然后通过RSS形成一条并联的稳态DC路径。因此,栅极导通瞬态电流由Ron决定,而RSS决定稳态二极管电流。

在栅极关断时,CGS和Con中的电荷将快速达到平衡。此处必须确保Con大于CGS,以确保稳态的电荷差使栅极电压VG变为负值,从而在硬开关应用中关断晶体管。

图1:E模式GaN HEMT等效电路(左)和建议的驱动方案(右)。

当并联配置CoolGaN™晶体管时,可使用相同参数的RC驱动网络分别连接每个并联晶体管,再同时与传统硅晶体管的标准驱动器连接。并联的几个晶体管只需要一个隔离型驱动器,例如隔离型EiceDRIVER™1EDI20N12AF,使用源极(OUT +)和漏极(OUT-)输出分别实现晶体管的导通和关断。当使用12V隔离电源作为栅极驱动器供电时,EiceDRIVER™内部会将其分为正向驱动电压和-2.5V反向关断电压这样可确保驱动电压不超过晶体管栅极阈值,并大限度减小反向导通损耗。即使在低占空比情况下,EiceDRIVER™也可以保持良好的栅极电压调节特性,从而阻止RC驱动网络失压。

电流旁路对GaN晶体管并联配置的影响

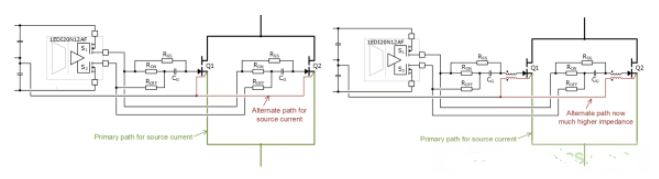

即使每个晶体管都配置独立的RC驱动网络,并联晶体管的源极电流仍然存在部分共享路径,这将会对栅极驱动产生影响(见图2)。理想情况下,所有源极电流都将从漏极流至晶体管源极,但不可避免的一种情况是,部分源极电流会从开尔文源极(Kelvin source)流出。如果这些路径的阻抗和PCB布线不同,则并联的CoolGaN™晶体管栅极回路中的VGS电压可能会有所不同,小至几毫伏的栅极电压差异会导致几安培的不平衡源极电流分流,导致并联晶体管之间在开关瞬态产生剧烈振荡。

图2:在CoolGaN™并联操作中,开尔文源极路径中的高阻抗可防止发生严重的振荡。

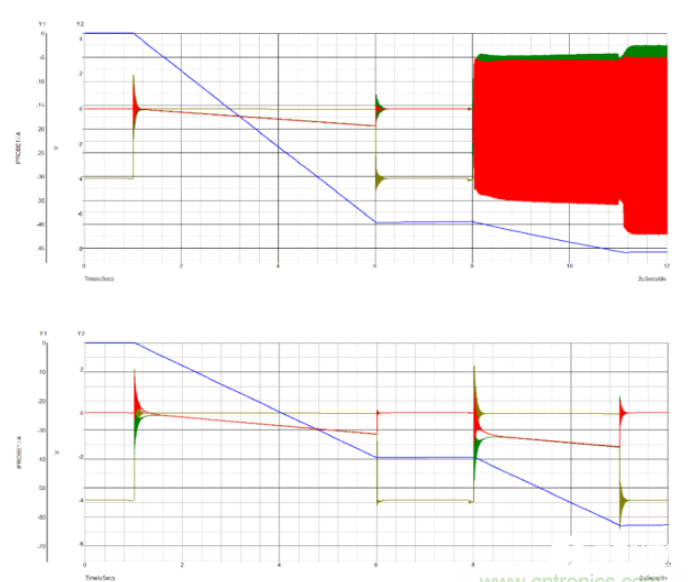

共享驱动电流路径问题可以通过在开尔文源极路径中引入高阻抗共模(CM)电感解决。将共模电感器和一个1Ω电阻器配置在栅极和相应的Kelvin源极驱动器返回路径之间,栅极驱动器环路中将呈现很小的漏感,而并联晶体管的栅极共享路径中将由于两个共模电感的存在呈现高阻抗。选择共模电感需要避免对栅极驱动器的驱动能力产生影响,图3所示的SIMetrix仿真结果清楚显示了共模电感对共享驱动电流路径问题的抑制。

图3:仿真结果显示在没有共模电感(上)和加入共模电感(下)情况下开关40A电流。

PCB优化设计

在并联配置晶体管时,另一个普遍关注的问题是PCB中寄生电感和电容(器件布局、PCB布线、多层PCB布局),以及所用器件中寄生电感和电容的影响。对于CoolGaN™晶体管,关键问题是由VGS阈值范围和晶体管之间RDS(on)差异造成的影响。通过仿真,在SIMetrix中对CoolGaN™晶体管进行建模分析。仿真模型使用0.9V~1.6V阈值电压和55mΩ~70mΩ的RDS(on)值的CoolGaN™并联,同时对寄生电感和PCB寄生电容电容进行建模。分析结果表明,并联晶体管分流不均仅与所用晶体管之间的RDS(on)差异有关。在必要情况下,可以通过进行严格器件匹配来解决。如前文所述,使用CM电感可以避免破坏性的持续电压振荡。然而,遵循良好的元器件布局和PCB布线也是一个关键因素。电源环路和栅极驱动环路必须保持较小且对称,同时还要确保开关节点的寄生电容尽可能低。

积累实践经验

了解挑战及其解决方案的最佳方法是在实验室进行试验。为此,英飞凌开发了并联半桥评估板,其中应用了四个70mΩ IGOT60R070D1 CoolGaN™晶体管。该评估板遵循了以上介绍的设计准则,可以为评估和设计开发提供了一个良好的基础。评估版还提供了大量测试点。需要注意的重要一点是,对于某些测量点,需要高带宽隔离差分探头,并且在使用前矫正以确保准确的波形采集。

通过连接外置电感,该评估板可用于降压或升压电路(buck circuit or boost circuit)测试、双脉冲(double pulse test)测试以及脉冲宽度调制(PWM)运行。评估板还适用于数千瓦功率等级或高开关频率至1MHz的软开关和硬开关应用。模块化设计简化了测试配置流程,除了板载100µF,450V的大容量电容之外,额外的连接器允许再增加一个母线电容。 该组件与另外两个高频旁路电容器一起,确定了450V的输出或母线电压等级。在安装合适的散热器、导热片和风扇的情况下,评估板可在硬开关或软开关下以高达28A的连续电流,或峰值电流70A运行。 死区时间电路中的电位计也包括在评估板内,可通过RC网络实现延迟接通,以及通过二极管实现无延迟关断。

图4:并联半桥CoolGaN™评估平台。

总结

尽管硅晶体管并联配置已经十分成熟,GaN晶体管并联配置对于许多设计工程师而言仍然存在挑战,采用不同于传统硅器件的栅极驱动电路是并联配置的关键。由此开始,GaN晶体管并联配置与硅晶体管相类似,但不完全相同。为保证并联晶体管均流,需要在设计阶段对PCB布线和器件选型进行优化。针对旁路电流对并联GaN晶体管的影响,在栅极和开尔文源极路径中加入合适的共模电感是必不可少的,这将有助于最大限度减小电压震荡。

编辑:hfy

-

晶体管

+关注

关注

78文章

10443浏览量

148696 -

GaN器件

+关注

关注

1文章

52浏览量

8301 -

硅晶体管

+关注

关注

0文章

10浏览量

3526

发布评论请先 登录

晶体管达林顿光耦:核心特性驱动的技术优势与应用价值

氮化镓GaN FET/GaN HEMT 功率驱动电路选型表

CGH40006P射频晶体管

基于偏置电阻晶体管(BRT)的数字晶体管系列MUN2231等产品解析

探索NSV1C300CT:高性能PNP晶体管的卓越之选

MUN5136数字晶体管技术解析与应用指南

电压选择晶体管应用电路第二期

多值电场型电压选择晶体管结构

Nexperia推出采用铜夹片封装的双极性晶体管

GAN功率器件在机器人上的应用实践

深度探讨GaN器件驱动电路并联晶体管设计方案

深度探讨GaN器件驱动电路并联晶体管设计方案

评论