作者:小鱼,Xilinx学术合作

一.概述

在文章《Verilog HDL入门思路梳理》我们说过应该如何去学习Verilog HDL描述。然而第一步,我们需要知道Verilog有哪些语法,它是否可以综合,可以用这个语法来描述什么逻辑功能电路呢?

其实Xilinx已经贴心地准备好了答案,还给你准备了一堆参考实例。

二. Verilog行为级描述

资料名称“Vivado Design Suite User Guide - Synthesis - UG901 (v2018.2) June 6, 2018”。(注:大家可以在Xilinx官网,或者安装DocNav(Xilinx Documentation Navigator) 并在这里面找到这份资料。)

资料的第7章《Verilog Language Support》就是介绍在Vivado里,可综合的Verilog描述语法以及描述方式。重点就是Verilog行为级描述(Behavioral Verilog)。

在了解了Vivado支持的可综合的Verilog描述语法之后,我们就可以通过实例设计来加深理解。从哪里可以找到这些实例设计呢?在Vivado里面就有,下面告诉你们如何找到它们。

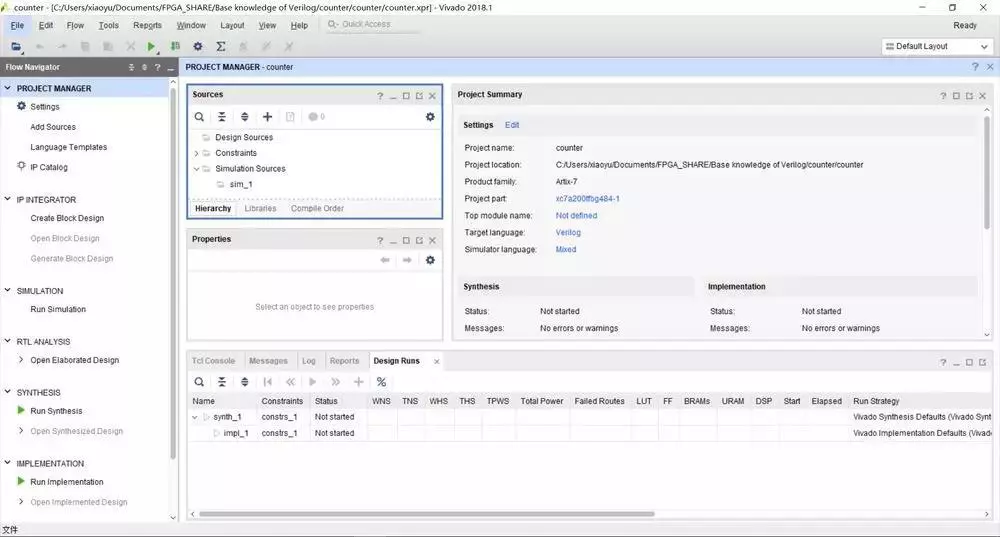

1.打开Vivado工具,先新建一个工程。然后进入下页面。

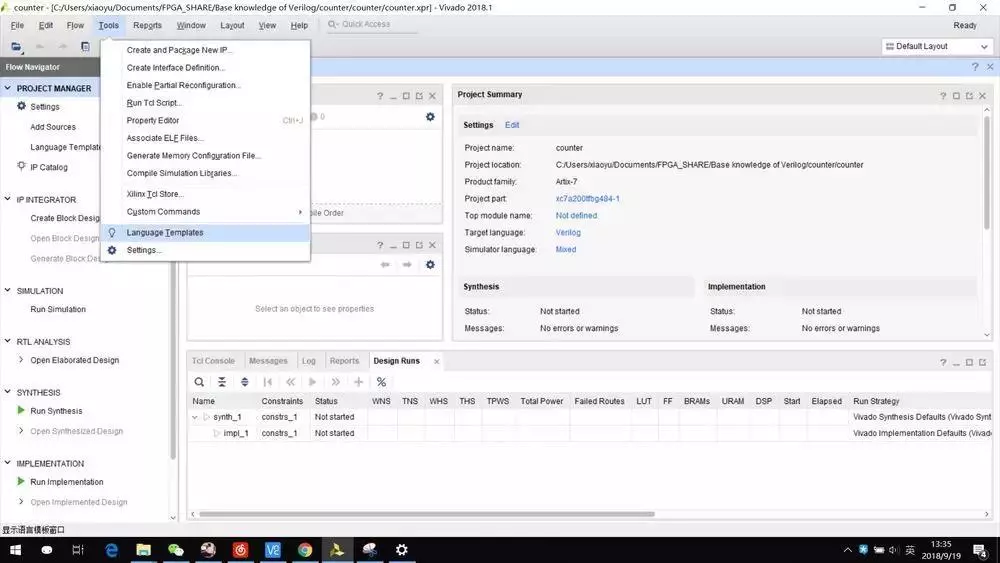

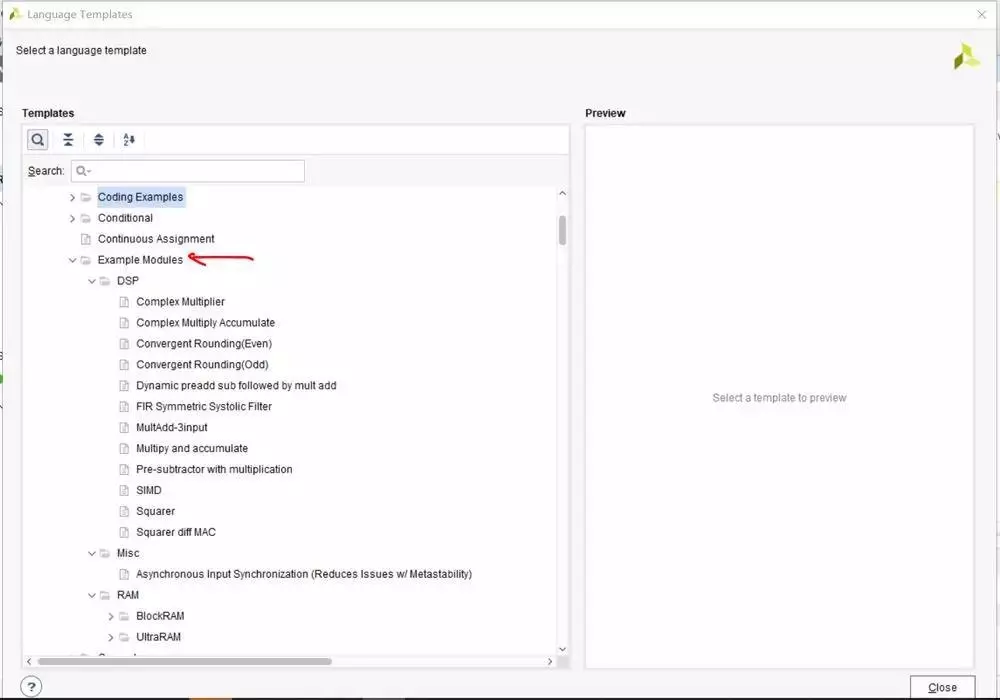

2. 在界面最上面一行菜单栏找到 “Tools”,点击 Tools-> Language Templates

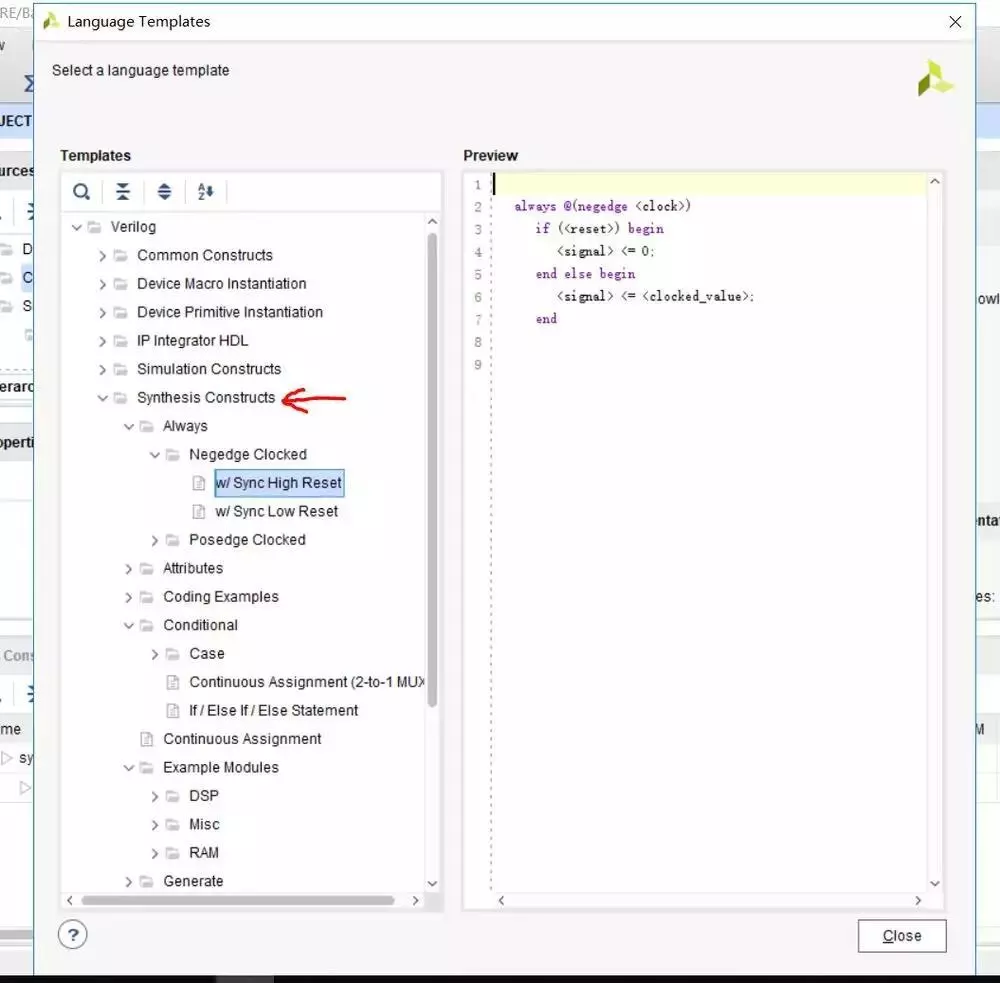

3. 将下图中的Verilog栏展开,在Synthesis Constructs栏就是我们可综合的常见Verilog描述。可以看到 Always ,Conditional里的case,条件选择赋值语句,if-else等常见的语法模型他都列出来了。在Coding Example里面有一些基础的电路模块的Verilog描述示例。

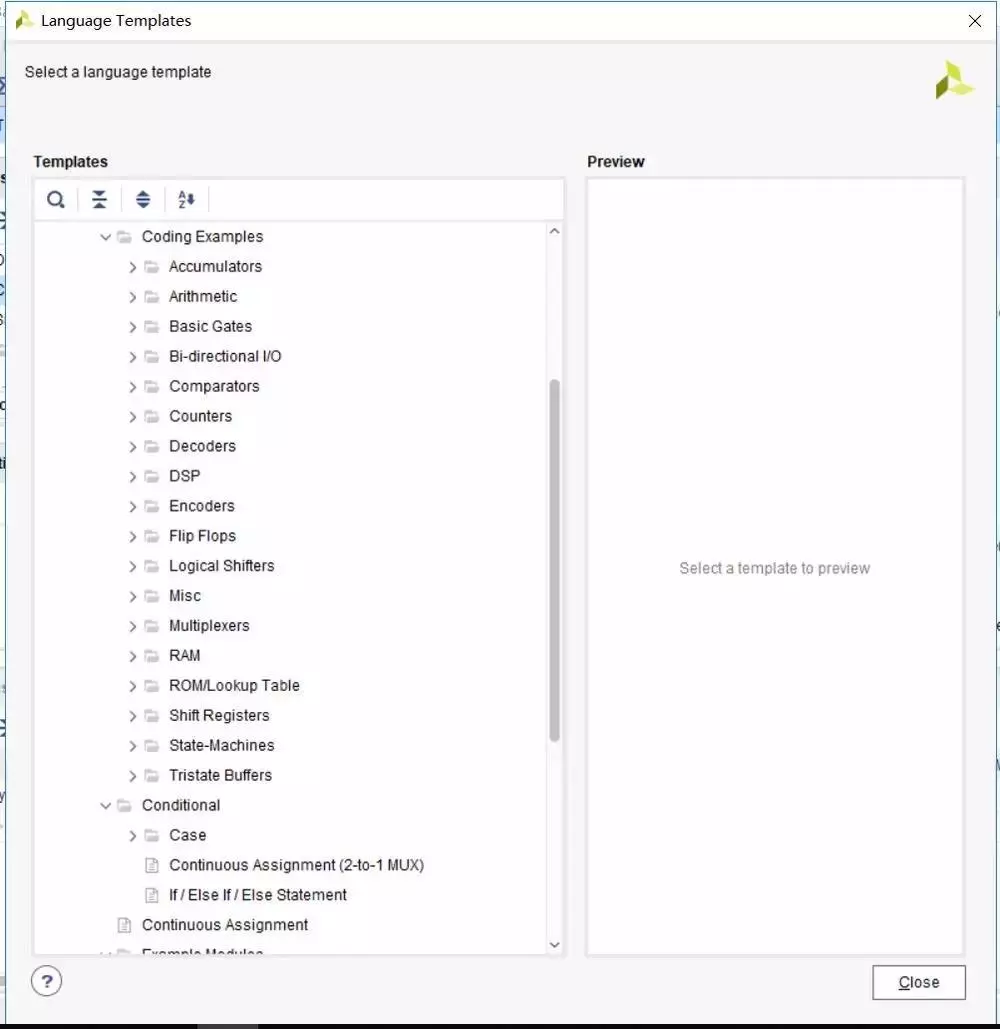

4. 展开Coding Example,可看到基础的电路,如累加器,基础算术电路,逻辑门,输入输出端口,比较器,计数器,解码器,常见的数字信号处理电路,译码器,寄存器(flip flops),逻辑移位器,Misc(有七段式数码管驱动,同步电路,防抖电路, 开漏输出端口,脉冲调制电路),多路选择器,RAM,ROM,移位寄存器,状态机,三态缓冲器等等的Verilog描述示例。

对于初学者可以好好利用这些资料。把上面这些示例模板和示例设计学习并仿真一遍。主要是将Verilog描述与电路对应起来,在Vivado里面可以使用Schematic,把Verilog描述的电路原理图显示出来。

编辑:hfy

-

Verilog

+关注

关注

30文章

1370浏览量

114167 -

Vivado

+关注

关注

19文章

848浏览量

70495

发布评论请先 登录

语法纠错和testbench的自动生成

如何在vivado上基于二进制码对指令运行状态进行判断

在vivado上基于二进制码对指令运行状态进行判断

如何利用Verilog HDL在FPGA上实现SRAM的读写测试

verilog模块的调用、任务和函数

FPGA Verilog HDL语法之编译预处理

一文详解Verilog HDL

千兆网络PHY芯片RTL8211E的实践应用

浅谈Verilog和VHDL的区别

通过实例设计来加深Verilog描述语法理解

通过实例设计来加深Verilog描述语法理解

评论