在群里交流提问的时候,大家总是惊讶并疑惑:为什么我要选择 VHDL入门?因为好像 99% 搞 FPGA 开发的人都在用 Verilog。我的选择,是通过网上搜索的讨论而做出的,为了留存,我这里水一篇。从长期来看,两个语言大概率都要学一下;但是从初学角度而言,总要选择一个入门语言。根据网上的信息,总结对比结论:Verilog 的优势:1. Verilog 语法接近C,学习容易;VHDL上手困难,语法繁琐。2. Verilog 是弱类型;VHDL 是强类型。2. 美国的公司主要使用 Verilog,使用广泛,工作岗位更多;美国的军工和欧洲用 VHDL 更多一些。3. 学会了 Verilog 之后,转向 SystemVerilog 更容易,这个是很多人(包括UP主老石的观点)更有前途的 HDL。4. 因为用的人多,所以学习的资料,教学书籍使用 Verilog 的明显比 VHDL 更多。VHDL的优势:1. VHDL 是强类型; Verilog 是弱类型。强类型是缺点是因为增加了代码编写的复杂度;是优势是因为更不容易写错误的代码。2. VHDL 是非常强的确定性,而 Verilog 有时候是非确定性的。(https://www.sigasi.com/opinion/jan/verilogs-major-flaw/)3. VHDL 提供更多的类型定义(同时导致代码繁琐),verilog 只提供少量的类型。4. 学习 VHDL,更能学习数字电路的基础(而学 verilog 只是可以更快的点灯,这是下面一个人的观点)5. 因为VHDL的强类型和确定性,在分析和综合过程中,VHDL 能检查出更多的逻辑错误。 Verilog 更容易接受带有潜在问题的代码。所以我选择 VHDL 的原因是:我是初学者,需要编译器给我更多的指导避免潜在的错误;需要同步学习更多数字电路逻辑的知识;使得代码更具结构性;编写代码浪费的时间其实并不是最重要的,测试和调试代码逻辑才是更耗时的部分,所以如果可以通过增加一些编写的时间,而大幅缩小测试调试的时间,是绝对值得的(如同 Rust 对 C/C++)。观点截图

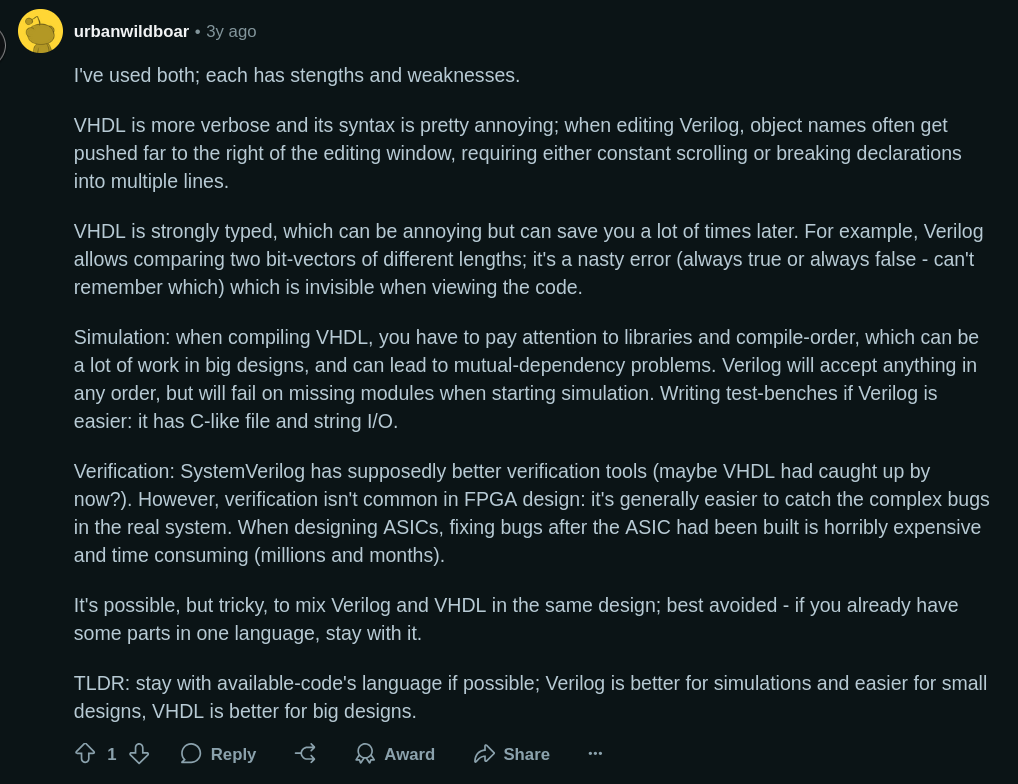

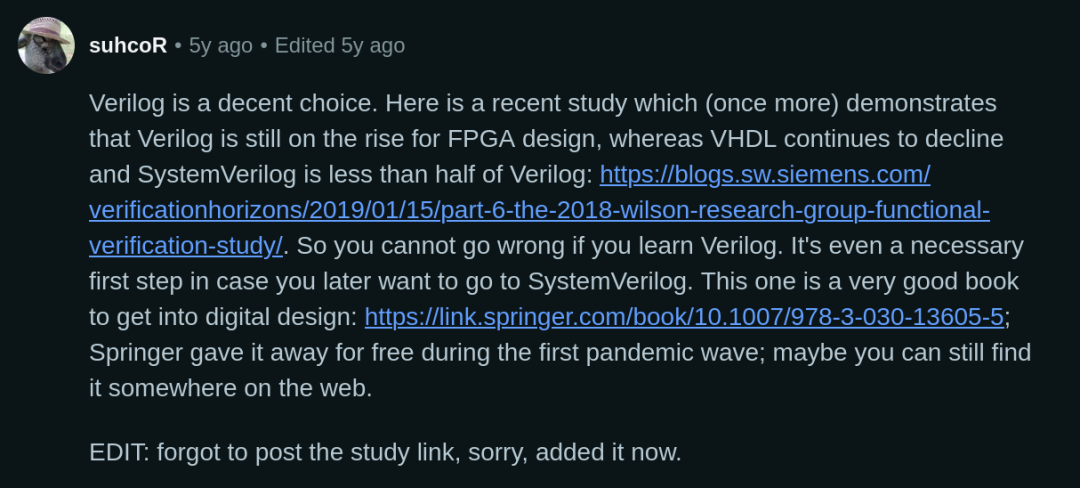

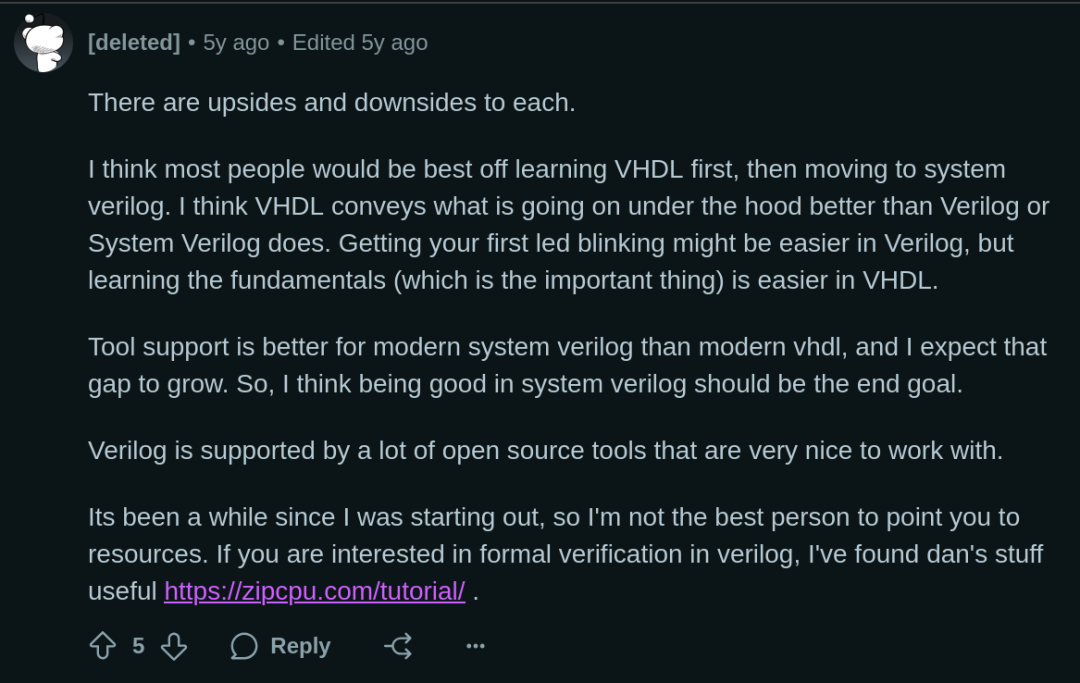

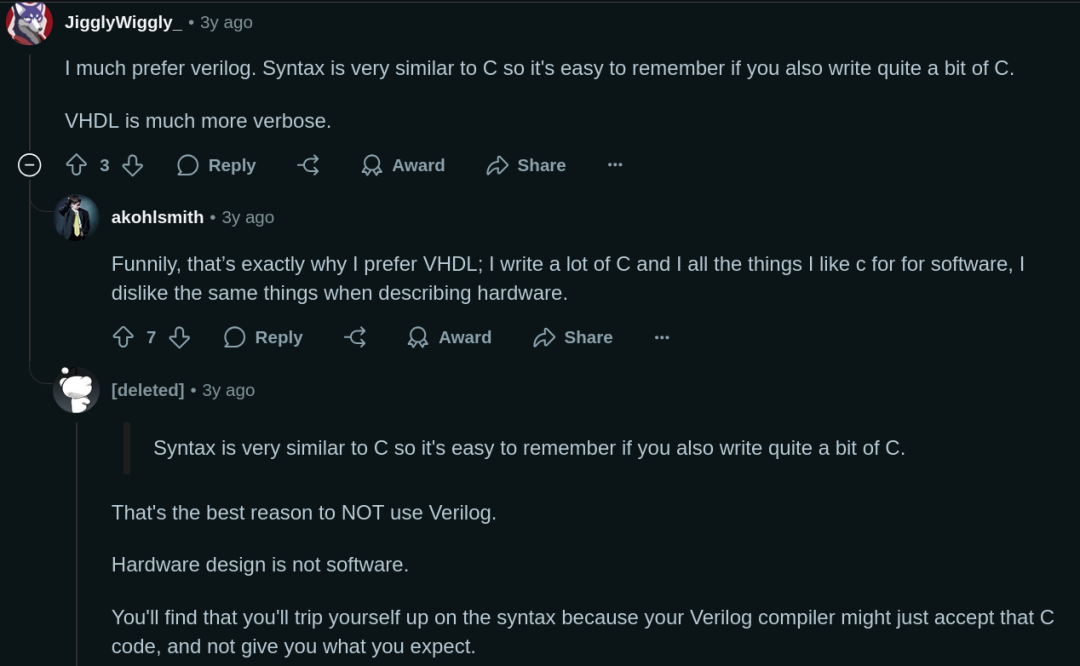

支持 Verilog 的观点

支持 Verilog 的观点

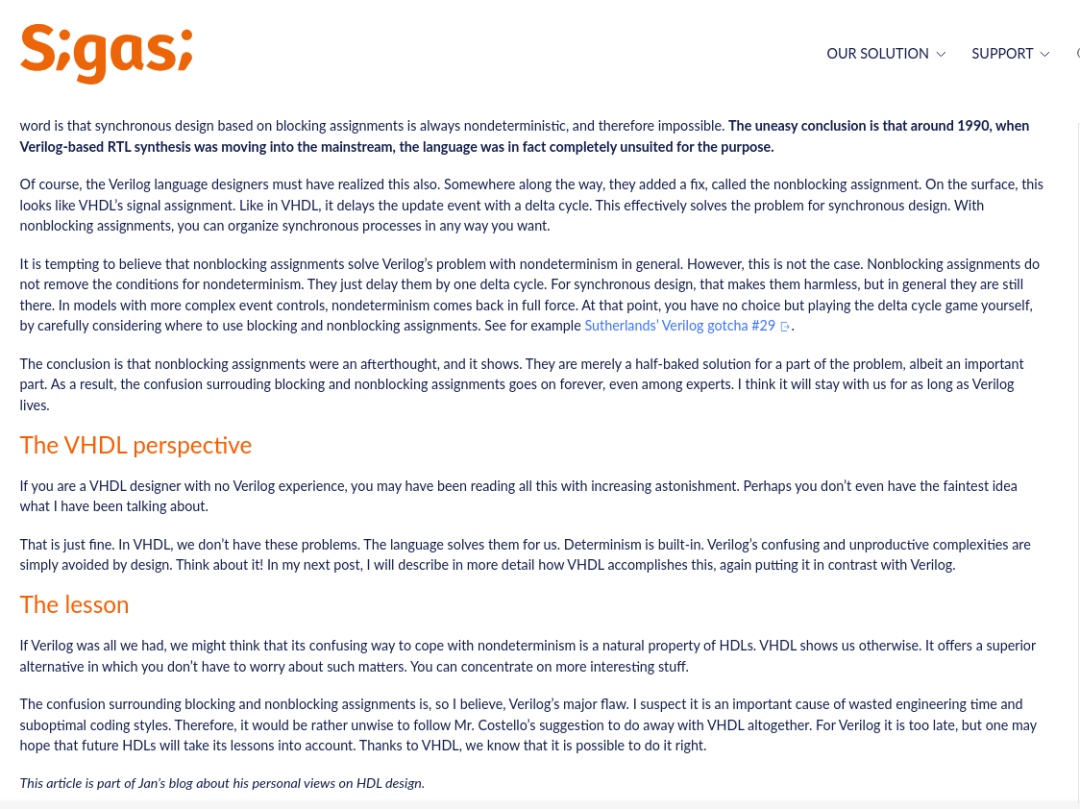

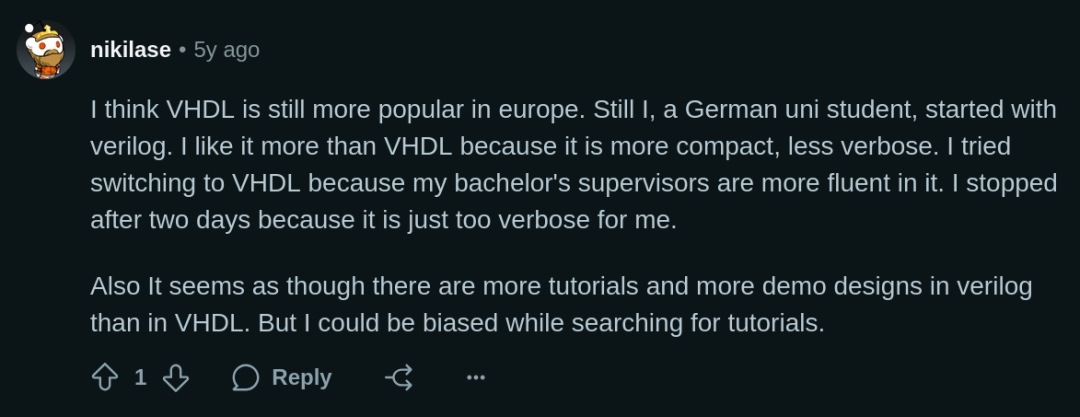

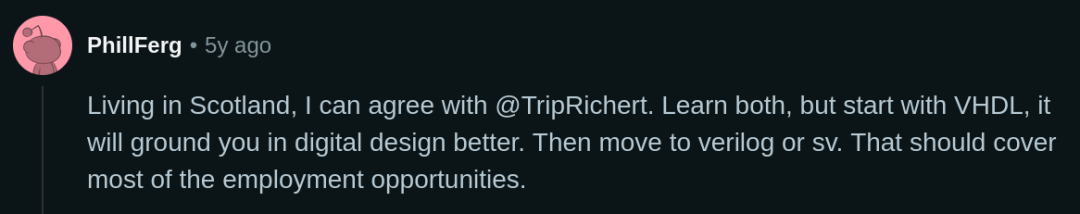

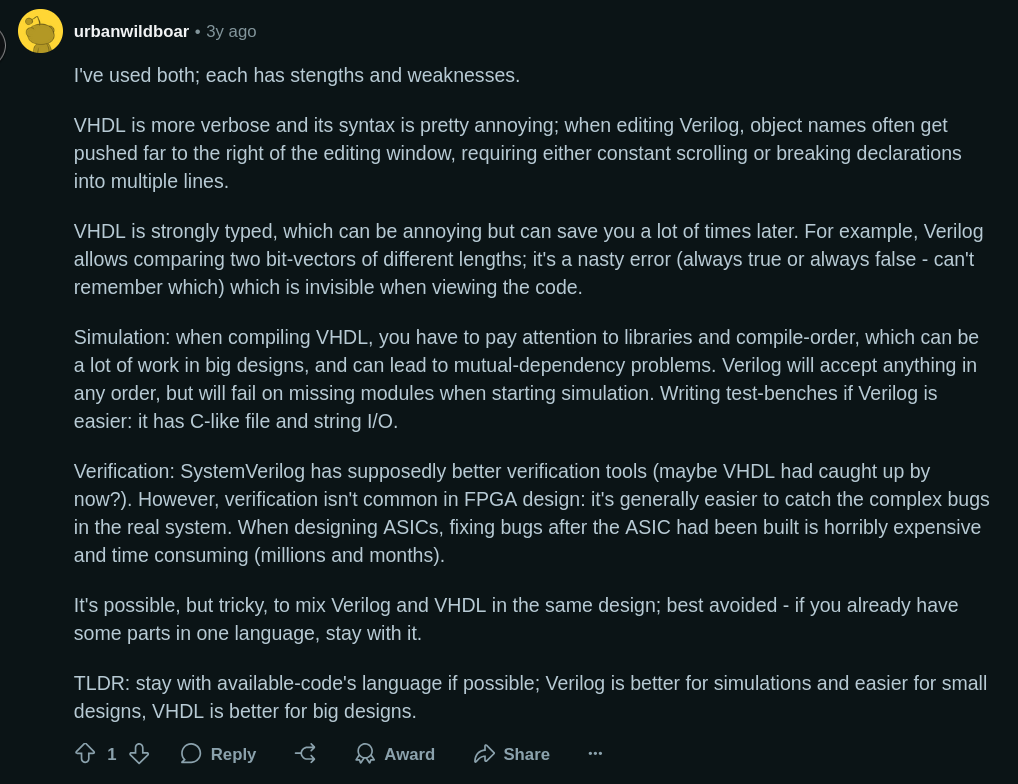

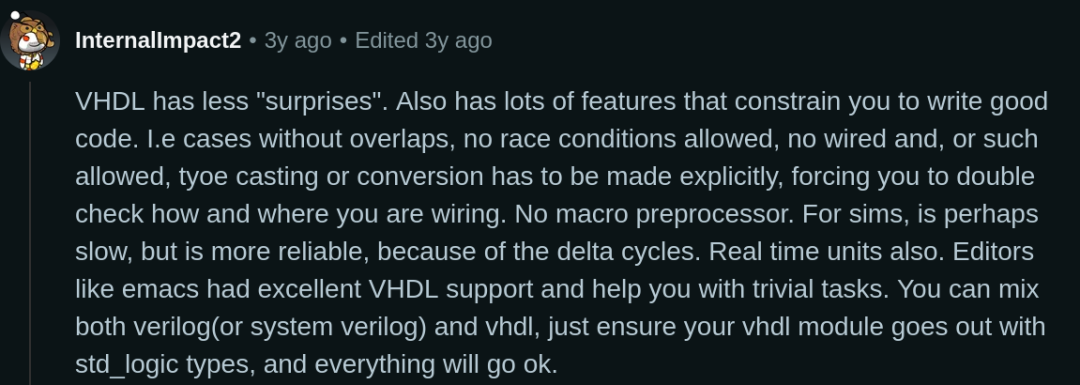

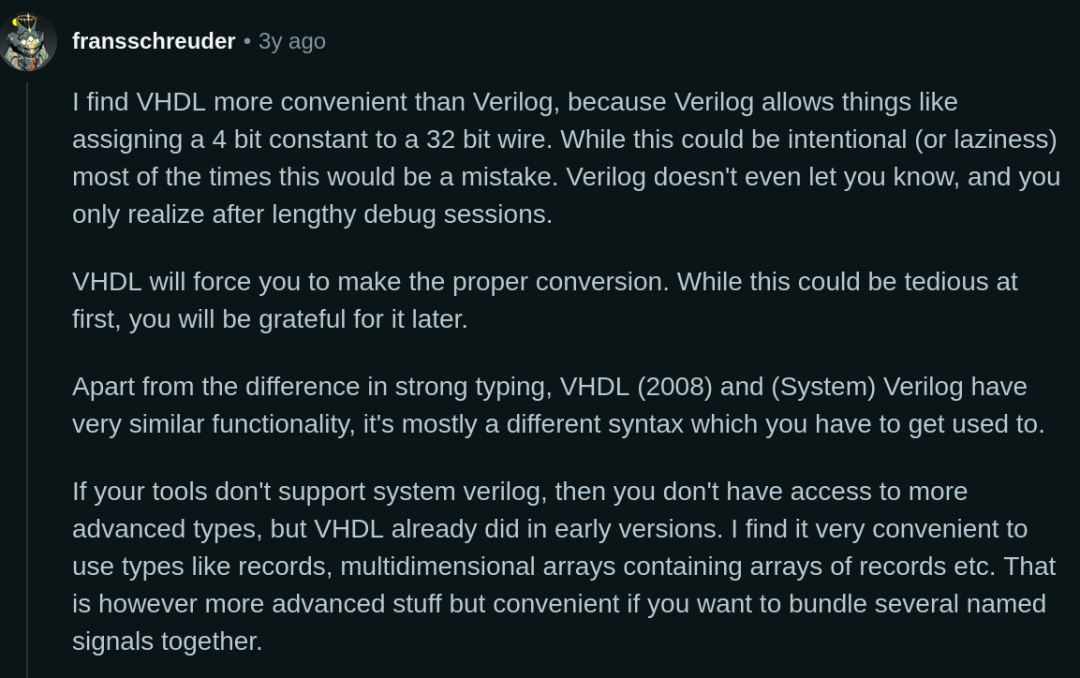

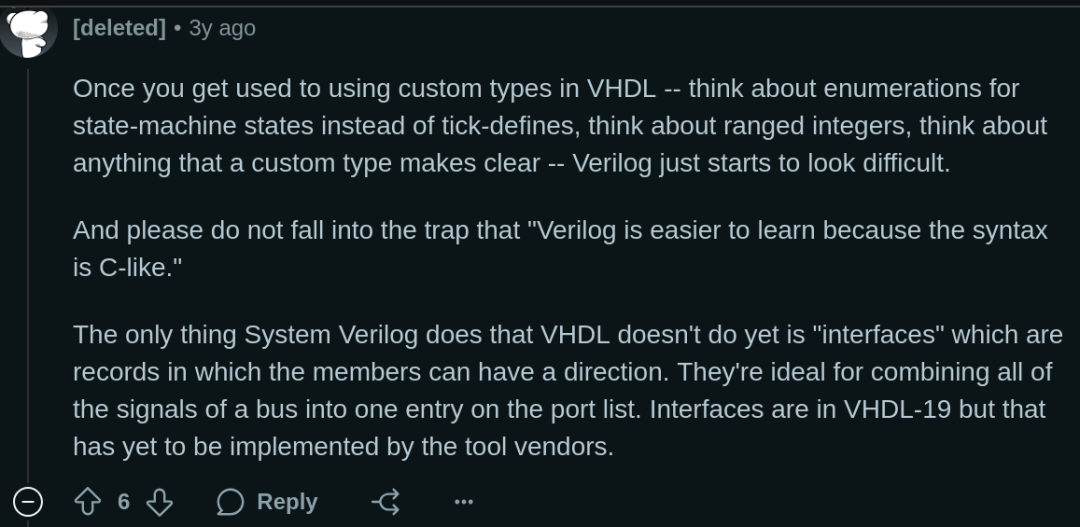

支持 VHDL 的观点

支持 VHDL 的观点

https://vhdlwhiz.com/should-i-learn-vhdl-if-verilog-is-becoming-more-popular/

https://www.sigasi.com/opinion/jan/verilogs-major-flaw/

https://digilent.com/blog/verilog-vs-vhdl/?srsltid=AfmBOopW22oVlEJQsfh9kTQePkD-7TUmSL58-S9MFdGj_i25Z1Kb20I3

https://www.fpga4student.com/2017/08/verilog-vs-vhdl-explain-by-example.html

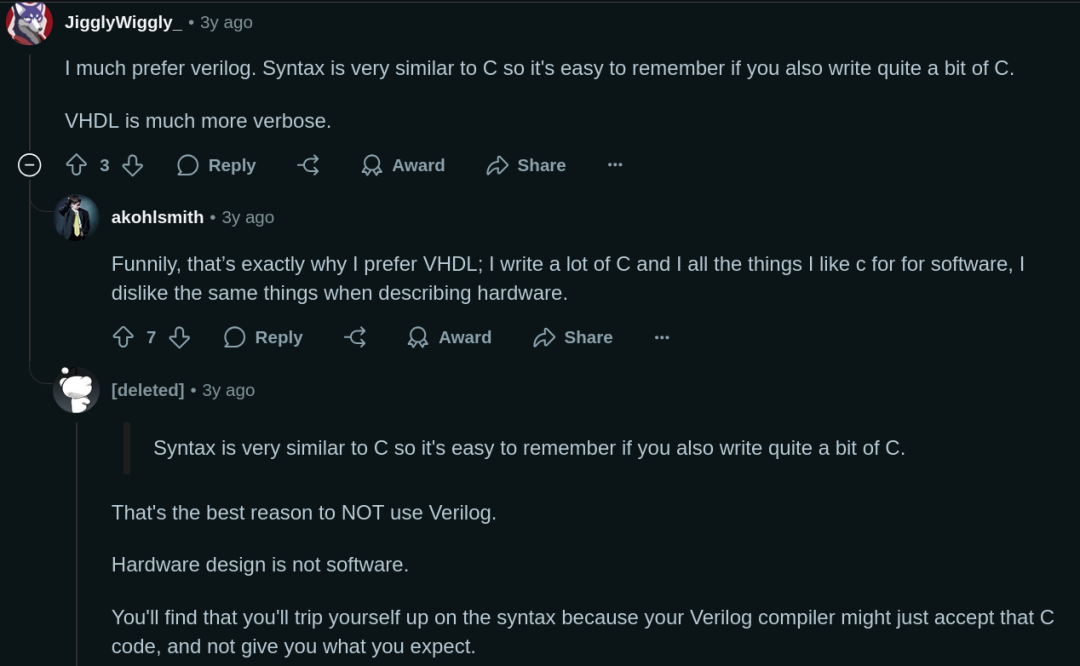

支持 Verilog 的观点

支持 Verilog 的观点

支持 VHDL 的观点

支持 VHDL 的观点

https://www.reddit.com/r/FPGA/comments/upcaj5/verilog_vs_vhdl/

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

vhdl

+关注

关注

30文章

822浏览量

131903 -

KiCAD

+关注

关注

6文章

331浏览量

10538

发布评论请先 登录

相关推荐

热点推荐

从架构到驱动:这三本经典书,承包了我的嵌入式Linux入门与进阶

作为一个深耕嵌入式领域的开发者,书架上总有几本“压箱底” 的书 —— 它们既是新手入门的灯塔,也是老手复盘的手册。今天想和大家聊聊几本经典的书,《ARM64 体系结构编程与实践》《鸟哥的 Linux

FPGA 入门必看:Verilog 与 VHDL 编程基础解析!

很多开发者第一次接触FPGA,都会有同样的疑问:FPGA是硬件,不是软件,怎么写程序?答案就是用硬件描述语言(HDL),最常用的就是Verilog和VHDL。今天,我们就带你入门,搞清楚FPGA编程

LAT1218 如何选择和设置外部晶体适配 BlueNRG-X

鉴于经常有客户对如何选择外部低速晶体,如何测试外部 32khz 时钟,如何直接使用外部32khz 信号源 以及 如何选择外部高速晶体,如何测试和校准频偏存在诸多困惑,我整理了该文档以备解惑用。

发表于 01-09 10:52

•0次下载

学习物联网怎么入门?

景等。同时,学习物联网的基本技术,如传感器技术、通信技术、云计算等,也是非常重要的。

其次,选择适合自己的学习方式也是入门学习物联网的重要一步。学习物联网的方式多种多样,可以通过网络搜索和学习物联网

发表于 10-14 10:34

Redis Sentinel和Cluster模式如何选择

在我十年的运维生涯中,见过太多团队在Redis集群方案选择上踩坑。有的团队盲目追求"高大上"的Cluster模式,结果运维复杂度爆表;有的团队死守Sentinel不放,最后扩展性成了瓶颈。今天,我想通过这篇万字长文,把

【PZ7020-StarLite 入门级开发板】——FPGA 开发的理想起点,入门与工业场景的双重优选

技术解决方案十余年,推出的 PZ7020-StarLite 开发板,以精准的入门级定位、完备的功能配置与友好的开发体验,成为工程师入门阶段的最优选择。

我该如何选择直线电机?

一、直线电机选择的核心考量因素 直线电机作为连接机械结构与精密控制的关键部件,其选型需结合应用场景的实际需求,综合评估多维度性能指标。首先是精度特性,包括定位精度与重复定位精度,不同行业差异显著

DSP从入门到精通全集

这是一本循序渐进介绍DSP的书籍,从DSP的入门知识介绍到DPS的硬件,接口,应用,从DSP的ADC/DAC到数字滤波器处理。本文除了对DSP的各种软硬件知识进行介绍后,还结合实际,接受了对应

发表于 07-12 14:36

家具别急着换新!如何使用树莓派让我的“傻瓜”设备变得更智能!

通信,我选择了HomeAssistant作为解决方案,同时还为智能家居项目配备了一些配件。此外,我不想拆开这些电子设备并在里面焊接芯片来让它们变得智能。相反,我选

为什么我选择VHDL入门

为什么我选择VHDL入门

评论