CMOS电路因其在在功耗、抗干扰能力方面具有不可替代的优势,以及在设计及制造方面具有简单易集成的优点而得到广泛应用。如今,在大规模、超大规模集成电路特别是数字电路中早已普遍采用CMOS工艺来来进行设计与制造。

一、CMOS门电路设计规则

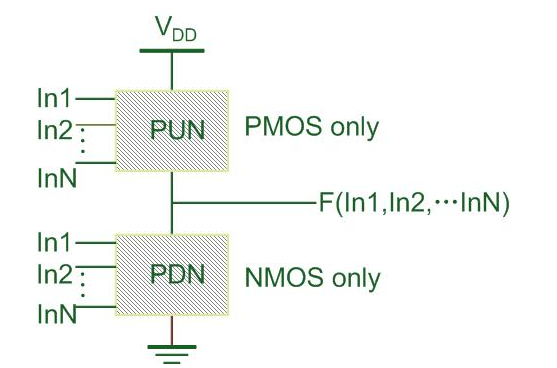

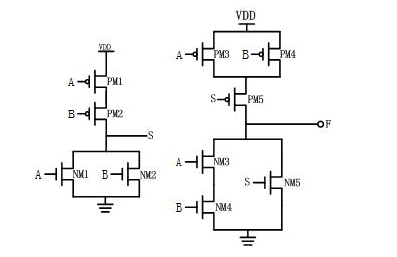

静态的CMOS电路的设计有着一定的规则,而正是这些规则使得其电路的设计变得非常简单。如图所示,COMS电路中最主要的部分是上拉网络PUN(Pull Up Net)和下拉网络PDN(Pull Down Net),这两个网络内部结构是对称互补的,或者说是对偶的。所谓的对称互补,即是指下拉网络中全是NMOS,而上拉网络中全是PMOS,两者数量相同;并且,下拉网络中组成“与”逻辑的MOS管,在上拉网络中对应的为“或”逻辑,在下拉网络中组成“或”逻辑的MOS管,在上拉网络中对应的为“与”逻辑。由于互补,上拉网络与下拉网络不会同时导通。

由于结构是互补对称的,CMOS电路的功能可以由下拉网络或者上拉网络单独来确定。对于下拉网络,先根据各个NMOS的串并联关系列出表达式,最后整体取反一下(取反是因为下拉网络为真时输出是低电平0);对于上拉网络,先将各个输入取反,再根据各个PMOS的串并联关系写出表达式。其中,串联为与,并联为或。

设计的过程则刚好反过来,先根据功能确定逻辑表达式,再选择下拉网络或者上拉网络中的一个作为切入点,根据与或关系确定MOS管的串并联,将其中一个网络画出来,最后根据互补关系画出另外一个网络。

二、CMOS异或门的设计举例

下面以异或门为例,讨论一下CMOS异或门的设计方法以及其中的一些技巧。

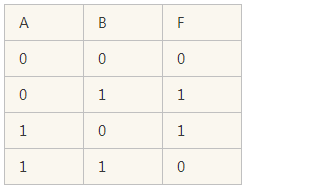

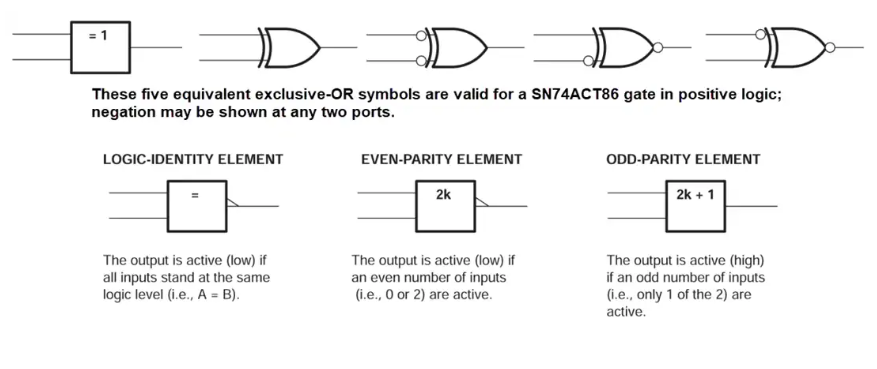

(1)确定功能。可以根据真值表、时序图等来确定。下表为异或门的真值表,当两输入信号相同时,输出为低电平;输入不同时,输出为高电平。

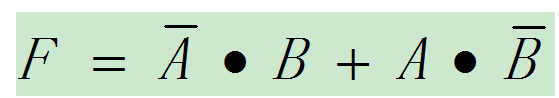

(2)确定逻辑表达式。异或门的逻辑表达式:

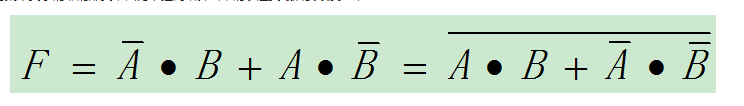

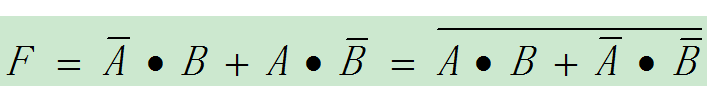

(3)画出下拉或上拉网络。以下拉网络为切入点,这时要先对表达式处理一下,变为某个式子的非的形式,因为下拉网络算出来的表达式最后要取反一下:

这样,就可以根据大非号下面的式子来搭建PDN电路:

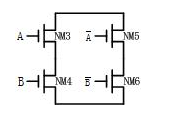

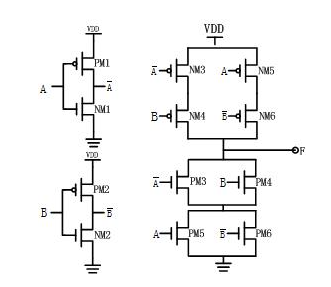

如图所示,由于A和B是与的关系,所以连接A和B的MOS管NM3和NM4要串联,和也是如此。由于与是或的关系,所以由NM3、NM4组成的串联和NM5和NM6组成的串联最后要并联在一起。至此下拉网络设计完成。

(4)根据互补关系确定另外一个网络。

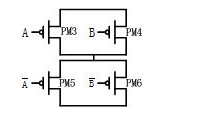

这一步就比较简单了,在PDN中A和B对应的MOS管是串联的,那么在PUN中就变成并联的,即PM3和PM4;和同样;最终将两个并联组合串联起来。

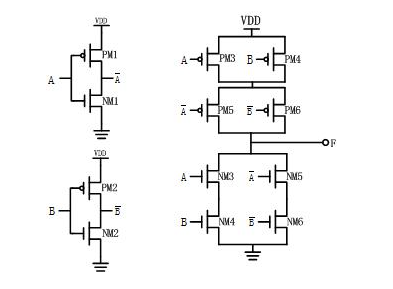

(5)将PDN和PUN组合起来,加上电源和地,如图:

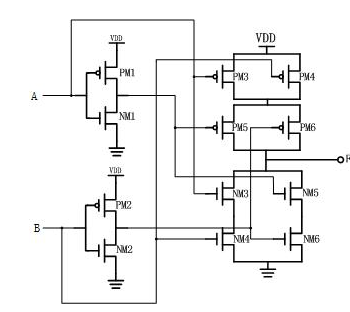

图中左侧是两个反相器,用于产生非信号。

为了便于分析,图中的连线都是用标号代替的,下图是一个完整的电路:

至此,一个完整的CMOS异或门电路设计完成。当然,后续还会有MOS管宽长比、掺杂等方面的设计,这些不在这里讨论。

三、另一种设计思路

以上是根据表达式:

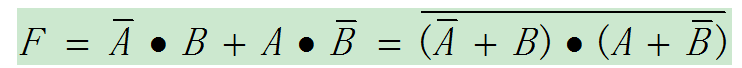

来进行设计的,对上式进行变换可以得到:

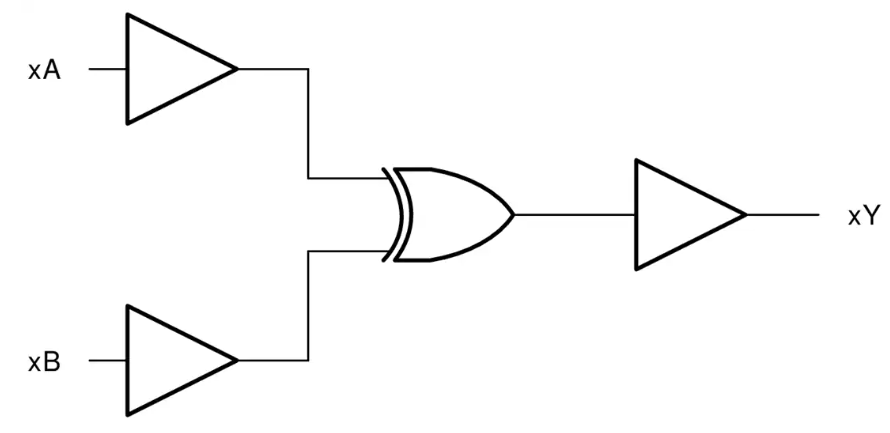

根据这个式子可以设计出与上例不同的电路:

该电路与前一种电路实现相同功能,只是在结构上PUN和PDN与前一种电路互换了一下,没有本质上的区别。

四、优化设计

下面介绍一种优化设计方法。

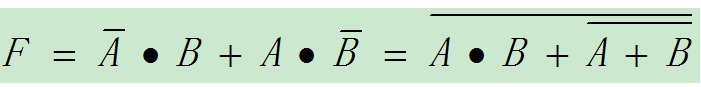

继续对异或门的逻辑表达式进行变换,得到:

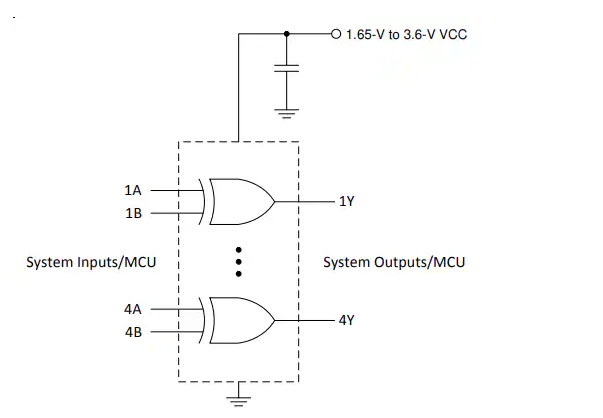

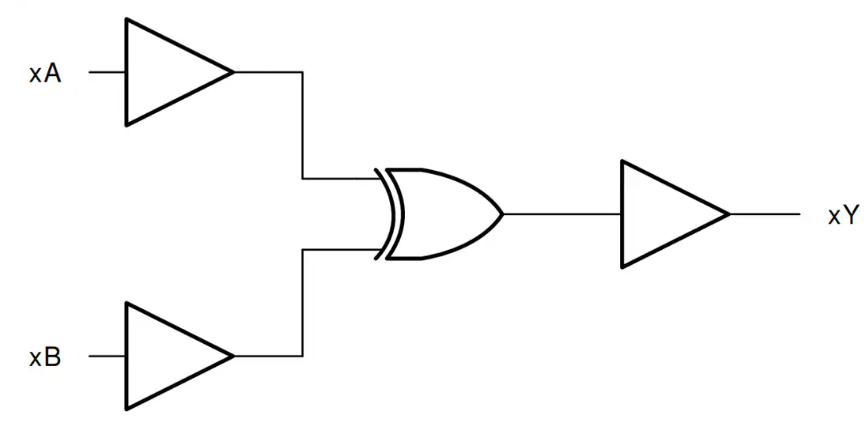

这里,将A与B的非作为一个整体,用一个独立的与非门来实现,电路图如图所示:

可以看到,前面两种电路都用了12个MOS管,而这个电路只用了10个MOS管就实现了异或门的功能。可别小看减下来的这两个MOS管,在大规模集成电路设计中,这种门电路的使用是非常普遍的,若是一个系统中能有百十个这样的门电路,那这种优化在减小芯片面积和降低成本方面将会为产品带来非常大的优势。

下面分析一下这样优化的原理。前两种电路中,逻辑表达式都包含了A、B、A非、B非四种信号,但是电路的原始输入只有A和B两种,因此要搭建产生A非和B非的电路,也就是搭建两个非门。而每个非门需要两个MOS管,所以产生A非和B非需要额外的四个MOS管。加上实现逻辑表达式功能的8个MOS管,一共12个。

而在第三种电路中,变化逻辑表达式消去了A非和B非,用A与B的非来代替,只需额外设计一个与非门,4个MOS管。由于A与B的非作为一个信号进行运算,相当于逻辑表达式中只有三个输入,一共需要6个管子,加起来一共10个。

也就是说,在逻辑表达式中,若果能够将信号合并使得输入端出现尽可能少的信号种类,那么就有可能减少整个门电路的MOS管个数。

编辑:hfy

-

CMOS

+关注

关注

58文章

6189浏览量

241582 -

MOS管

+关注

关注

110文章

2754浏览量

74933 -

异或门

+关注

关注

1文章

42浏览量

18245

发布评论请先 登录

单片机TTL和CMOS电平知识

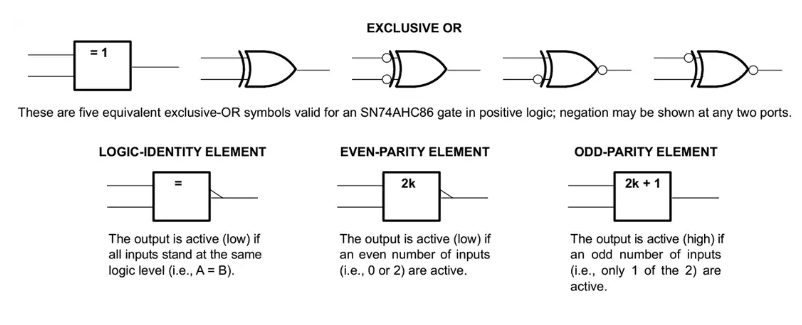

SN74AHC86四路双输入异或门技术解析与应用指南

SN74LV4T86-EP 四通道双输入异或门技术解析

Texas Instruments SN74LVC86A/SN74LVC86A-Q1四路2输入异或门数据手册

Texas Instruments SN74HC86四通道双输入异或门数据手册

Texas Instruments SN74ACT86/SN74ACT86-Q1双输入异或门特性/应用/框图

VirtualLab:CMOS传感器仿真

VirtualLab:CMOS传感器仿真

硬件基础篇——TTL与CMOS电平

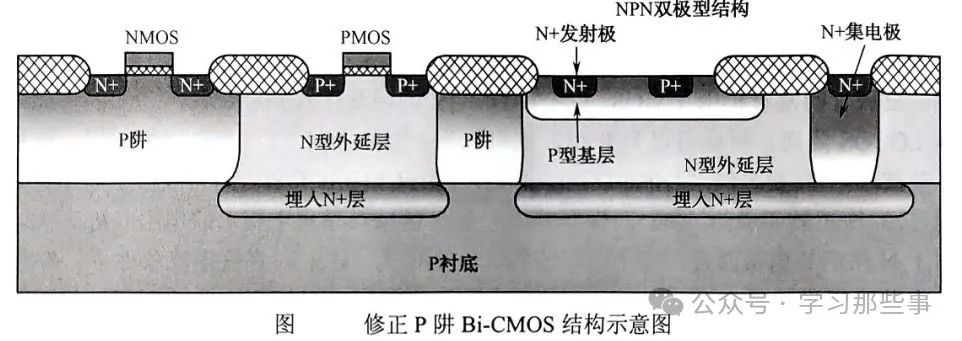

Bi-CMOS工艺解析

74HC86-Q100;74HCT86-Q100四路2输入异或门规格书

CMOS异或门的设计方法及技巧

CMOS异或门的设计方法及技巧

评论