忠告一

如果时序差的不多,在1NS以内,可以通过修改综合,布局布线选项来搞定,如果差的多,就得动代码。

忠告二

看下时序报告,挑一个时序最紧的路径,仔细看看是什么原因导致,先看逻辑级数是多少?是哪种电路有问题,乘法器 或者还是RAM接口数据 先弄清楚哪儿的问题

忠告三

搞时序优化的话 插入寄存器是王道 但也要看具体情况 不一定都得插寄存器,插入寄存器效果不明显的话,先检查一下寄存器插入的位置,如果寄存器不是在关键路径的中间插入而是在某一端的话,确实不大明显

忠告四

把关键路径找出来,看时序报告,看是什么原因导致频率上不去,如果是组合逻辑复杂,就优化逻辑或者复制逻辑,如果是DSP延迟大,就选多级流水的,只要想搞到150,就一定可以。

忠告五

看时序报告的时候,建议同时对照电路图一起看,这样最直观

忠告六

对照代码,自己把关键路径涉及部分的电路图画出来,然后根据时序要求,算一下要插多少寄存器,插哪儿合适

忠告七

32BIT的比较器,进位链有点长,可以分段比较,分成4个8BIT的数据段去比,或者你分成两段,先比高16,插寄存器,再比低16,时序很好,如果想深入些,就自己手写一个比较器,不要调库。

忠告八

多BIT的逻辑,时序上不去,通常都是进位链太长,通常做法就是打断进位链,建议看看计算方法或者数字算法之类的书,应该会有帮助

-

FPGA

+关注

关注

1664文章

22504浏览量

639304 -

寄存器

+关注

关注

31文章

5620浏览量

130423 -

比较器

+关注

关注

14文章

1936浏览量

112095

发布评论请先 登录

工程师高培解读XilinxVivadoFPGA设计进阶与AI自动编程

登临科技携手多家科技在八大领域落地典型AI应用案例

FPGA时序收敛的痛点与解决之道——从一次高速接口调试谈起

RGB时序灯条的工作原理讲解

CITE2026公布八大关键词,解构2026电子信息行业发展新态势

为什么在FPGA设计中使用MicroBlaze V处理器

数字IC/FPGA设计中的时序优化方法

FPGA实现基于SPI协议的Flash驱动控制芯片擦除

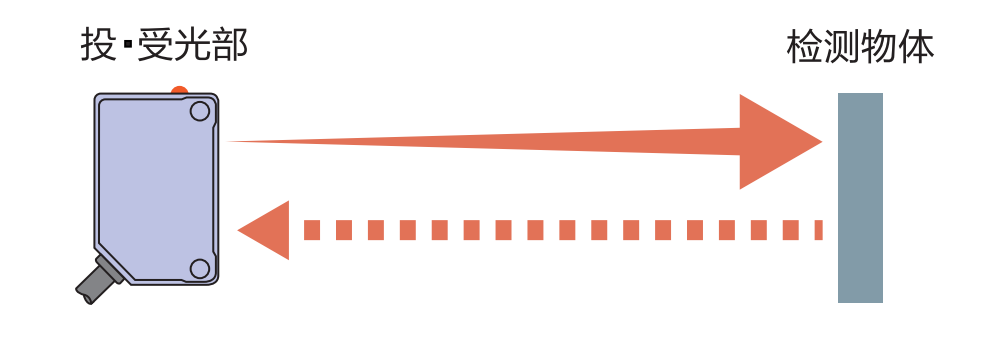

从原理到场景:工业光电传感器八大检测原理

FPGA测试DDR带宽跑不满的常见原因及分析方法

江智原创性老人八大关键时光点全覆盖 康养生态软件系统

关于FPGA时序八大忠告

关于FPGA时序八大忠告

评论