为保证信号传输质量、降低EMI干扰、通过相关的阻抗测试认证,需要对PCB关键信号进行阻抗匹配设计。本设计指南是综合常用计算参数、电视机产品信号特点、PCB Layout实际需求、SI9000软件计算、PCB供应商反馈信息等,而最终得出此推荐设计。适用于大部分PCB供应商的制程工艺标准和具有阻抗控制要求的PCB板设计。

一、 双面板阻抗设计

100欧姆差分阻抗推荐设计①、包地设计:线宽、间距 7/5/7 mil地线宽度≥20mil信号与地线距离6mil,每400mil内加接地过孔;②、不包地设计:线宽、间距 10/5/10mil差分对与对之间距离≥20mil(特殊情况不能小于10mil)建议整组差分信号线外采用包地屏蔽,差分信号与屏蔽地线距离≥35mil(特殊情况不能小于20mil)。90欧姆差分阻抗推荐设计①、包地设计:

线宽、间距 10/5/10mil地线宽度≥20mil信号与地线距离6mil或5mil,每400mil内加接地过孔;②、不包地设计:

线宽、间距 16/5/16mil差分对与对之间距离≥20mil建议整组差分信号线外采用包地屏蔽,差分信号与屏蔽地线距离≥35mil(特殊情况不能小于20mil)。要领:优先使用包地设计,走线较短并且有完整地平面可采用不包地设计;计算参数:板材FR-4,板厚1.6mm+/-10%,板材介电常数4.4+/-0.2,铜厚1.0盎司(1.4mil)阻焊油厚度 0.6±0.2mil,介电常数 3.5+/-0.3

图1 包地设计

图2 不包地设计

二、 四层板阻抗设计

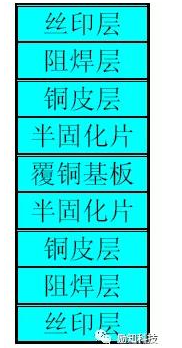

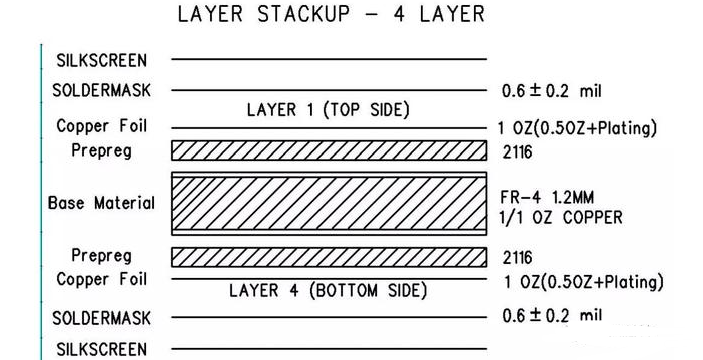

100欧姆差分阻抗推荐设计线宽、间距 5/7/5mil差分对与对之间距离≥14mil(3W准则)注:建议整组差分信号线外采用包地屏蔽, 差分信号与屏蔽地线距离≥35mil (特殊情况不能小于20mil)。90欧姆差分阻抗推荐设计线宽、间距 6/6/6mil差分对与对之间距离≥12mil(3W准则)要领:在差分对走线较长情况下,USB的差分线建议两边按6mil的间距包地以降 低EMI风险(包地与不包地,线宽线距标准一致)。计算参数:板材FR-4,板厚1.6mm+/-10%,板材介电常数4.4+/-0.2,铜厚1.0盎司(1.4mil)半固化片(PP) 2116(4.0-5.0mil),介电常数4.3+/-0.2阻焊油厚度 0.6±0.2mil,介电常数 3.5+/-0.3叠层结构:丝印层阻焊层铜皮层半固化片覆铜基板半固化片铜皮层阻焊层丝印层

图3

三、 六层板阻抗设计

六层板叠层结构针对不同的场合会有不同,本指南只对比较常见的叠层(见图 2)进行了设计推荐,后面的推荐设计都是以图2的叠层下得到的数据。外层走线的阻抗设计与四层板相同因内层走线一般情况下比表层走线多了个平面层,电磁环境与表层不同以下是第三层走线阻抗控制建议(叠层参考图4)100欧姆差分阻抗推荐设计线宽、间距 6/10/6 mil差分对与对之间距离≥20mil(3W准则);90欧姆差分阻抗推荐设计线宽、线距 8/10/8 mil差分对与对之间距离≥20mil(3W准则);计算参数:板材FR-4,板厚1.6mm+/-10%,板材介电常数4.4+/-0.2,铜厚1.0盎司(1.4mil)半固化片(PP) 2116(4.0-5.0mil),介电常数4.3+/-0.2阻焊油厚度 0.6±0.2mil,介电常数 3.5+/-0.3叠层结构:顶层丝印阻焊层铜皮层半固化片覆铜基板半固化片覆铜基板半固化片铜皮层阻焊层底层丝印

图4

四、 六层以上,请按相关的规则自行设计或咨询相关人员确定叠层结构及走线方案。

注:①、影响阻抗的情况较多,需要阻抗控制的PCB仍需要在PCB设计资料或样板单中标 明阻抗控制要求;②、100欧姆差分阻抗主要用于HDMI、LVDS信号,其中HDMI需要通过相关认证是强制要求;③、90欧姆差分阻抗主要用于USB信号;④、单端50欧姆阻抗主要用于DDR部分信号,鉴于DDR颗粒大部分采用内部调节匹配阻抗设计,设计以方案公司提供Demo板为参考,本设计指南不作推荐;⑤、单端75欧姆阻抗主要用于模拟视频输入输出,在线路设计上都有一颗75欧姆的电阻对地电阻进行了匹配,所以在PCB Layout中不需要再进行阻抗匹配设计,但需要注意线路中的75欧姆接地电阻应靠近端子引脚放置。常用PP

阻焊油厚:0.6±0.2mil Cer=3.5+/-0.3

编辑:hfy

-

PCB板

+关注

关注

27文章

1487浏览量

54782 -

阻抗

+关注

关注

17文章

983浏览量

48752 -

阻抗控制

+关注

关注

1文章

57浏览量

11042

发布评论请先 登录

线路板阻抗匹配:实操中要避开的 3 个设计误区

线路板阻抗匹配实操:过孔与拐角的处理技巧

技术资讯 I 信号完整性与阻抗匹配的关系

基于史密斯圆图实现天线阻抗匹配

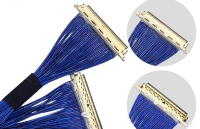

极细同轴线(micro coaxial cable)的阻抗匹配原理

村田贴片电容的阻抗匹配问题如何解决?

如何确保模拟示波器的输入阻抗匹配?

阻抗匹配中所说的50R,90R之类的阻抗是什么意思?

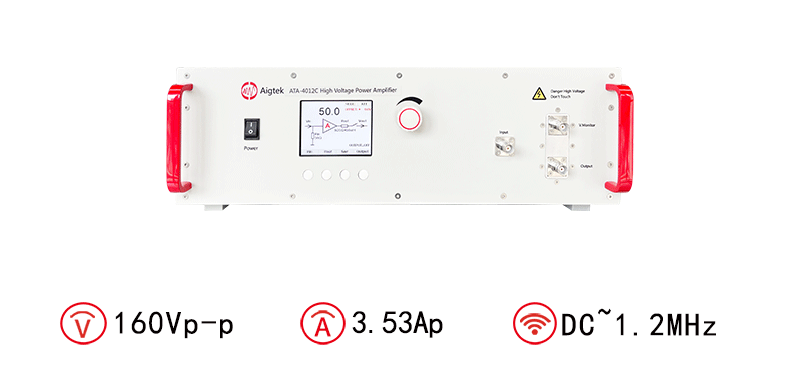

Aigtek:功率放大器如何进行阻抗匹配

LVDS连接器PCB设计与制造

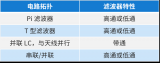

电源滤波器的阻抗匹配问题:源阻抗和负载阻抗不匹配时的优化策略

利用两个元件实现 L 型网络阻抗匹配

PCB设计之阻抗匹配设计方案

PCB设计之阻抗匹配设计方案

评论