在存储基础部件领域(Storage & Memory),这两年讨论最多的应属Intel Optane系列,全新的介质、出色的性能、非挥发特性、适中的价格,Optane受到众多存储架构师和数据中心架构师的青睐,Intel也持续大力研发和推广。本文原逻辑在2019年8月的DapuStor Haishen3系列产品发布会上已经讨论过,这里再引申一些内容,抛砖引玉,供大家探讨。

主要有以下内容:

什么是SCM(StorageClassMemory);

为什么说SCM越来越重要(数据中心基础设施在经历什么,存储行业又在经历什么);

DapuStor在思考什么(Optane SSD & Haishen3-XL)。

什么是SCM

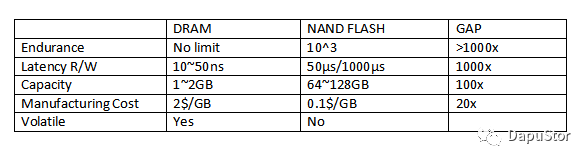

关于SCM的定义,个人觉得以下统称比较合适:“介于DRAM和NAND FLASH之间的具备非挥发特性的产品”。因为没有精确的关于SCM参数的定义,我们先来看看DRAM和NAND的一些相关参数:

表:DRAM vs NAND FLASH

可以看到这两者之间存在比较大的GAP,SCM即填补了这个GAP,如下图的产品级图示:

图:存储层缺口Gap - SCM

为什么说SCM越来越重要

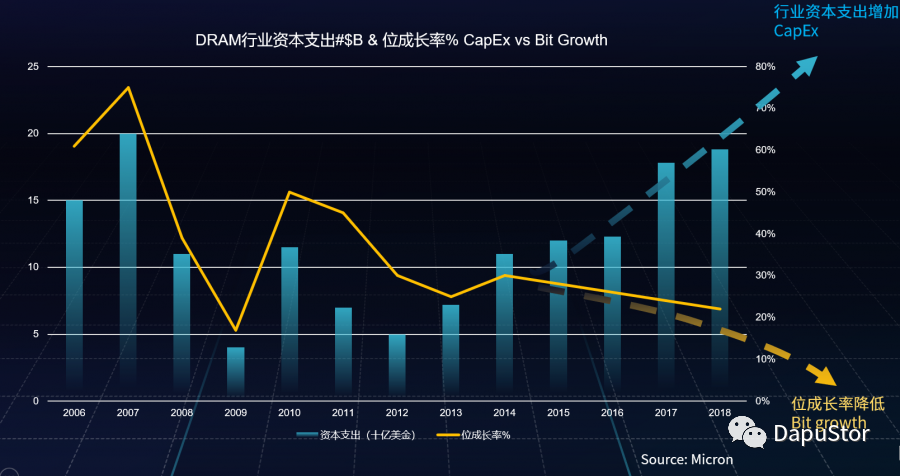

首先,每个CPU核的可用DRAM容量,每两年降低20~30%。

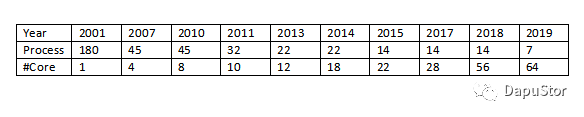

Intel创始人之一的Gordon Moore提出“集成电路上可容纳的元器件的数目,约每隔18-24个月便会增加一倍,性能也将提升一倍”,这成为IT产业最著名的摩尔定律,Intel、AMD服务器CPU路线也符合这个发展规律:

表:服务器CPU的发展

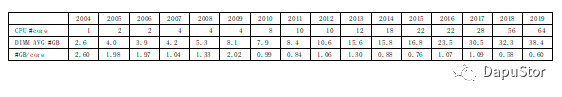

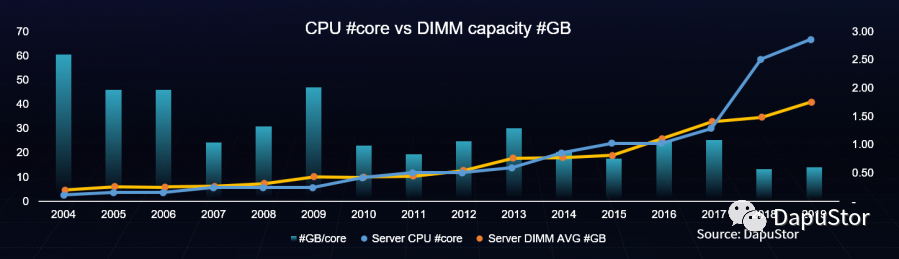

但当我们把服务器内存容量的发展趋势和CPU核数放在一起,就能看到其中的问题:

表:服务器CPU &内存的发展

即“每个服务器CPU核的可用DRAM容量,每两年降低20~30%”,其实服务器CPU对内存的“hungry”是业界的共识:

图:服务器CPU &内存的发展

这个趋势从美国阿冈国家实验室超级计算机计划 Argonne National Labs plans也可以看出:

表:阿冈国家实验室HPC计划

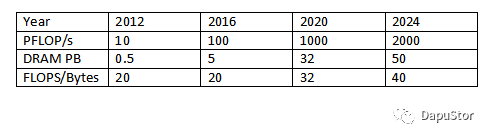

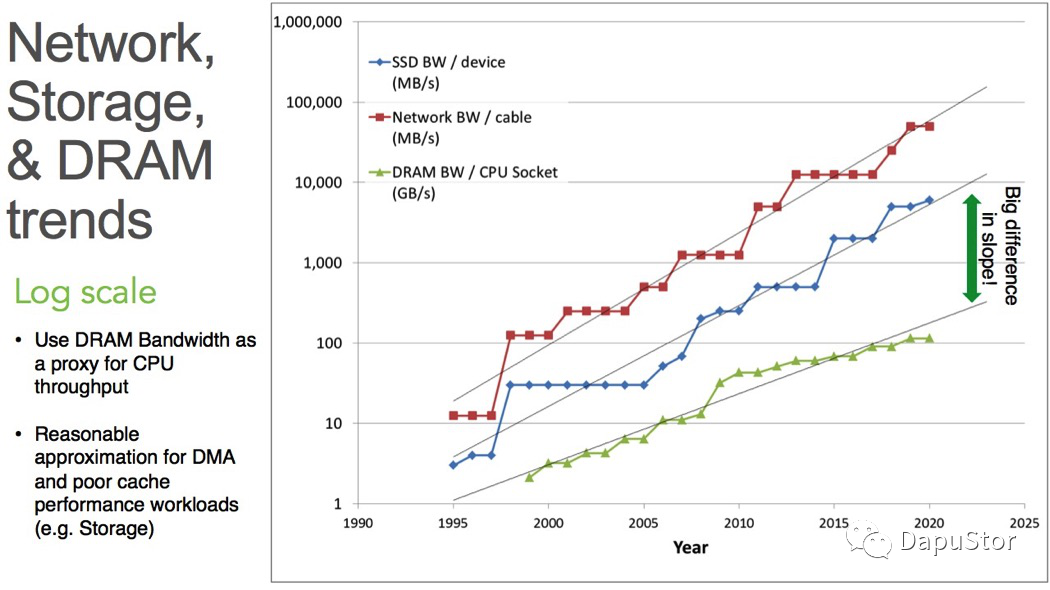

其次,CPU获得的DRAM带宽增速,远远不及SSD、网络带宽增速。

这里直接引用Sandisk Fellow Fritz Kruger的数据,有兴趣的朋友可以搜索“CPU Bandwidth – The Worrisome 2020 Trend”:

图:网络、存储、DRAM趋势(Log scale)

图:网络、存储、DRAM趋势(Linear scale)

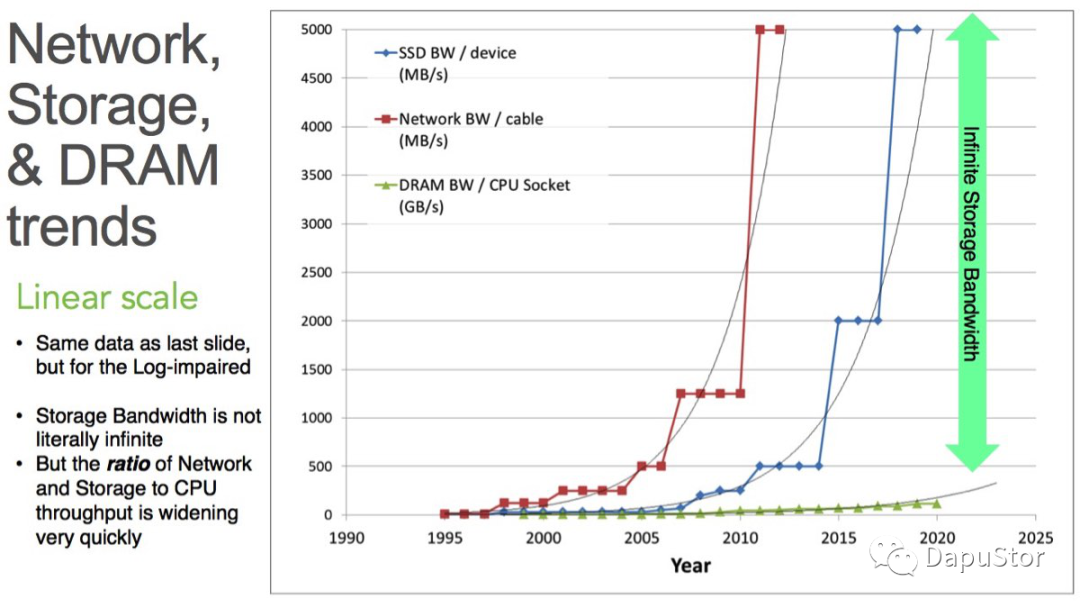

第三,DRAM行业面临scale up瓶颈。

熟悉DRAM行业的朋友,都知道DRAM行业经历了一个残酷的厮杀过程:从上世纪80年代的超过20家,到现在的“3大1小”。

在这个行业发展过程中,每一家都在靠以下两种方式竞争:“制程转进”与“扩大产能”。前者即为新工艺的研发,如20nm转往17nm,会带来比如20~30%的bit growth;后者即为更新、增加产线和设备,以增加投片和产出。这两者都需要庞大的资本投入,而在早期资本的投入和整体bit growth基本呈线性关系。

而我们如果拆开来看的话,可以发现随着制程的发展,到了20nm及以下制程后,工艺的转进带来的研发投入增长越来越庞大,大白话是“原来有100块钱,花30块钱更新制程另外70块钱扩产;但是现在更新一个制程需要花70块甚至更高”。

因此,行业近5年虽然资本支出越来越大,但产出bit growth却越来越低,也就是说整个行业面临scale up的瓶颈,资本投入和bit growth并非线性关系,且越来越明显:

图:DRAM行业资本支出和位成长率

DRAM是已经商用的最快的存储介质,从性能特性来说无法被替代,再加上现在行业的寡头局面,任何一个IT OEM厂商或者数据中心,都需要至少3家供应商。如果你是其中一家DRAM供应商,你会怎么想?会不会是“这个生意太好了,慢慢来 :)”。

综合以上各个趋势发展,聪明的架构师们就开始从系统角度来思考这个问题,这也说明了为什么SCM会被委以重任。

具体SCM的使用场景有两种:Caching 和 Tiering,一般情况下Caching相对比较容易实现,而Tiering需要更深入的上下层整合,包括配套的算法,以确保兼顾各Tier的容量比(即成本)和效率。很多大型数据中心和存储厂商都在积极寻找和布局合适Optane SCM的应用场景,比如HPE有“Memory-Driven Flash”(Caching),比如DellEMC PowerMAX支持Tiering。

DapuStor在思考什么

DapuStor(深圳大普微电子科技有限公司)致力于打造企业级智能固态硬盘、数据存储处理器芯片及边缘计算相关产品,企业级、数据中心级智能存储基础设施是我们现阶段主要的方向,而在此领域如此重要的SCM产品,当然非常关键。

合作伙伴KIOXIA(原Toshiba)在2018年提出SCM级XL-FLASH发展规划,在接下来的时间里,DapuStor也针对XL-FLASH和KIOXIA进行了长时间的紧密沟通和合作,Haishen3-XL SCM级SSD也确定了如下特性:

图:DapuStor Haishen3 SCM特性

关于Haishen3-XL和OptaneSSD、Z-SSD性能的比较

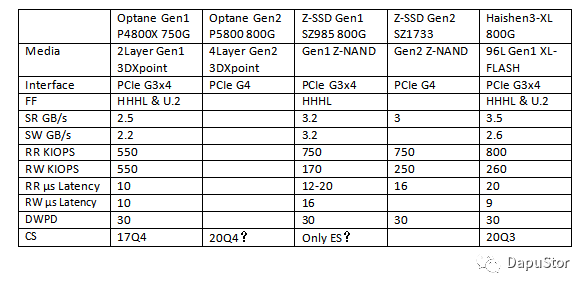

表:Optane SSD vs Z-SSD vs Haishen3-XL

Optane SSD采用3DXpoint,Z-SSD和Haishen3-XL采用optimized low-latency SLC NAND,从介质上讲3DXpoint已经不是NAND而是PCRAM,是“cross point”型架构,寻址方式、写入过程等与NAND完全不同,不需要垃圾回收,因此Optane SSD RW IOPS有明显优势,另外据说Optane Gen2 会进一步提升至60DWPD,这是从介质改革带来的优势;其它方面Haishen3-XL并不弱。

因此从整体性能方面,low-latency SLC NAND SSD,如Haishen3-XL可在大部分应用场景和Optane SSD共同存在。

DapuStor也在2020年1月份的PM Summit上基于RWW(Real World Workload)对Optane SSD、Haishen3-XL进行了比较,原文链接参考:http://www.dapustor.com/news_view.aspx?nid=2&typeid=139&id=543

关于Haishen3-XL和OptaneSSD成本的比较

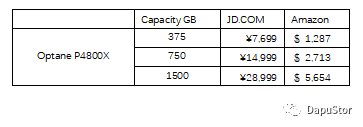

因为Intel在数据中心CPU领域占绝对垄断地位,针对CPU和Optane、SSD也有类似bundle program优势,因此我们无法估算Optane SSD的to B实际成交价格,仅以电商平台零售价来看还是挺高的:

表:Optane SSD零售价

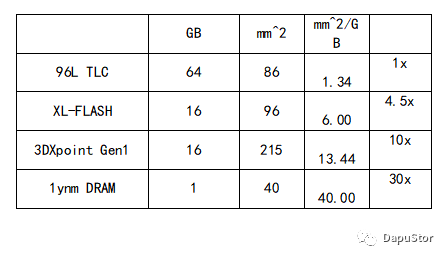

另一方面,我们粗算一下,能看到3DXpoint Gen1的Wafer成本大概是96L low-latency SLC NAND的2倍:

表:Wafer Cost:TLC vs XL-FLASH vs 3DXpoint vs DRAM

下面再看看Intel 3DXpoint从Micron的采购成本。

从Micron 2020FQ2 Earnings report,可以估算出Micron交付给Intel的3DXpoint业务预计为2B$的6%,即为120M$:

“……Revenue for the CNBU was approximately $2 billion, down approximately1% sequentially and down 17% year-over-year. We have now started to include all 3D XPoint revenue in CNBU reporting, as the use cases for 3D XPoint technology are more closely aligned with memory expansion and this business is being managed by CNBU. Excluding 3D XPoint, CNBU revenue would have been down 7% sequentially……”

而3DXpointGen1的产能约为135MGB/Q https://blocksandfiles.com/2019/08/27/3d-xpoint-revenue-forecasts/:

“……It will output 45m GB/month of Gen 1 XPoint in the fourth quarter and 5m GB/month of Gen 2 XPoint……”

即Intel采购价格约为120M$/135MGB = 0.88$/GB。Intel和Micron的长期合作协议,该价格应该是Micron能提供的最优价,基本符合上面Wafer成本的测算(3DXpoint Gen1 wafer成本大概是96L TLC的10倍).

财务表现上, Intel在Optane上的巨大研发投入,也导致NSG绝大多数财季在亏损。从长期来看,Intel大概率会持续推广Optane产品,随着3DXpoint的使用量越来越多,生产制造成本也会随之降低,形成正循环。

而从一个健康的行业发展来看,现阶段正是需要多个SCM玩家推高市场需求的时期。Low-latency NAND因为基于非常成熟的3D NAND研发生产制造流程,从生态上来说是一个非常合适的SCM产品第二选择,DapuStor也立志成为基于low-latency NAND的优秀SCM解决方案提供商。

说明:文中部分内容涉及对未来的判断,可能和实际会有出入;另外有一些数据是通过参考公开数据推测而来,并非一手数据。若有偏颇还望见谅,有问题欢迎讨论lijinxing@dapustor.com :)

-

存储

+关注

关注

13文章

4886浏览量

90270 -

SCM

+关注

关注

2文章

68浏览量

15879

原文标题:珍藏!存储级内存SCM,看这一篇就够了!

文章出处:【微信号:SSDFans,微信公众号:SSDFans】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

内存条价格闪崩,存储市场步入下行周期?

自研芯片、猛攻企业级,国内存储“量级跃迁”

慧荣科技下半年推出PCIe 6.0主控,布局企业级和消费级产品满足市场需求

工业级板载存储新选择:创世 SD NAND 实测

内存暴涨缺货?全志T536开发板灵活存储救场,现货秒发不卡壳

【「Linux 设备驱动开发(第 2 版)」阅读体验】+读深入理解Linux内核内存分配

CW32A系列(车规级 MCU)介绍

工业网关的内存有什么功能

半导体存储芯片核心解析

存储示波器的存储深度对信号分析有什么影响?

佰维存储亮相COMPUTEX 2025,全场景存储方案赋能“AI +”未来生态

国产新突破!江波龙车规级 LPDDR4x与车规级eMMC重磅发布,定义存储新标杆

存储级内存SCM详细介绍

存储级内存SCM详细介绍

评论