尽管2020年全球半导体行业会因为疫情导致下滑,但台积电的业绩不降反升,掌握着7nm、5nm先进工艺的他们更受客户青睐。今天的财报会上,台积电也首次正式宣布3nm工艺详情,预定在2022年下半年量产。

台积电原本计划4月29日在美国举行技术论坛,正式公布3nm工艺详情,不过这个技术会议已经延期到8月份,今天的Q1财报会议上才首次对外公布3nm工艺的技术信息及进度。

台积电表示,3nm工艺研发符合预期,并没有受到疫情影响,预计在2021年进入风险试产阶段,2022年下半年量产。

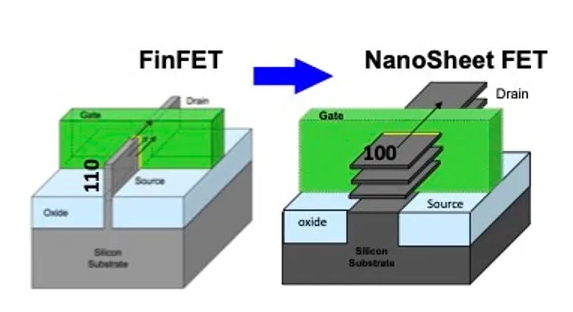

在技术路线上,台积电评估多种选择后认为现行的FinFET工艺在成本及能效上更佳,所以3nm首发依然会是FinFET晶体管技术。

在3nm节点上,台积电最大的对手是三星,后者押注3nm节点翻身,所以进度及技术选择都很激进,将会淘汰FinFET晶体管直接使用GAA环绕栅极晶体管。

根据三星的信息,相较于7nm FinFET工艺,3nm工艺可以减少50%的能耗,增加30%的性能。

至于量产时间,三星之前计划在2021年量产,不过因为疫情影响,现在也推迟到了2022年,但没有明确是上半年还是下半年,他们与台积电谁能首发3nm工艺还没定论。

随着3nm工艺的临近,人类正在逼近硅基半导体的极限,此前台积电有信心将工艺推进到2nm甚至1nm,但还是纸面上的,相关技术并没有走出实验室呢。

-

芯片

+关注

关注

446文章

47700浏览量

408840 -

台积电

+关注

关注

43文章

5262浏览量

164768

发布评论请先 登录

相关推荐

在特殊类型晶体管的时候如何分析?

台积电3nm工艺预计2024年产量达80%

全球首颗3nm电脑来了!苹果Mac电脑正式进入3nm时代

今日看点丨三星透露:已和大客户接洽2nm、1.4nm代工服务;广汽埃安 AION S Max 纯电轿车正式上市

三星披露下一代HBM3E内存性能

什么是3nm工艺芯片?3nm工艺芯片意味着什么?

来看看“不约而同”的2nm时间轴进程

台积电的3nm工艺价格为每片19150美元

一辆汽车需要哪些半导体器件?车规级芯片分类介绍

深度解析imec 晶体管和工艺节点路线图

Cadence 发布面向 TSMC 3nm 工艺的 112G-ELR SerDes IP 展示

台积电表示3nm工艺预计在2021年进入风险试产阶段 首发依然会是FinFET晶体管技术

台积电表示3nm工艺预计在2021年进入风险试产阶段 首发依然会是FinFET晶体管技术

评论