前言:

芯粒逐渐成为半导体业界的热词之一,它被认为是一种可以延缓摩尔定律失效、放缓工艺进程时间、支撑半导体产业继续发展的有效方案。

摩尔定律的演变

即便不是IT从业人士,想必也会听说过著名的“摩尔定律”:1965年,英特尔创始人戈登·摩尔提出,在至多十年内,集成电路的集成度会每两年翻一番,后来这个周期被缩短为18个月。当时摩尔先生仅仅是将摩尔定律的适用时间限定在“十年内”,但实际上处理器技术的发展令人咋舌,至今这条在当时遭到无数人质疑的奇妙定律仍旧在生效,基本上每两年制程工艺都会进入一个新的台阶。

但是,如今主流的处理器制程已经发展到22nm,而更先进的14nm、10nm工艺也已经进入了芯片制造商的产品蓝图,硅片晶体管的尺寸有着其物理极限,美国国防先进研究项目局主任Robert Colwell先生曾表示,半导体技术不断发展,制造工艺已经达到 7nm,依靠缩小线宽已无法同时满足性能、功耗、面积以及信号传输速度等多方面的要求,越来越多的半导体厂商开始把注意力放在系统集成层面,亟需发掘新的材料和芯片技术,成为硅晶体管技术的替代品。然而这是一种超越摩尔定律,是通过系统集成单颗芯片或是多芯片堆叠的方式实现,希望能做到更多的功能。

后摩尔时代的技术明星——芯粒

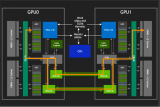

近年来,半导体厂商发现芯粒可以被认为延缓摩尔定律失效,放缓工艺进程时间,支撑半导体产业继续发展的有效方案。那什么是芯粒呢?理论上,芯粒模式是一种,开发周期短且成本较,低的方法,提供了先进工艺和主流成熟工艺选择的灵活性,芯粒技术就是像搭积木一样,可以将不同节点工艺(10nm、14/16nm及22nm)、不同材质(硅、砷化镓、碳化硅、氮化镓)、不同功能(CPU、GPU、FPGA、RF、I/O、存储器)、不同半导体公司的芯片封装在一起。

后摩尔时代保鲜剂芯粒的优点

后摩尔时代的单片集成向多片异构封装集成技术“改道”是重要趋势,相对于以往的软 IP 形式,芯粒则是经过硅验证的裸芯片。芯粒能在实现高效能运算的同时,提供更高的带宽、更低的功率、更低的成本和更灵活的形状因子等优势。

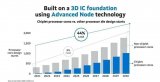

目前,已经有很多公司创建了自己的芯粒生态系统。随着芯片制程从10nm7nm到,5nm再到未来的3nm,每一次制程缩减所需要的成本和开发时间都在大幅提升。而且,当芯片制程接近1nm时,就将进入量子物理的世界,现有的工艺制程会受到量子效应的极大影响。

未来,以芯粒模式集成的芯片会是一个“超级”异构系统,为IC产业带来更多的灵活性和新的机会。

后摩尔时代保鲜剂芯粒的优点

芯粒模式成功的关键在于芯粒的标准和接口。但作为一种创新,芯粒模式存在多种挑战。

① 技术层面

芯粒的组装或封装尚缺乏统一的标准。目前各大玩家都有自家的方案,尽管各家的名称不同,但归总离不开硅通孔、硅桥和高密度FO技术,不管是裸片堆叠还是大面积拼接,都需要将互连线将变得更短,要求互连线做到100%的无缺陷,否则整个芯片无法工作。

② 质量保障问题

相对传统软IP,芯粒是经过硅验证的裸芯片,可以保证物理实现的正确性。但如果其中的一个裸芯片有问题,则整个系统都会受影响,代价很高。因此要保证芯粒100%无故障。当然这其中也包括集成后的测试,封装后,可能有部分芯粒可能完全无法直接从芯片外部管脚直接访问,给芯片测试带来的新的挑战。

③ 散热问题

几个甚至数十个裸芯片封装在一个有限的空间中,互连线非常短,让散热问题变得更为棘手。

④ 芯片网络问题

尽管每个芯粒本身设计不会发生死锁,其通信系统都可以很好地工作,但是当它们全部连接在一起形成芯片网络时,就可能出现了交通死锁与流量堵塞问题。超微半导体研究人员最近提出一种消除死锁难题的方案,如果能够彻底解决死锁问题,那么芯粒将为未来计算机设计的发展带来新的动力。

⑤ 供应链重塑问题

在芯粒模式下,EDA工具提供商、芯片提供商、封测提供商都要有所改变。比如芯粒模式中出现的问题可能最终都需要通过EDA工具的改进来给出答案,需要EDA工具从架构探索、到芯片实现、甚至到物理设计提供全面支持。还有来自不同的芯片提供商的裸芯片进入封装提供商工厂的进度同步问题。

结尾

芯粒将驱动半导体工业的未来,而这是一场即将到来的MCP海啸。大型芯片制造商也正在转向芯粒,若干年后是否会形成一个开放的产业生态、是否要建立芯粒生态推进联盟是值得行业思考的问题。

责任编辑:wv

-

半导体

+关注

关注

336文章

29986浏览量

258293 -

后摩尔时代

+关注

关注

0文章

13浏览量

9317 -

芯粒

+关注

关注

0文章

81浏览量

395

发布评论请先 登录

首创3D-CIM架构!微纳核芯定义后摩尔时代AI算力新范式

UCIe协议代际跃迁驱动开放芯粒生态构建

面向芯粒设计的最佳实践

借助Arm芯粒技术构建计算未来

【「AI芯片:科技探索与AGI愿景」阅读体验】+半导体芯片产业的前沿技术

华大九天推出芯粒(Chiplet)与2.5D/3D先进封装版图设计解决方案Empyrean Storm

后摩尔时代破局者:物元半导体领航中国3D集成制造产业

Chiplet与3D封装技术:后摩尔时代的芯片革命与屹立芯创的良率保障

奇异摩尔出席第三届芯粒开发者大会AI芯片与系统分论坛

Arm正式发布芯粒系统架构首个公开规范

Arm发布芯粒系统架构首个公开规范

广电计量受邀参加后摩尔器件研讨会 携半导体综合技术解决方案亮相

对话郝沁汾:牵头制定中国与IEEE Chiplet技术标准,终极目标“让天下没有难设计的芯片”

后摩尔时代保鲜剂芯粒的优点有哪些

后摩尔时代保鲜剂芯粒的优点有哪些

评论