由于电子设计日渐复杂,设计人员通常需要采用各种不同类型的功能,但他们无法具备所有的专业知识、资源和时间。这促使了半导体知识产权(SIP)市场的增长,预计2017年将达到57亿美元。某些复杂设计使用的各种SIP模块甚至多达100多种。因此,需要解决如何将这些模块集成到设计中,并验证它们能够在底层硬件上很好地工作。在每一新工艺代上,这都变得越来越困难。

而且,当使用来自不同供应商的SIP模块时,由于没有标准指导如何编写这些模块,或在不同设计中如何使用它们,因此,互操作性问题也越来越复杂。每一个模块对速度、功耗、管芯尺寸等方面都有不同的要求,芯片系统(SOC)设计人员无法切实有效地满足所有需求。因此,使用多家供应商的IP模块实现最优设计颇具挑战。

此外,如果业界仍然按照过去十年的发展轨迹继续走下去,实现一个每秒400吉比特(Gbps)的系统几乎要完全占用1百万逻辑单元(LE)的整片FPGA。这肯定不会被客户接纳。Altera已认识到这一点,从头开始重新规划了高性能IP,不仅速度更快以支持越来越高的数据速率,而且还提供更小、更高效的IP。采用创新的体系结构,IP模块比以前的产品快两倍,体积小50%。

对速度的需求

互联网的爆炸式增长使得高速数据处理成为一项关键功能。据国际电信联盟(ITU),2011年,世界70亿人口中有三分之一使用互联网,产生的网络流量高达每秒80太比特(Tbps),比上一年增长45%。

下一波互联网应用是机器至机器(M2M)通信,即物联网(IoT)。IoT涉及多种设备,如智能仪表、无线传感器节点、工业监视控制和数据采集(SCADA)系统、网关,以及高速收费标签读卡器等。所有这些都会在公共和私有基础设施上产生大量的数据流。IoT市场在2011年达到440亿美元,预计每年增长30%,2017年会达到2900亿美元。

另一个增长迅速的领域是移动通信。2011年IP数据流的55%来自移动通信——每年的增长率达到66%。这对于电信公司而言是巨大的挑战,他们目前正尽快部署4G网络。基站越来越多地依靠高速FPGA来提高内核性能,在很宽的频率范围内处理复杂的功能。FPGA能够灵活地适应不断变化发展的标准,有助于保护在4G基站上的投入。

据思科公司,互联网协议数据流在2016年底每年会超过万亿字节(1021)。

数据中心尤其要面对很大的压力来处理越来越大的数据流。多核处理器这种发展趋势虽然解决了功耗问题,但外部存储器和数据带宽却跟不上计算能力的增长。这种情况非常适合采用FPGA进行数据访问、计算和网络加速,解决数据访问瓶颈问题。随着云计算和软件即服务(SaaS)的不断发展,这将会越来越重要。

下一代FPGA将采用高速串行存储器克服并行存储器接口的带宽、延时和功耗局限。Arria 10 FPGA能够很轻松地处理100 Gbps和200 Gbps数据流。具有多个56 Gbps收发器的Stratix 10 FPGA可以处理400 Gbps以太网(GbE)和500 Gbps Interlaken数据流。

全面的Altera IP

FPGA虽然能解决4G基站和数据中心通道卡的存储器和I/O接口瓶颈问题,但数据通路带宽和频率的增长通常也使功耗直线上升。这是Altera在全系列IP内核上综合考虑的关键问题,以及带宽和管芯尺寸。

对任何应用而言,存储器访问都非常关键。Altera FPGA具有丰富的片内SRAM存储器,而对于需要快速访问片外存储器的应用,Altera及其合作伙伴提供存储器控制器IP内核、参考设计和设计实例。所有这些都经过了硬件测试的置入式设计模块,能够大大简化复杂存储器的本地接口。支持的标准包括:

●SDR SDRAM

●RLDRAM 2或者RLDRAM 3

●DDR SDRAM

●DDR2 SDRAM

●DDR3 SDRAM

●DDR4 SDRAM

存储器技术发展非常快,Altera始终都在追踪最新变化。Micron的3-D混合立方存储器(HMC)的带宽是DDR3 SDRAM模块的15倍,能耗比现有技术低70%,占用的电路板空间减少了90%。Altera和Micron最近展示了Altera 28 nm Stratix V FPGA和Micron HMC的互操作性。今后的Arria 10和Stratix 10 FPGA都将包括HMC接口。

对于芯片至芯片、电路板至电路板,以及机框至机框连接,Altera及其合作伙伴提供175种不同的互联IP内核和参考设计,采用了集成到FPGA和ASIC器件中的收发器,仅以太网IP内核就能提供60种解决方案。以许可IP内核和参考设计以及免费宏功能和设计实例的形式提供这些接口协议。

PCI Express (PCIe)是数据中心所采用的主要背板互联标准。Altera通过其Cyclone、Arria和Stratix FPGA产品线来提供PCIe Gen1 (2.5 Gbps)和Gen2 (5.0 Gbps) IP。Stratix V FPGA包含PCIe Gen3 (8.0 Gbps),以硬核IP模块的形式嵌入协议栈。PCIe标准一直是10代FPGA关注的重点。硬核实现了PCIe模块后,每一IP例化的资源节省了8,000至30,000个LE,与功能等价的软核IP相比,时序收敛更快,设计和编译时间更短,而且有效地降低了功耗。所有PCIe内核都经过验证,符合相应的PCI Express基本规范。

更小、更快、更好

Altera新的低延时10GbE IP内核最先受益于10代FPGA体系结构。IP优化将内核性能从156.25 MHz提高到312.5 MHz。表2对比了现有标准10GbE IP内核与新的低延时内核。不但体积减小36%,速度提高24%,而且低延时40GbE IP内核在体积和延时方面的优势是减小了40%,而低延时100GbE IP内核打破了传统的思路,引脚布局减小了55%,往返延时降低了70%。与已经非常优秀的内核和真正同类最佳的IP相比,这些IP均更为先进。

表1列出了标准和低延时10GbE IP内核在大小和速度上的不同。

表1.10GbE内核大小和速度

表2列出了标准和低延时40GbE IP内核在大小和速度上的不同。

表2.40GbE IP内核大小和速度

表3列出了标准和低延时100GbE IP内核在大小和速度上的不同。

表3.100GbE IP内核大小和速度

Interlaken是可扩展协议,支持从10 Gbps到100 Gbps及以上的芯片至芯片数据包传送。Interlaken设计用于接入、骨干以太网和数据中心应用的多太比特路由器和交换机,这些应用要求IP可配置,以优化系统性能和互操作性。Altera的Interlaken IP内核使用了Stratix V和Arria V FPGA中的硬核PCS,与软核IP相比,节省了30%至50%的逻辑资源。Altera的IP内核经过了大量的仿真验证,确保了符合Interlaken协议规范v1.2。表4总结了Altera Interlaken IP的特性和优点:

表4.Altera Interlaken IP的特性和优点

目前低延时10GbE IP内核已开始提供,并可早期试用Interlaken和40GbE以及100GbE IP内核,预计2014年上半年开始批量供货。

设计人员可以从数百个Altera IP解决方案中进行选择,所有这些IP都经过了全面的测试、验证和优化,能够在底层硬件上工作,从而避免了棘手的集成问题,支持围绕复杂的IP模块开发应用程序,并确保能够协同工作,因此,产品能够更迅速面市。

随着数据速率的不断提高,100 Gbps带宽会很快耗尽,新的400 Gbps系统高速协议将是现有硬件面临的一个主要难题。10代FPGA体系结构不断创新,Altera可交付1 GHz FPGA,极大的提高了带宽,同时切实降低了功耗,减小了管芯尺寸。Stratix 10 FPGA将能够处理400GbE,甚至500 Gbps Interlaken。

综合考虑进行设计

那么Altera是如何针对这么多的IP内核快速实现如此低的延时,并减小尺寸的?答案在于IP体系结构以及底层FPGA硅片的体系结构。事实上,二者相结合才实现了电路板上的这些重大改进。对于底层硅片,通常认为芯片设计不可避免的会有困难,在速度、功耗、延时和管芯尺寸上要进行难以取舍的综合考虑。从28 nm开始,Altera重新设计了FPGA,与前一代FPGA相比,生产的芯片速度更快,功耗更低,体积更小,设计人员工作起来比以前更自由。

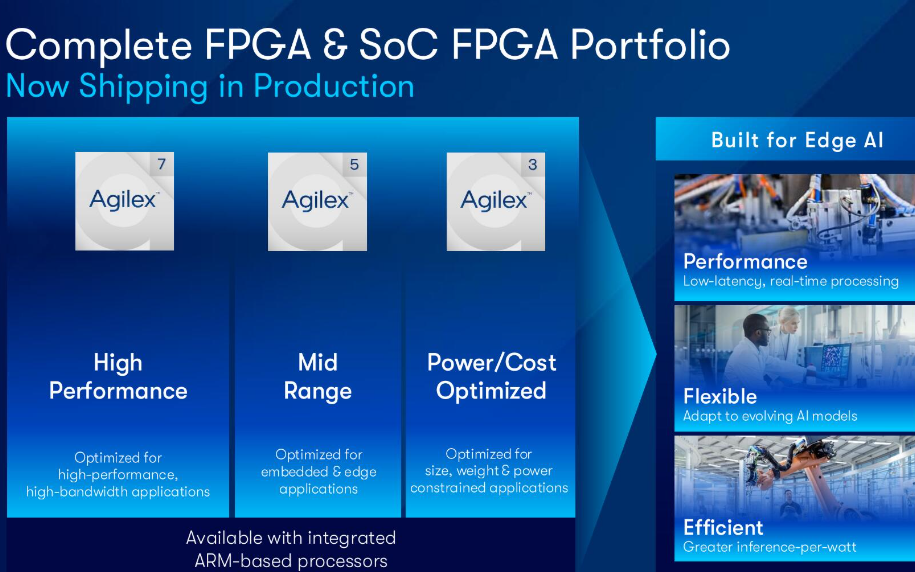

中端Arria 10 FPGA和SoC是10代系列产品中推出的第一款系列器件。该系列器件为中端可编程器件设立了新标杆,以最低的中端器件功耗实现了当前高端FPGA的性能和功能。利用针对TSMC 20 nm工艺进行了优化的增强体系结构,Arria 10 FPGA和SoC比前一器件系列的性能更强,而功耗降低了40%。

Arria 10器件的特性和功能比目前的高端FPGA更丰富,而性能提高了15%。Arria 10 FPGA和SoC反映了硅片融合的发展趋势,实现了系统集成度最高的中端器件,包括115万LE、集成硬核IP和第二代处理器系统,这一系统具有1.5 GHz双核ARM Cortex-A9处理器。Arria 10 FPGA和SoC含有28 Gbps收发器,带宽比当前一代产品高4倍,系统性能提高了3倍,支持每秒2,666兆比特(Mbps) DDR4 SDRAM以及15 Gbps HMC。

高端Stratix 10 FPGA和SoC——内核性能高达1 GHz,将超过10 TeraFLOPS,这一性能水平是任何货架器件都不具备的。

对于在这些硅片平台上重新设计的IP,Altera工程师重新研究了数据通路,减少了流水线,非常关注优化控制结构。这样,他们将时钟速率提高了一倍,而延时没有变化。

Altera逻辑单元注意到在传统的流水线中,在寄存器级之间通常有三个甚至更多的LUT。现有的硬件体系结构有太多的寄存器,如果不增加后布局布线面积就无法提高寄存能力(请参考图1)。

图1.Altera逻辑单元,每一个未寄存的LUT靠近一个未使用的寄存器。

将未寄存的LUT与寄存器相匹配导致电路带宽加倍,同时保持了面积不变。例如,100GbE能够运行在200 Gbps。应用工程师现在可以选择运行两个独立的流,也可以占用一半的电路来运行一个流(请参考图2)。

图2.未寄存LUT与未使用的寄存器相匹配

最后的选择涉及到删除一半的宽度,保持最初的带宽。对于并行度很高的电路,这是停止点:时钟速率加倍,相同的延时,一半的面积(请参考图3)。

图3.提高了效率,限制带宽能够减小管芯面积。

所有这些体系结构创新都应用到了Stratix V、Arria 10以及Stratix 10 FPGA和SoC上。这就是前面列出的所有IP变小、更快、更好的主要原因。这些发现促使Altera在将要发布的所有新IP内核中实现Altera这些良好的实践。已经更新了Altera的设计软件,确保全面的器件支持,实现与已有设计的无缝移植。

结论

Altera 10代FPGA可实现提高系统总吞吐量,降低延时,同时减小功耗。电路设计人员能够从多种10代Arria和Stratix FPGA中进行选择,这些器件在带宽、延时、功耗和管芯大小方面各有侧重。但是,对于任何应用,其性能要远远超出目前所遇到的应用,能够很好的满足各种设计需求。

使用Altera全系列同类最佳的IP,如10代FPGA,设计人员能够尽快向市场推出最前沿的产品,在今后多年中都能保持领先地位。

责任编辑:gt

-

FPGA

+关注

关注

1664文章

22502浏览量

639203 -

寄存器

+关注

关注

31文章

5619浏览量

130410 -

Altera

+关注

关注

37文章

828浏览量

159130

发布评论请先 登录

Altera三大FPGA系列产品生命周期支持延至2045年

Altera Agilex FPGA与SoC实现更智能的AI

奕行智能论文入选国际计算机体系结构顶级会议 ISCA 2026

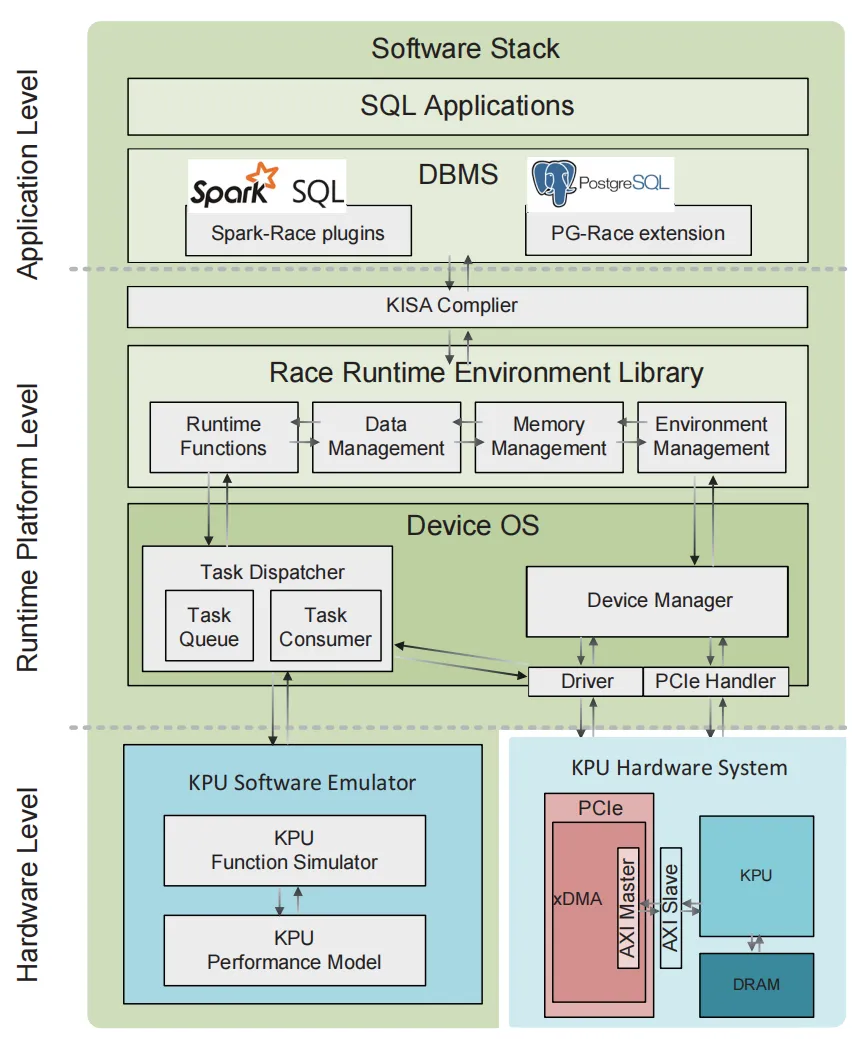

操作系统体系结构

Altera携手合作伙伴共建FPGA创新未来

Altera全新推出MAX 10 FPGA封装新选择

Altera进一步扩展 Agilex™ FPGA 产品组合,全面提升开发体验

使用Altera SoC FPGA提升AI信道估计效率

Altera FPGA 的PIO IP当中bidir和inout选项的区别

DPU核心技术论文再次登陆体系结构领域旗舰期刊《IEEE Transactions on Computers》

Altera Agilex 3 FPGA和SoC产品介绍

基于Altera 10代FPGA体系结构的低延时IP内核和参考设计

基于Altera 10代FPGA体系结构的低延时IP内核和参考设计

评论