近日,奕行智能宣布其论文《Dynamic Scheduling for AI Accelerators via TISA》(基于 Tile 级虚拟指令集实现 AI 加速器的动态调度)正式入选 ISCA 2026(International Symposium on Computer Architecture,国际计算机体系结构年会)。

ISCA 创立于 1973 年,是计算机体系结构领域最权威的学术会议之一,与 MICRO、HPCA 并称"三大顶会"。谷歌 TPU 初代架构论文(ISCA 2017)发布于此,历届论文见证了算力架构从指令集变革到异构计算的每一次关键演进。

算力竞争范式转移,动态调度恰逢其时

AI 算力竞争正从"谁算得更快"转向"谁算得更省"。推理场景爆发后,Token 成本成为 AI 基础设施商业价值的核心指标,提升算力利用率与能效已是决胜关键。

现有 AI 加速器普遍依赖传统静态调度:执行策略往往在编译期一次性固化,无法响应运行时动态变化。随着模型规模扩大,编译复杂度高、硬件行为适配难、运行时变化导致流水线空泡,硬件潜能被浪费。奕行智能此次入选 ISCA 的论文,正是对这一行业痛点的系统性解答。

三位一体闭环,重新定义动态调度

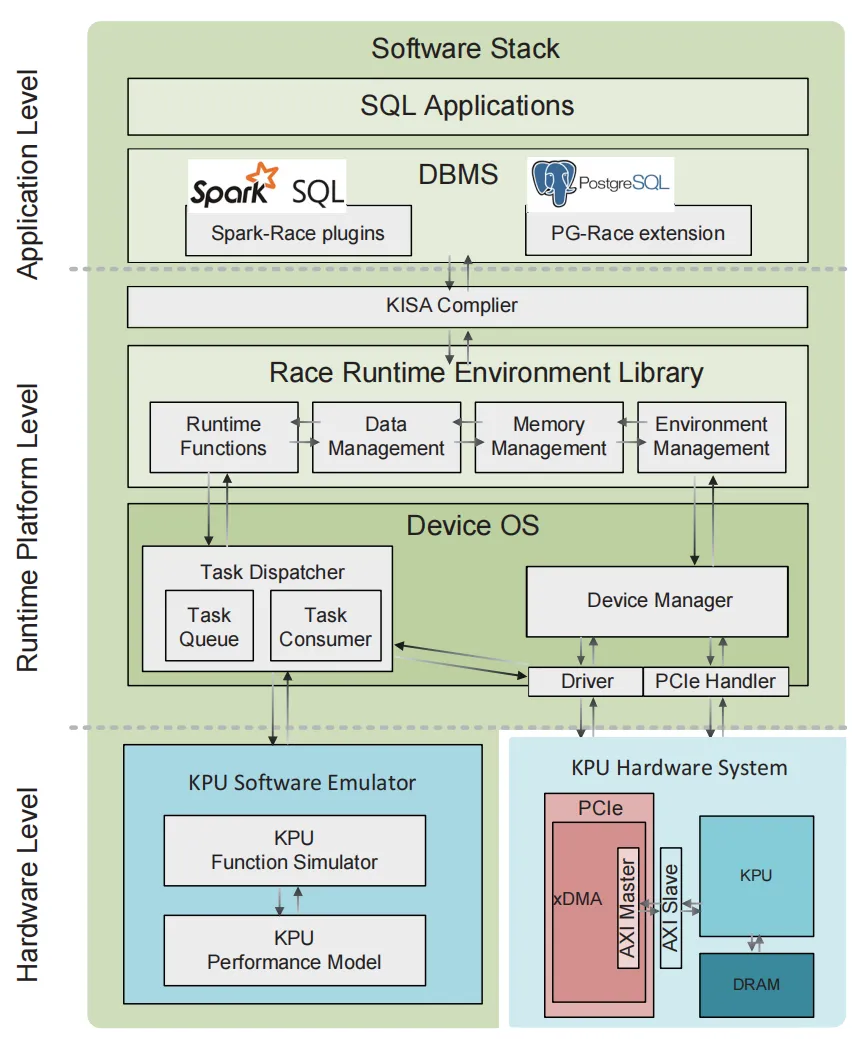

奕行智能入选顶会ISCA的论文,围绕其独家打造的 Tile 级动态调度架构展开,通过"虚拟指令+ 智能编译器 + 硬件调度器"的三位一体闭环,将复杂的指令依赖、流水线管理和内存切分全部交由硬件自动完成,从根本上打破静态优化的性能上限,也让上层开发像"拼积木"一样干净简洁。

具体而言,架构由三个核心组件协同构成:Tile 级虚拟指令集(VISA)在硬件底层与上层软件生态之间架起统一接口,智能编译器ACE 自动处理指令映射与优化,VISA 调度器则在硬件层实时感知运行状态,动态平衡Tile 执行与资源分配,将算力利用率推向极限。三者协同,将"一次性规划"升级为"运行时持续寻优",让硬件并行潜能得到更充分的释放。

数据说话:多模型全面验证

论文在DeepSeek-R1、ResNet-50、BERT、GPT-J、LLaMA2 及 FlashAttention-3 等主流大模型与视觉模型上进行系统评测,结果表明:

- 相较基线方案,整体加速比达1.52–1.92×;

- 优于强静态流水调度方案1.14–1.63×;

- FlashAttention-3 场景下,硬件利用率提升 +26.4%。

多平台、多模型的评测结果充分验证了动态调度架构的广泛适用性与稳定优势。

此次入选ISCA 2026,是国际顶级学术界对奕行智能技术原创性的有力认可。从语义感知编译到运行时动态寻优,从打破静态天花板到充分释放硬件潜能,TISA 框架指向 AI 加速器架构创新的下一个范式。

-

加速器

+关注

关注

2文章

841浏览量

40232 -

AI

+关注

关注

91文章

40927浏览量

302512

发布评论请先 登录

传音相关研究成果入选计算机视觉顶会CVPR 2026

理想汽车马赫100芯片论文入选ISCA 2026

地平线11篇论文强势入选CVPR 2026

奕斯伟计算携RISC-V创新成果亮相Embedded World 2026

由顺序主导的计算机体系

后摩智能4篇论文入选人工智能顶会ICLR 2026

MediaTek多篇论文入选全球前沿国际学术会议

易控智驾荣获计算机视觉顶会CVPR 2025认可

思必驰与上海交大联合实验室研究成果入选两大顶级会议

后摩智能与高校合作研究成果荣获ISCA 2025最佳论文奖

理想汽车八篇论文入选ICCV 2025

DPU核心技术论文再次登陆体系结构领域旗舰期刊《IEEE Transactions on Computers》

奕行智能论文入选国际计算机体系结构顶级会议 ISCA 2026

奕行智能论文入选国际计算机体系结构顶级会议 ISCA 2026

评论