在现代 5G 网络中,快速且准确的信道状态信息 (CSI)更新是保障连接质量、优化 MIMO 配置并提供一致用户体验的核心基础。然而,随着网络密度的持续提升和流量规模的迅速激增,这些更新带来的信令开销急剧扩大,导致上行带宽的利用率出现瓶颈。

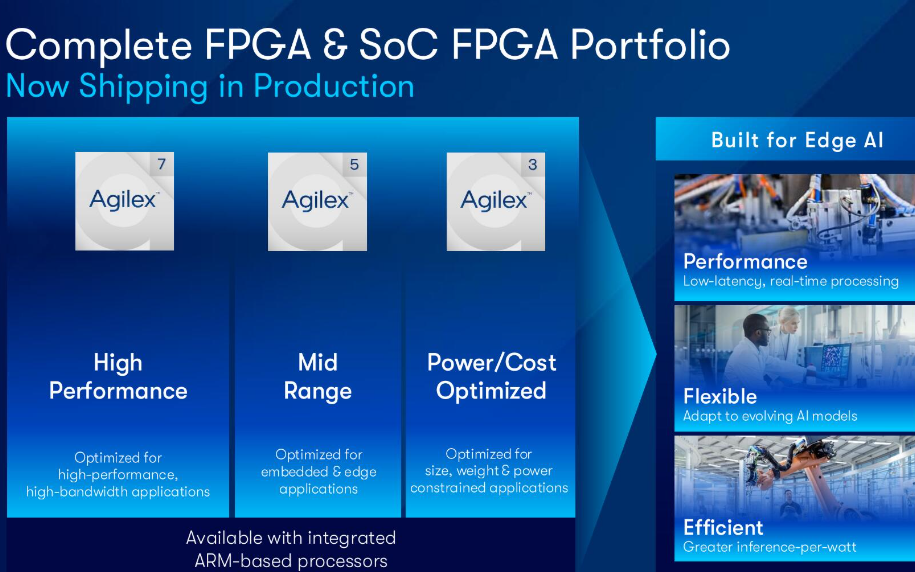

为应对这一挑战,Altera 正依托Agilex SoC FPGA,提供由 AI 驱动的 CSI 压缩解决方案。结合 Altera 的FPGA AI 套件和 OpenVINO 开源工具包部署深度学习模型。

该方案能够将更新频率和信令负担降低高达 99.9%,同时确保原始 CSI 数据与重构后的数据之间保持0.9999 以上的相关性。

面向下一代 RAN 的高效压缩解决方案

在高移动性场景中,CSI 通常需要每个传输时间间隔更新一次,这无疑给上行链路容量带来了持续的压力。

针对这一问题,新方案采用基于神经网络的自动编码器,通过在代表性信道数据上开展训练,能够以更高的准确性实现 CSI 压缩和重构。此举不仅有助于减少信令数量,还能释放频谱资源供用户数据使用,进而全面提升整体网络效率。

技术亮点

信令开销降低高达 99.9%,同时保持CSI 的无损保真度;

原始与重构信道矩阵相关性高达 0.9999 以上;

基于FPGA AI 套件、OpenVINO 及Quartus Prime实现技术落地;

符合 3GPP 5G Rel-17 标准,并可适配新兴的 6G 框架。

这一解决方案清晰展现了如何借助高能效的 FPGA 逻辑结构,通过在边缘实时执行数据驱动的优化,以 AI 替代传统人工调优的启发式方法。

以 FPGAi 打造更高效的无线解决方案

FPGAi 作为 Altera 面向 FPGA 架构的 AI 原生方法,CSI 压缩仅是其广泛应用中的一个典型案例。

FPGAi 还将驱动 RAN 系统向着更智能、更高效的方向持续演进。借助 Agilex SoC FPGA,开发人员能够将先进的 AI 功能深度集成至无线信号链,进而有效攻克带宽、时延和功耗三大核心挑战。

-

FPGA

+关注

关注

1664文章

22508浏览量

639470 -

Altera

+关注

关注

37文章

828浏览量

159161 -

AI

+关注

关注

91文章

41295浏览量

302678

原文标题:Altera SoC FPGA 助力:AI 信道估计效率实现显著提升

文章出处:【微信号:英特尔FPGA,微信公众号:英特尔FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Altera Agilex FPGA与SoC实现更智能的AI

贸泽电子开售:面向工业、AI、医疗、数据中心等领域的Altera Agilex 5 FPGA与SoC

Altera即将亮相Embedded World 2026

使用NORDIC AI的好处

Altera Agilex 5系列FPGA与SoC产品荣膺2025全球电子成就奖

Altera Agilex 5 D系列FPGA和SoC家族全面升级

Altera发布 Quartus® Prime 专业版和 FPGA AI 套件 25.3 版:编译更快,智能更强

Altera FPGAi解决方案助力mMIMO系统性能提升

Altera Agilex 3 FPGA和SoC产品家族的性能分析

Altera进一步扩展 Agilex™ FPGA 产品组合,全面提升开发体验

Altera Agilex 3/5 FPGA和SoC的功能特性

全球各大品牌利用NVIDIA AI技术提升运营效率

Altera SoC FPGA如何助力实现AI信道估计

Altera Agilex 3 FPGA和SoC产品介绍

使用Altera SoC FPGA提升AI信道估计效率

使用Altera SoC FPGA提升AI信道估计效率

评论