Frederik Dostal

ADI公司

许多模拟电路需要一种时钟信号,或者要求能在一定时间后执行某项任务。对于这样的应用,有各种各样适用的解决方案。对于简单的时序任务,可以使用标准的555电路。使用555电路和适当的外部组件,可以执行许多不同的任务。

然而,使用相当广泛的555定时器有一个缺点,就是设置不太精确。555定时器通过给外部电容充电和检测电压阈值来工作。这种电路很容易制作,但它的精度很大程度上取决于其电容的实际值。

晶体振荡器适用于精度要求较高的应用。它们的精度可能很高,但它们有一个缺点:可靠性。参与电气设备维修的人都知道,故障通常是由大型电解电容引起的。晶体振荡器是引起故障的第二大原因。

第三种测量时间长度或生成时钟信号的方法是使用一个简单的小型微控制器。当然,可供选择的器件数量繁多,且可以选择各自不同的优化方法。但是,这些器件需要编程,用户需要掌握一定的知识才能使用它;此外,由于其采用数字设计,在关键应用中使用时,必须非常小心谨慎。例如,如果微控制器发生故障,整个系统会出现问题。

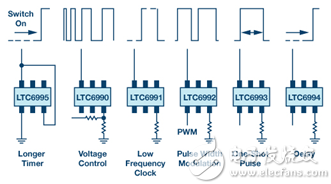

除了这三种基本的时钟产生构建块之外,还有其他不太为人所知的替代方案。ADI公司提供的TimerBlox模块就是这样一种替代方案。它们是基于硅的时序模块,与微控制器不同,它们在运行中是完全模拟的,可以通过电阻进行调整。所以,它不需要软件编程,功能也非常可靠。图1对不同的TimerBlox模块进行了概述,且介绍了它们各自的基本功能。使用这些基本构建模块可以生成无数其他功能。

图1.用于生成各种时序功能的TimerBlox电路。

与广泛使用的555定时器电路相比,TimerBlox电路不依赖外部电容充电。所有的设置都在电阻中完成,因此其功能更精确。精度可达到1%至2%。晶体振荡器的精度更高,约为100倍,但随之而来的是各种缺点。

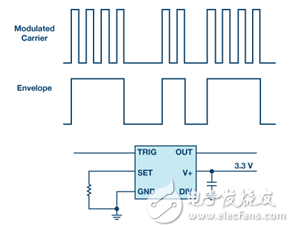

图2.采用LTC6993 TimerBlox集成电路的包络检波器。

时序模块的应用非常多样化。ADI公司已经发布了许多示例电路。图2显示了一个包络检波器。几个快速脉冲结合在一起形成一个较长的脉冲。LTC6993-2的外部组件对于这个应用来说是最少的。电路中的电容只是一个支持电源电压的备用电容,对定时模块的精度没有影响。

其他有趣的应用还包括用于电源的多个开关稳压器的相移同步,或将扩频调制添加到具有同步输入的开关稳压器IC中。另一个典型的应用是部署指定的延迟,也就是定时器为特定的电路段提供延迟开启的功能。

有许多不同的技术解决方案用于生成时钟信号和执行各种基于时间的任务。每种方案各有其优缺点。例如TimerBlox模块这样的硅振荡器,就因为使用可变电阻代替电容,所以具备易于使用、精度高、可靠性高等特点。

作者简介

Frederik Dostal曾就读于德国埃尔兰根-纽伦堡大学微电子学专业。他于2001年开始工作,涉足电源管理业务,曾担任多种应用工程师职位,并在亚利桑那州凤凰城工作了四年,负责开关模式电源。Frederik于2009年加入ADI公司,担任欧洲分公司的电源管理技术专家。联系方式:frederik.dostal@analog.com。

发布评论请先 登录

板子的差分时钟如何正确地转化为单端

工业现场的CCLink模块总线协议通讯:网关模块的应用价值

西门子再收购EDA公司 西门子宣布收购Excellicon公司 时序约束工具开发商

FPGA时序约束之设置时钟组

一文详解Vivado时序约束

正确的时序

正确的时序

评论