CPU的生产是需要经过硅提纯、切割晶圆、影印、蚀刻、分层、封装、测试7个工序,这个过程中要进行加工各种电路和电子元件,制造导线连接各个元器件。其工艺的先进与否关系到CPU内能塞进多少个晶体管,还有CPU所能达到的频率还有它的功耗。1978年Intel推出了第一颗CPU--8086,它采用3μm(3000nm)工艺生产,只有29000个晶体管,工作频率也只有5MHz,而现在晶体管数量最多的单芯片CPU应该是Intel的28核Skylake-SP Xeon处理器,它拥有超过80亿个晶体管,而频率最高的则是Core i9-9900K,最大睿频能到5GHz,它们都是用Intel的14nm工艺生产的。

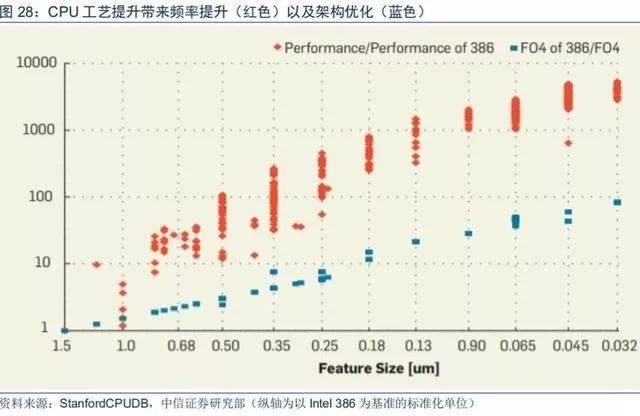

先进的制程工艺提升对于 CPU 性能提升影响明显。工艺提升带来的作用有频率提升以及架构优化两个方面。一方面,工艺的提升与频率紧密相连,使得芯片主频得以提升;另一方面工艺提升带来晶体管规模的提升,从而支持更加复杂的微架构或核心,带来架构的提升。根据 CPUDB 的数据,可以看出在芯片发展历史上,工艺提升显著带来了频率提升和架构提升的作用。随着制程节点进步,可以发现频率随工艺增长的斜率已经减缓,由于登德尔缩放定律的失效以及随之而来的散热问题,单纯持续提高 CPU 时钟频率变得不再现实,厂商也逐渐转而向低频多核架构的研究。

AMD 先前代工厂商 GlobalFoundries14nmLPP 技术授权自三星,工艺水平低于 Intel 14nm,但同价位产品多线程性能更高。以 AMD 目前最新的 Ryzen 系列处理器为例,Ryzen系列于 2017 年 3 月上市,采用 ZEN 架构,制作工艺采用 GlobalFoundries 14nmLPP,事实上 GlobalFoundries 14nmFinFET 技术于 2014 年购买自三星,在栅极间距(Gatelength)/CPP(ContactedPolyPitch)、鳍片间距(FinPitch)、第一层金属间距(MetalPitch)等参数上 AMD 14nm 处理器均弱于 Intel 14nm 处理器。根据 Anandtech 性能测试结果,AMDRyzen 系列 CPU 在单线程性能方面弱于同价位 IntelCPU,但由于采用了堆积更多核心的设计,实际多线程性能强于同价位 IntelCPU,因而 AMD RyzenCPU 实际拥有更高性价比。

目前服务器市场英特尔占据约 99%市场、AMD 约 1%;桌面级市场英特尔约占 91%、AMD 约 9%。AMD 在 CPU 市场长期位于市场第二,近几年来市场份额有显著下降。但自2017 年 AMD 发布 Ryzen 新系列之后,新品获得较好反响,市场份额开始好转。2018 年AMD 服务器 CPU 市场份额已回升超过 1%,个人电脑 CPU 市场份额亦回升至 10%左右。

AMD转投台积电后,工艺水平赶超英特尔,有望持续扩张市场份额。近期 AMD 宣布在 7nm 节点采用台积电工艺,其长期合作的代工厂 GlobalFoundries 放弃 7nm 研发。一方面,由此可见赛道壁垒持续提高,GlobalFoundries 7nm 技术进展已无法满足 AMD 需求,台积电在有限的未来先进工艺代工中难以看到对手。另一方面,CPU 已经进入 Fabless + Foundry 阶段,英特尔与 AMD 之间的竞争实质上变为英特尔作为 IDM 与台积电代工工艺的竞争。由于台积电 2018 年 Q2 已量产 7nm 工艺,AMD 有望从 2019 年上半年逐渐出货7nmCPU 产品,而英特尔 10nm 预计 2019 下半年量产,实际出货恐延后至 2020 年。AMD有望工艺领先 Intel 一年左右,未来一年内在服务器端和个人电脑端 AMD 有望持续扩张市场份额,预计 AMD 与台积电双双获益。

-

amd

+关注

关注

25文章

5647浏览量

139028 -

cpu

+关注

关注

68文章

11218浏览量

222954 -

先进制程

+关注

关注

0文章

89浏览量

8977

原文标题:【AET原创】先进制程竞争已成为影响CPU的决定因素

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

那么龙芯CPU性能如何呢?

一个提升蜂鸟E203性能的方法:乘除法器优化

目前最先进的半导体工艺水平介绍

树莓派5超频指南:安全高效地提升性能!

Arm KleidiAI与XNNPack集成实现AI性能提升

基于纳米流体强化的切割液性能提升与晶圆 TTV 均匀性控制

快手上线鸿蒙应用高性能解决方案:数据反序列化性能提升90%

前端性能优化:提升用户体验的关键策略

FDD网络性能提升的方法

台积电2纳米制程技术细节公布:性能功耗双提升

HDI盲埋孔工艺及制程能力你了解多少?

台积电分享 2nm 工艺深入细节:功耗降低 35% 或性能提升15%!

先进的制程工艺提升对于CPU性能提升影响明显

先进的制程工艺提升对于CPU性能提升影响明显

评论