加利福尼亚州圣何塞 - 制造商设备供应商佳能公司的一位官员警告说,下一代平版印刷术(NGL)面临着新的障碍,可能会威胁到IC产业转向低于40纳米的芯片制造业。

Current 193在65纳米节点之后,-nm光学工具可能会碰壁,这促使人们需要65纳米及以上的新解决方案。浸入式光刻技术仍然是当前和“干燥”193纳米工具之后最有前途的技术,但评委会仍然不清楚该技术是否可以处理晶圆 - 大批量生产。

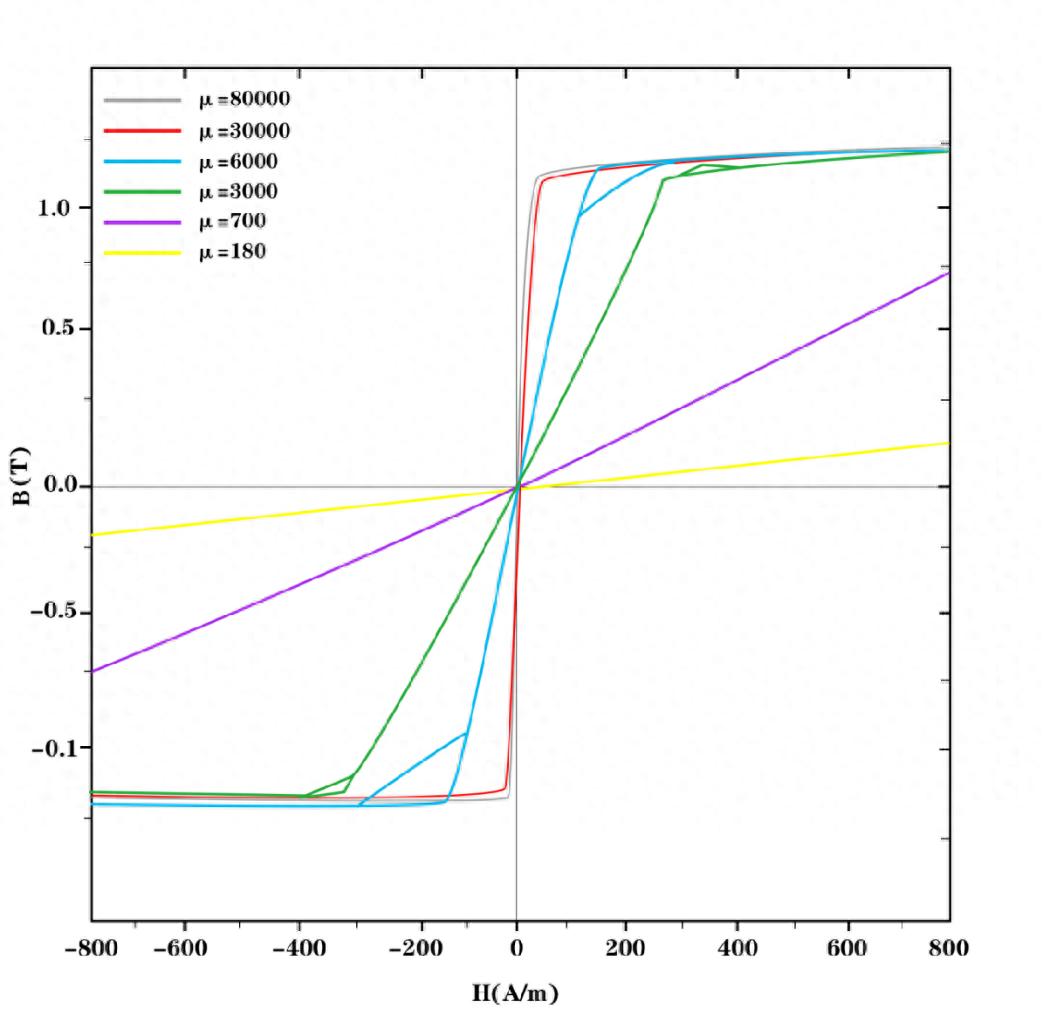

电子投影光刻(EPL)缺乏客户群,而极紫外(EUV)技术显然已经遇到了一个新的,无法预料的障碍 - 可行的光刻胶。

EUV应该在2009年之前投入生产32纳米节点。在EUV进入晶圆厂批量生产之前,该行业必须解决几个问题,最明显的是电源。

在最近的日本EUV活动中,平版印刷者发现了一个新问题。 EUV“40nm以下的化学放大抗蚀剂图像是不可接受的,”光学设备供应商佳能(东京)的研究员Phil Ware周四(11月18日)在国际Sematech全球经济研讨会上发表演讲。

过去,EUV支持者声称目前的抗蚀剂适合生产。然而,Ware表示EUV将需要“更灵敏的抗蚀剂”,以便EUV工具处理低于40纳米的晶圆。 “这是业界必须克服的问题之一,”韦尔说。

“EUV看起来不确定,”他说。 “所有与EUV相同的问题仍然在列表中,尽管所有的资金都花在了这个行业。如果EUV没有来自32纳米节点,那将是22纳米的挑战。”

这并不是说其他NGL候选人都是扣篮,包括EPL。 “EPL有一个不同的问题:没有客户,”Ware说。

甚至还有一些关于沉浸式光刻的问题,这应该在2006年和2007年的时间框架内出现。虽然该行业看好沉浸,但该技术尚未在生产工厂生产晶圆。 “我们正在等待的是生命的证据,”他说。

沉浸似乎也有一些理论上的限制。有些人认为沉浸可以扩展到22纳米节点。 Ware指出,先进的193纳米浸没工具加上折射率为1.6的“调味水”,只能处理低至40纳米的晶圆。

“你还需要(解决方案)在30纳米,“他说。使用157纳米工具进行浸入可能超过40纳米,但该技术仍然缺乏合适的157纳米镜头材料。他说,没有可行的157纳米浸泡液体。

-

芯片

+关注

关注

462文章

53535浏览量

459137 -

EUV

+关注

关注

8文章

614浏览量

88527

发布评论请先 登录

在物联网设备面临的多种安全威胁中,数据传输安全威胁和设备身份安全威胁有何本质区别?

芯源半导体安全芯片技术原理

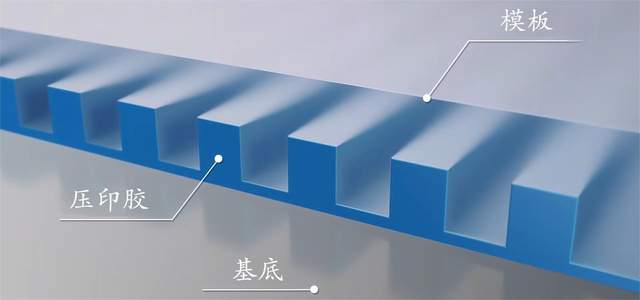

压电纳米定位系统如何重塑纳米压印精度边界

超声波指纹模组灵敏度飞升!低温纳米烧结银浆立大功

全球芯片产业进入2纳米竞争阶段:台积电率先实现量产!

碳纳米管在EUV光刻效率中的作用

Litho路障威胁到40纳米以下的芯片生产

Litho路障威胁到40纳米以下的芯片生产

评论