一、铺铜的原因:

1.EMC,对于大面积的地或电源铺铜,会起到屏蔽作用,有些特殊地,如PGND起到防护作用。

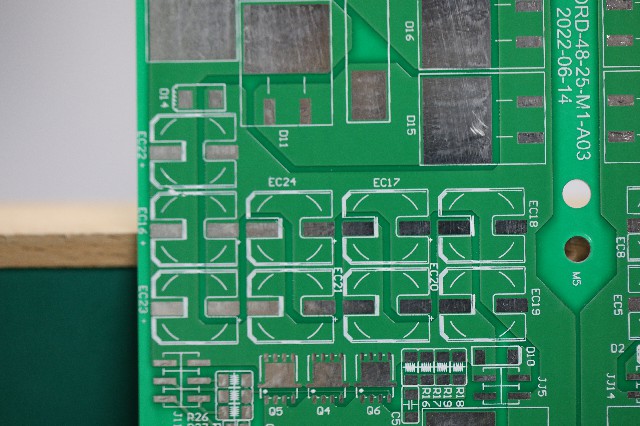

2.pcb工艺要求,一般为了保证电镀效果,或者层压不变形,对于布线较少的pcb板层铺铜。

3.信号完整性要求,给高频数字信号一个完整的回流路径,并减少直流网络的布线。当然还有散热,特殊器件安装要求铺铜等等原因。

二、铺铜的好处:

铺铜最大的好处是降低地线阻抗(所谓抗干扰也有很大一部分是地线阻抗降低带来的)数字电路中存在大量尖峰脉冲电流,因此降低地线阻抗显得更有必要一些,普遍认为对于全由数字器件组成的电路应该大面积铺地,而对于模拟电路,铺铜所形成的地线环路反而会引起电磁耦合干扰得不偿失(高频电路例外)。因此,并不是是个电路都要普铜的(BTW:网状铺铜比整块整块的铺性能要好)

三、铺铜的意义在于:

1.铺铜和地线相连,这样可以减小回路面积

2.大面积的铺铜相当于降低了地线的电阻,减小了压降从这两点上来说,不管是数字地,或模拟地都应该铺铜以增加抗干扰的能力,而且在高频的时候还应该把数字地和模拟地分开来铺铜,然后用单点相连,该单点可以用导线在一个磁环上绕几圈,然后相连。不过如果频率不算太高的话,或者仪器的工作条件不恶劣的话,可以相对放宽些。晶振在电路中可以算做一个高频发射源,你可以在周围铺铜,然后将晶振的外壳接地,这样会好一点。

四、铺铜的整块与网格的区别:

具体的来分析一下大概有3种作用:

1.美观;

2.抑制噪声;

3.为了减少高频干扰(在电路板上的理由w ww.pcblx.com)根据走线的准则:电源跟地层尽可能走宽为什么要还要加网格啊不是跟原理不符合吗?如果从高频的角度来看的话更是不对了在高频布线时最忌讳的就是尖锐的走线,在电源层有n多的90度则问题多多。其实为什么那样做完全是工艺的要求:看看那种手工焊的有没有那样画,几乎没有;你看到有这样画的肯定上面有表帖芯片的那时因为在贴片的时候有一种工艺叫波峰焊他要对板子局部加热如果全铺铜的话2面的比热系数不一样板子就翘起来而板子一翘起来问题就来了,在上钢罩(也是工艺的需要)对芯片的pin很容易出错废品率就直线上去了其实这个做法也是有缺点的:在我们现在的腐蚀工艺下:菲林很容易粘在上面这样的话,在后面强酸工程中,那个点可能腐蚀不了,废品也不少,但是只有的话,只是板子坏了而上面是芯片跟板子一起完蛋!从这个角度来看的话,你懂为什么要那样画了吗?当然了,也有的表贴的没有加网格,从产品的一致性的角度来看问题的话,可能有2中情况:a.他的腐蚀工艺很好;b.不用波峰焊而是采用了更高级的回炉焊,但是这样的话,整个流水线的投资要上去3-5倍。

责任编辑:ct

-

PCB设计

+关注

关注

396文章

4939浏览量

95785 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44715

发布评论请先 登录

07. 如何在Allegro中设置可以走线但不能铺的铜区域?| 芯巧Allegro PCB 设计小诀窍

高速PCB工程师必看:用仿真三步法,让铺铜从“隐患”变“保障”

PCB设计 | AI如何颠覆PCB设计?从手动布线到智能自动化的30年演进

PCB设计与打样的6大核心区别,看完少走3个月弯路!

电子电路当中 “地” 的介绍

高速PCB设计EMI避坑指南:5个实战技巧

深度解读PCB设计布局准则

上海图元软件国产高端PCB设计解决方案

高速PCB铺铜到底怎么铺

PCB设计,轻松归档,效率倍增!

高密PCB设计秘籍:BB Via制作流程全解析

为什么要在pcb设计当中铺上铜

为什么要在pcb设计当中铺上铜

评论