敷铜作为PCB设计的一个重要环节,不管是国产的***PCB设计软件,还国外的一些Protel,PowerPCB都提供了智能敷铜功能,那么怎样才能敷好铜,我将自己一些想法与大家一起分享,希望能给同行带来益处。

所谓覆铜,就是将PCB上闲置的空间作为基准面,然后用固体铜填充,这些铜区又称为灌铜。敷铜的意义在于,减小地线阻抗,提高抗干扰能力;降低压降,提高电源效率;与地线相连,还可以减小环路面积。也出于让PCB 焊接时尽可能不变形的目的,大部分PCB 生产厂家也会要求PCB 设计者在PCB 的空旷区域填充铜皮或者网格状的地线,敷铜如果处理的不当,那将得不赏失,究竟敷铜是“利大于弊”还是“弊大于利”?

大家都知道在高频情况下,印刷电路板上的布线的分布电容会起作用,当长度大于噪声频率相应波长的1/20 时,就会产生天线效应,噪声就会通过布线向外发射,如果在PCB 中存在不良接地的敷铜话,敷铜就成了传播噪音的工具,因此,在高频电路中,千万不要认为,把地线的某个地方接了地,这就是“地线”,一定要以小于λ/20 的间距,在布线上打过孔,与多层板的地平面“良好接地”。如果把敷铜处理恰当了,敷铜不仅具有加大电流,还起了屏蔽干扰的双重作用。

敷铜一般有两种基本的方式,就是大面积的敷铜和网格铜,经常也有人问到,大面积覆铜好还是网格覆铜好,不好一概而论。为什么呢?大面积敷铜,具备了加大电流和屏蔽双重作用,但是大面积覆铜,如果过波峰焊时,板子就可能会翘起来,甚至会起泡。因此大面积敷铜,一般也会开几个槽,缓解铜箔起泡,单纯的网格敷铜主要还是屏蔽作用,加大电流的作用被降低了,从散热的角度说,网格有好处(它降低了铜的受热面)又起到了一定的电磁屏蔽的作用。但是需要指出的是,网格是使由交错方向的走线组成的,我们知道对于电路来说,走线的宽度对于电路板的工作频率是有其相应的“电长度“的(实际尺寸除以工作频率对应的数字频率可得,具体可见相关书籍),当工作频率不是很高的时候,或许网格线的作用不是很明显,一旦电长度和工作频率匹配时,就非常糟糕了,你会发现电路根本就不能正常工作,到处都在发射干扰系统工作的信号。所以对于使用网格的同仁,我的建议是根据设计的电路板工作情况选择,不要死抱着一种东西不放。因此高频电路对抗干扰要求高的多用网格,低频电路有大电流的电路等常用完整的铺铜。

说了这么多,那么我们在敷铜中,为了让敷铜达到我们预期的效果,那么敷铜方面需要注意那些问题:

1.如果PCB的地较多,有SGND、AGND、GND,等等,就要根据PCB板面位置的不同,分别以最主要的“地”作为基准参考来独立覆铜,数字地和模拟地分开来敷铜自不多言,同时在覆铜之前,首先加粗相应的电源连线:5.0V、3.3V等等,这样一来,就形成了多个不同形状的多变形结构。

2.对不同地的单点连接,做法是通过0欧电阻或者磁珠或者电感连接;

3.晶振附近的覆铜,电路中的晶振为一高频发射源,做法是在环绕晶振敷铜,然后将晶振的外壳另行接地。

4.孤岛(死区)问题,如果觉得很大,那就定义个地过孔添加进去也费不了多大的事。

5.在开始布线时,应对地线一视同仁,走线的时候就应该把地线走好,不能依靠于覆

铜后通过添加过孔来消除为连接的地引脚,这样的效果很不好。

6.在板子上最好不要有尖的角出现(《=180度),因为从电磁学的角度来讲,这就构成的一个发射天线!对于其他总会有一影响的只不过是大还是小而已,我建议使用圆弧的边沿线。

7.多层板中间层的布线空旷区域,不要敷铜。因为你很难做到让这个敷铜“良好接地”

8.设备内部的金属,例如金属散热器、金属加固条等,一定要实现“良好接地”。

9.三端稳压器的散热金属块,一定要良好接地。 晶振附近的接地隔离带,一定要良好接地。总之:PCB 上的敷铜,如果接地问题处理好了,肯定是“利大于弊”,它能减少信号线的回流面积,减小信号对外的电磁干扰。

责任编辑:ct

-

PCB设计

+关注

关注

396文章

4937浏览量

95730 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44706

发布评论请先 登录

四探针测试:铜浆料的配方和工艺对电阻率的影响

热压键合工艺的技术原理和流程详解

为什么铜缆是企业无线技术的支柱?

金属淀积工艺的核心类型与技术原理

半导体“光刻(Photo)”工艺技术的详解;

芯片键合工艺技术介绍

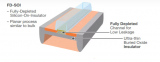

SOI工艺技术介绍

工艺与材料因素导致铜基板返修的常见问题

从微米到纳米,铜-铜混合键合重塑3D封装技术格局

用于 ARRAY 制程工艺的低铜腐蚀光刻胶剥离液及白光干涉仪在光刻图形的测量

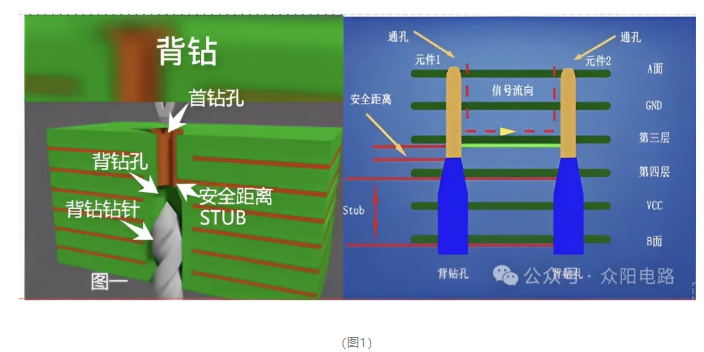

众阳电路背钻工艺技术简介

敷铜工艺技术你掌握的如何

敷铜工艺技术你掌握的如何

评论