本系列的第1部分描述了数字信号如何通过PC板传播[参考文献1]。 1,2,5,6]。在第2部分中,我们将研究特定的电路板设计,以实现低EMI。我在客户的电路板设计中看到的最大问题是层叠不良。

重申第1部分中的两个基本规则并实现数字信号电源(瞬态)是在电介质层中移动的电磁波,我们看到PC板设计有两个非常重要的原则:

PC板上的每个信号和电源走线(或平面)都应该

传输线中的数字信号传播实际上是铜迹线和GRP之间空间中电磁场的移动。

要构建传输线,你需要两个相邻的金属片来捕获或包含场地。例如,相邻接地返回平面(GRP)上的微带线或与GRP相邻的带状线或与GRP相邻的功率迹线(或平面)。例如,在电源和接地参考平面之间定位多个信号层将导致快速信号的真正EMI问题。观察这两个规则将决定层叠。

换句话说,每个信号或功率跟踪(路由功率)必须具有相邻的GRP,并且所有功率平面应具有相邻的GRP。多个GRP应与拼接过孔矩阵连接在一起。在本文中,我们将研究几种堆叠设计。

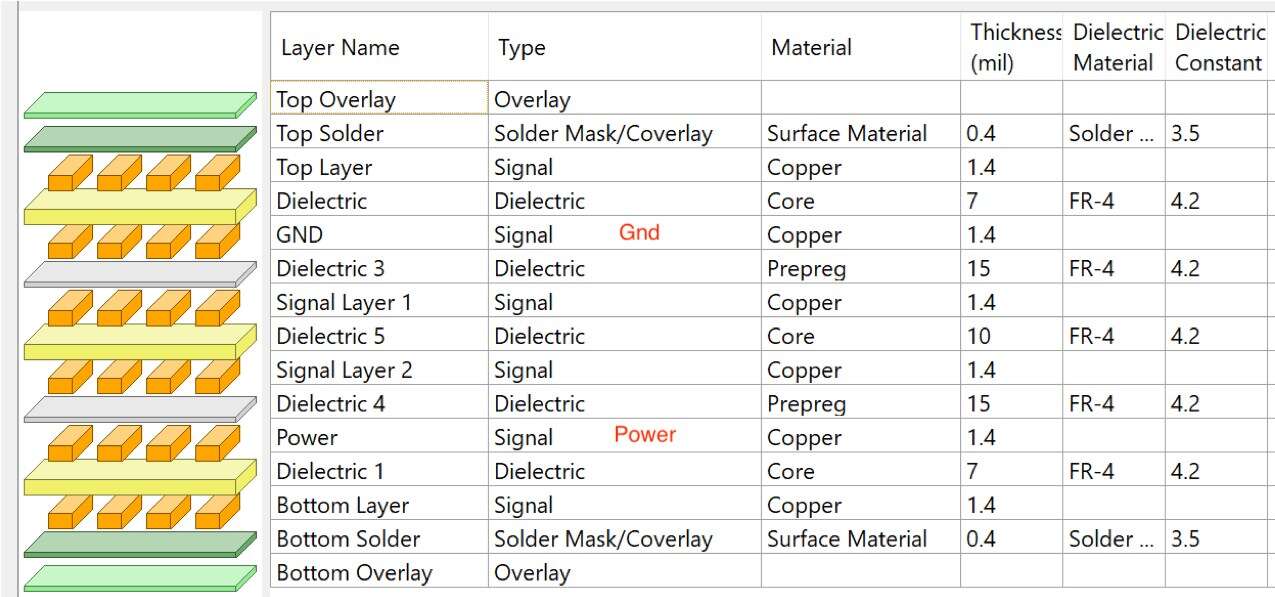

典型的六层设计(Altium)

我经常看到的一个叠加是这个六层设计(图1)。这在20世纪90年代到21世纪初可能运行良好,但是今天的速度和混合信号技术要快得多,这是EMI灾难的秘诀。这有两个问题:底部的两个信号层以电源平面为参考,电源和接地返回平面不相邻且距离太远。

图1.一种非常常见但很差的EMI叠层设计(6层示例)。信号层4和6以功率为参考,而GRP和功率平面不相邻,其间有两个信号层。这将耦合这两个信号层上的电源瞬变。

除少数例外(一些DDR RAM电源和信号(例如)电流想要返回其源,这些源以GRP为参考。将这些信号引用到电源平面是非常具有EMI风险的,因为没有明确定义的返回路径,除了通过平面到平面的电容,在这种情况下相对较小。此外,返回路径中的这些间隙导致场泄漏到电路板介电层的其他区域。反过来,这会导致交叉耦合和辐射EMI。

当我们将功率和GRP分成两个信号层时,会出现第二个问题。任何电网瞬变都将在介电层内交叉耦合,沿着路径耦合到层3和4上的任何信号迹线。如果这些平面间隔超过3-4密耳,您也会失去任何平面到平面的电容效益。

以下是几个想法适用于符合数字信号传播传输线方面的PC板叠加。

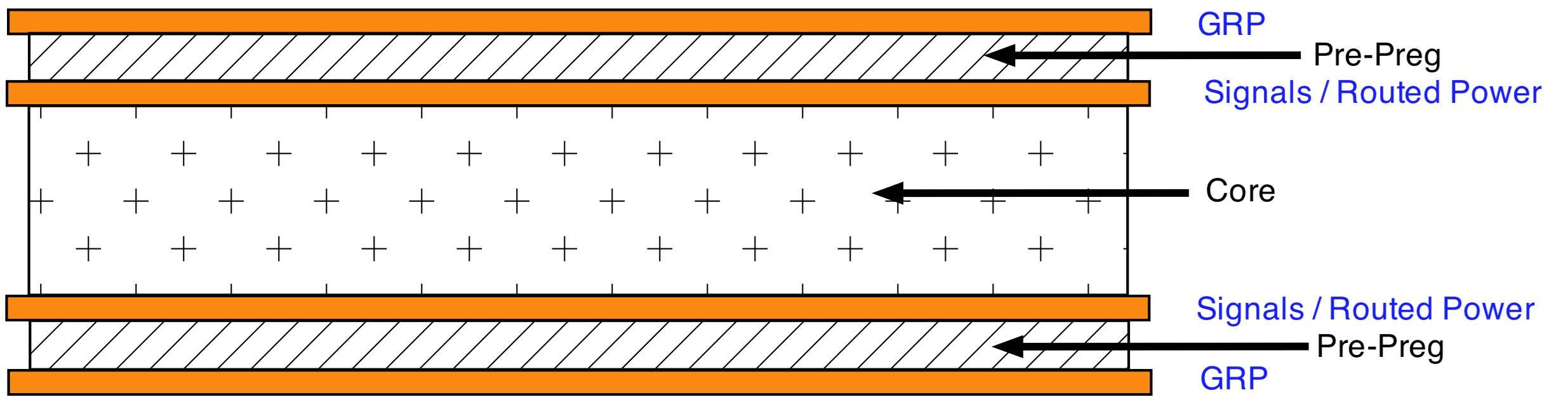

四层板:设计1

良好的四层电路板堆叠,可提高EMI(图2)。我们使用路由或倾倒功率以及第2层和第3层上的信号来代替电源平面。因此,每个信号/功率迹线与GRP相邻。此外,只要两个GRP通过拼接过孔矩阵连接在一起,就可以轻松地在所有层之间运行过孔。如果沿着周边(例如,每隔5mm)运行一排缝合过孔,则会形成法拉第笼。

图2.这种良好的四层电路板叠层可提高EMI,使信号和布线功率保持在接地参考平面附近。

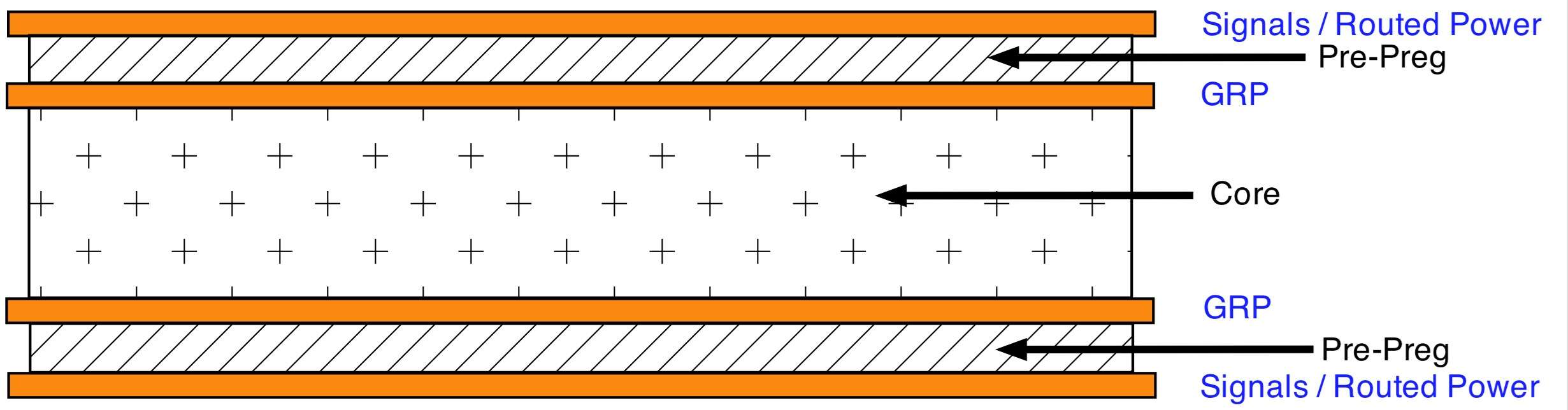

四层板:设计2

另一方面,如果您更愿意访问信号和路由/倾倒的电源线,您可以简单地反转层对,这样两个GRP层位于中间,两个信号层位于中间在顶部和底部,具有布线功率和足够的去耦电容,而不是电源平面(图3)。

图3.这种用于改善EMI的良好的四层电路板叠层将接地参考平面放置在电路板内。结果

对于这两种设计,您希望运行一种缝合过孔图案,将两个GRP连接起来,最大距离为1厘米。

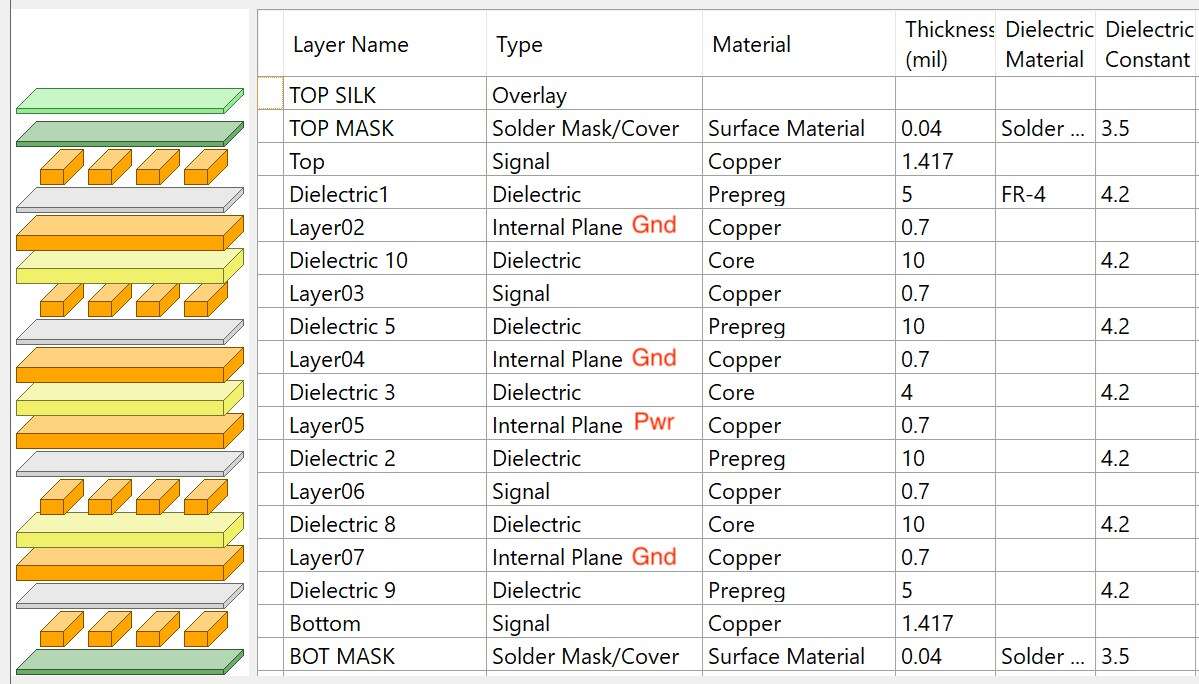

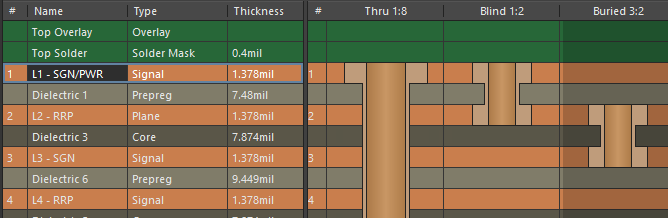

八层板(Altium)

四层和八层板设计(图4)遵循保持良好传输线设计的两个基本规则。此外,对于八层设计,功率和GRP平面现在相距4密耳,提供相当好的平面到平面电容。更接近甚至会更好。例如,1密耳至3密耳的间隔对于最小化EMI是理想的。所有GRP应与1 cm的过孔图案拼接在一起。

图4.良好的EMI叠层设计(8层示例)。所有信号层都参考相邻的GRP,而功率也参考相邻的GRP。

当然,在信号和GRP或功率和GRP之间创建正确的传输线对还有很多次迭代。

两层电路板怎么样?

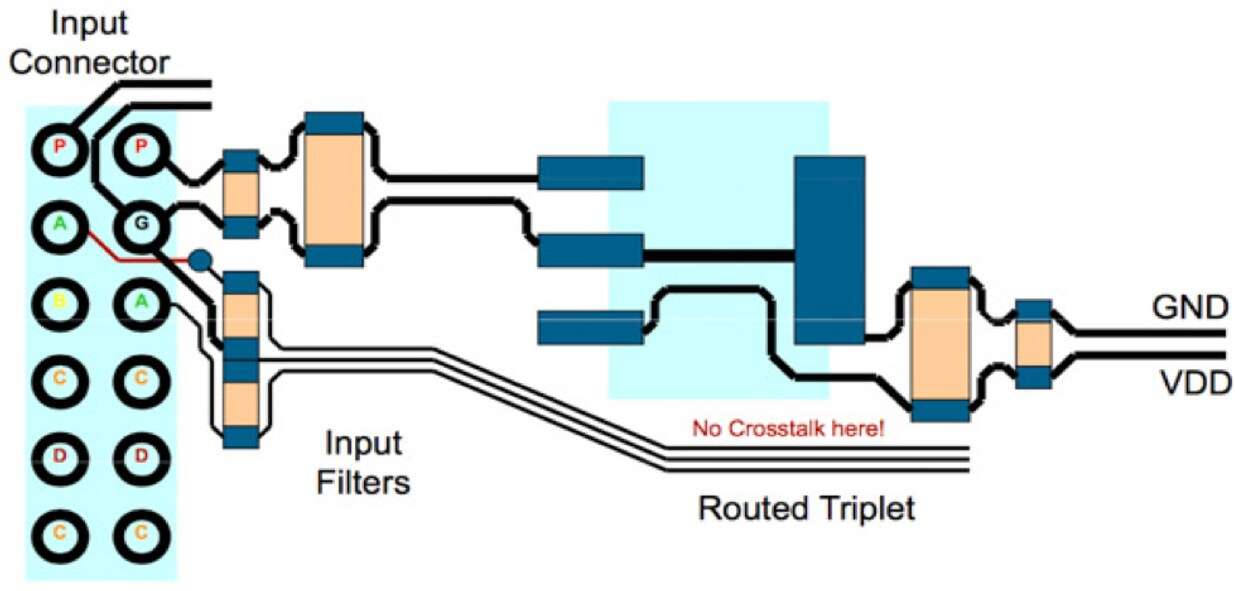

简单,只需在第1层运行信号和路由电源,并在第2层使用GRP。那么,这可能适用于昨天的技术。在今天的技术中,我们经常需要使用至少两层来运行信号。答案是在两条信号走线之间运行“三联体”和接地回路(图5)。这是恩智浦半导体高级应用工程师Daniel Beeker的一个想法[参考文献5]。

图5.信号路由三元组的示例,以及尝试保留路由功率的传输线原理。礼貌:Daniel Beeker,恩智浦半导体

在这里,我们看到了保护路由功率的传输线特性。该示例还显示了模拟信号迹线,它们之间具有接地返回迹线 - 路由“三重态”。由于在每个信号走线和返回走线之间充分捕获电磁场,因此几乎没有场泄漏。

如果您愿意要了解更多有关在PC板上设计EMI合规性的信息,我还建议Rick Hartley作为他为期2天的研讨会的优秀来源(参考文献6)。最后,我要感谢Ralph Morrison,Dan Beeker和Rick Hartley,他们真正教我电路板中的快速信号[参考文献3,4,5,6]。

本系列的第3部分将讨论电路部分的划分,高速走线的布线以及一些其他布局实践,以帮助降低EMI。

-

pcb

+关注

关注

4392文章

23750浏览量

421066 -

emi

+关注

关注

54文章

3864浏览量

134202 -

可制造性设计

+关注

关注

10文章

2065浏览量

16368 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44402 -

华秋DFM

+关注

关注

20文章

3513浏览量

6156

发布评论请先 登录

叠层固态电容:小型化封装,释放PCB更多空间

晶科能源再度实现钙钛矿/TOPCon叠层电池转换效率突破

叠层固态电容的性能优势

贴片电感代理-叠层电感的实际应用

捷多邦专家解读:如何选择最优PCB叠层方案?

HDMI2.0滤波保护叠层共模滤波器介绍

效率超30%!双面钙钛矿/晶硅叠层电池的IBC光栅设计与性能优化

如何设计用于EMI的PCB基本叠层

如何设计用于EMI的PCB基本叠层

评论