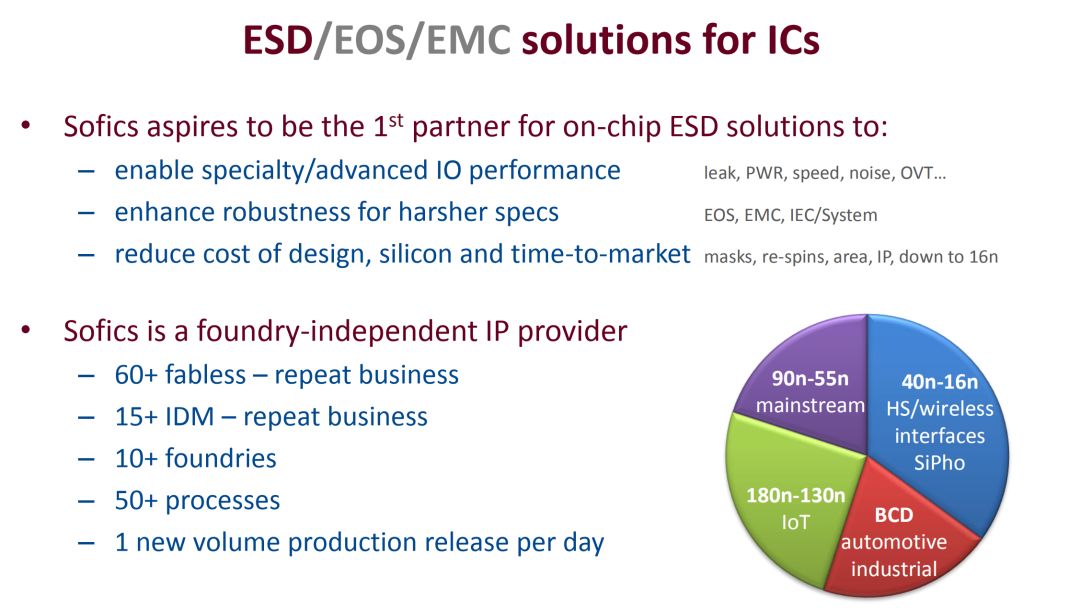

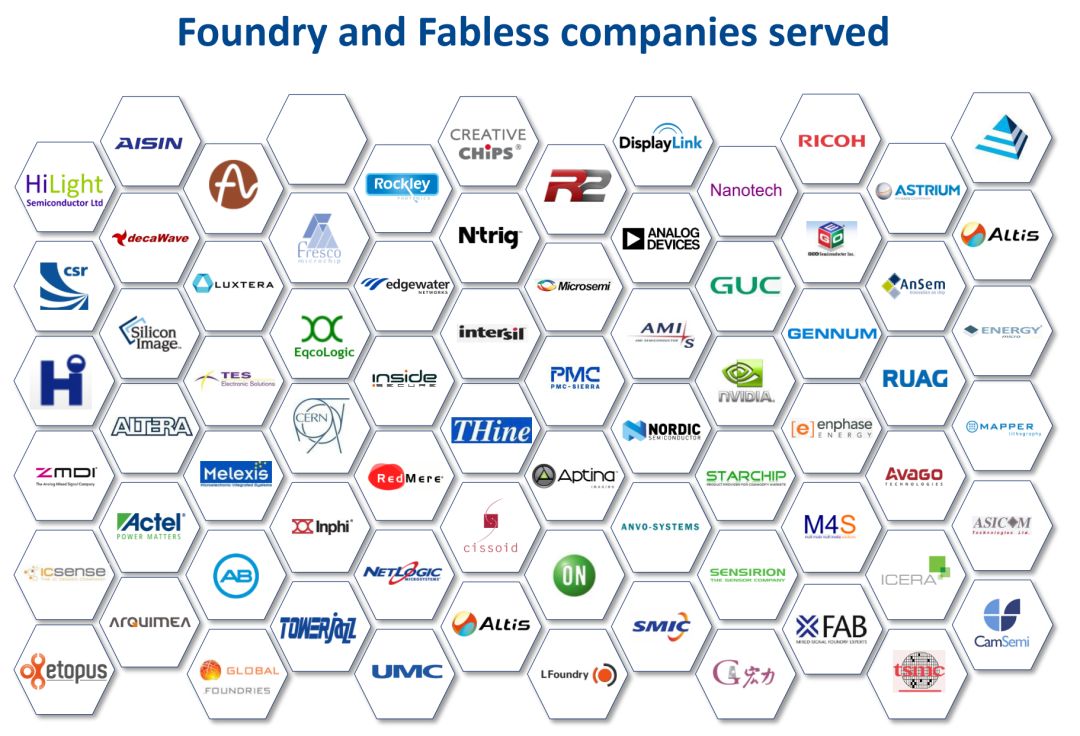

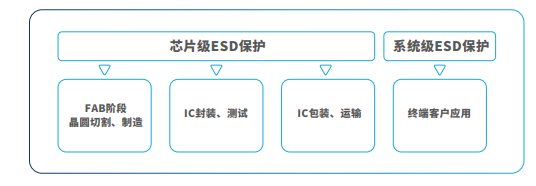

静电防护是IC设计中不可缺失的一部分,一般来说,ESD在比较大的设计公司或者半导体厂都有自己的专属部门。然而,随着技术节点的推进,广泛的应用,ESD的问题越来越变得防不胜防。为了和国内设计公司和半导体厂实现双赢,本篇文章介绍一家专注于on-chip ESD资源的比利时公司Sofics,希望能够给大家参考,并且有机会合作,实现双赢。 公司的On-chip ESD IP覆盖了很多领域,比如 IOT, 硅光电,汽车电子,医疗器械,高速电路SERDES,防辐射, SOI,FINFET, 超低功耗, 3DIC等等。 我们服务过的合作伙伴也是超过了80多家,平均每天有一个量产的产品公布。从下面的图中,大家可以看到,我们服务的客户主要集中在欧美,日本等等,中国目前的客户还是相对比较少。因此我们坚信,随着设计公司对产品的精益求精,国内会有越来越多的公司需要定制的ESD,因为私人定制的on-chip ESD 能给设计公司的产品,带来更多附加价值。

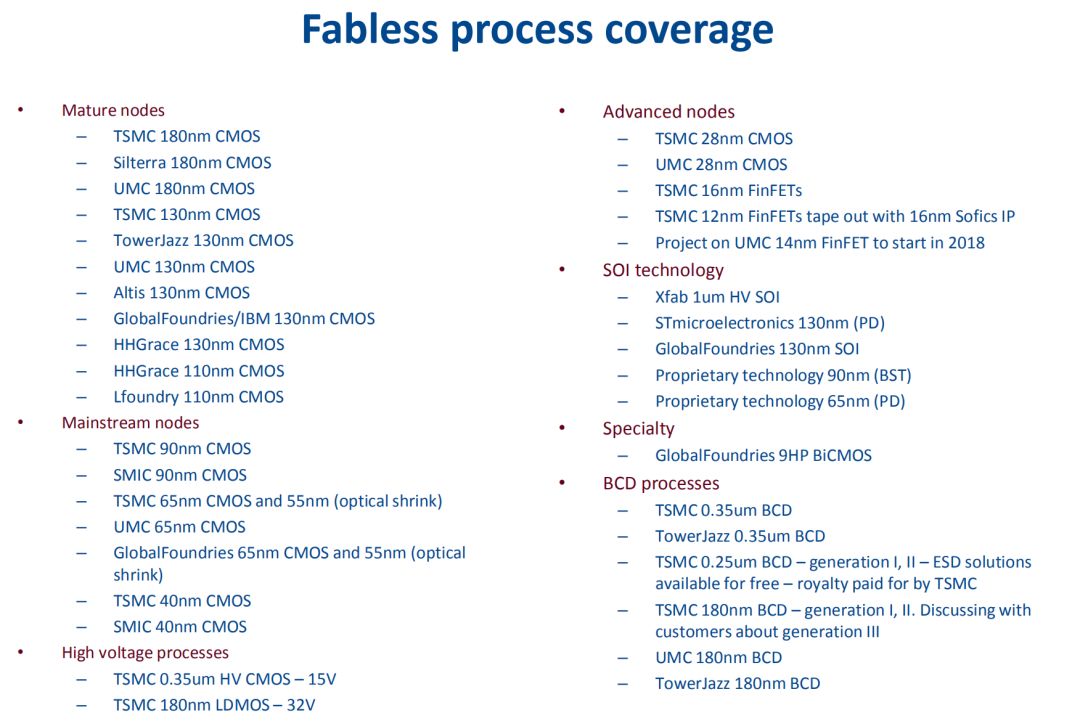

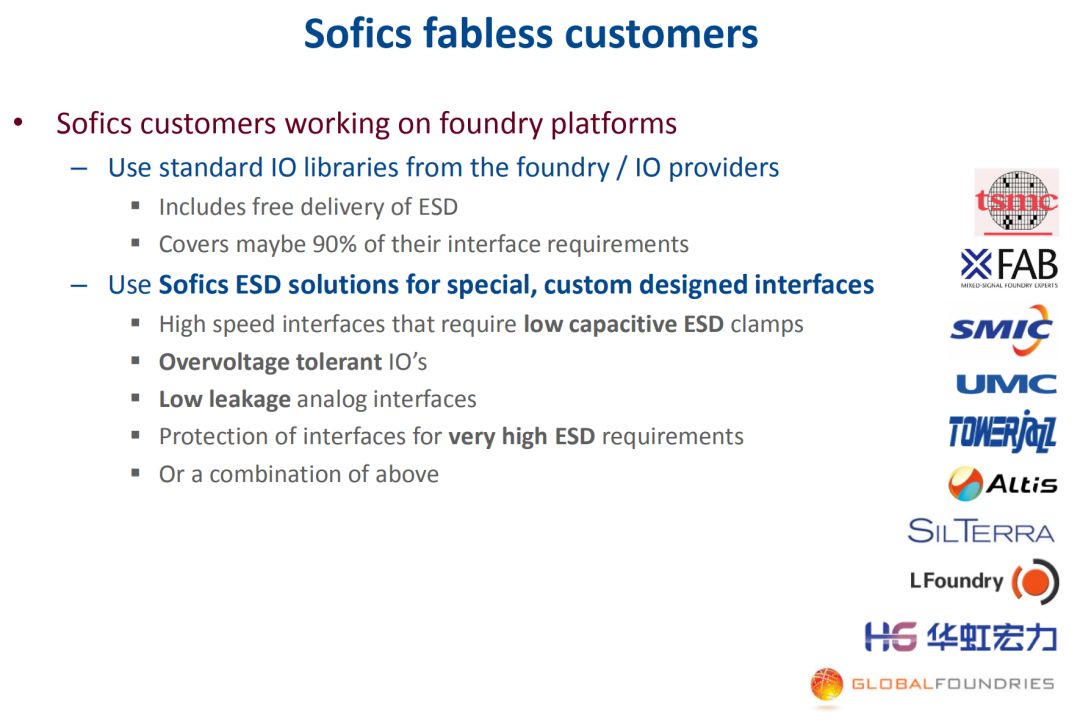

SOFICS的ESD私人定制解决方案,使特殊应用变为可能,产品性能得到提升,减少了产品的上市时间。至于具体的服务客户和工艺节点,可以参考下面两张图片。

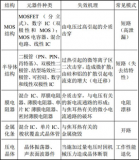

因为对于不同的产品应用,接口,ESD 参数需求(HBM,CDM,MM)是千变万化的。半导体厂能解决80-90%客户的需求,但是对于高速界面,超高压的ESD,IO的超电压需求, 超低漏电的模拟界面等等,还是需要给出私人定制的方案。Sofics 的ESD解决方案,恰恰满足了这部分客户的私人定制需求。

很多朋友会疑问,采用SOFICS的ESD解决方案有什么优点吗,总的来说,因为有很多项目经验,成熟的解决方案,可以直接用到客户的产品中,让客户减少产品设计周期,使其保持在新产品,高性能方面的优势。同时,对于先进节点,公司的ESD也能在减少芯片面积,减少MASK等方面有独特的技术,帮助设计公司减少芯片费用。

-

芯片

+关注

关注

463文章

54389浏览量

469054 -

静电防护

+关注

关注

11文章

235浏览量

48659

发布评论请先 登录

探索ESD562-Q1:汽车应用中的ESD保护解决方案

汽车网络ESD防护利器:ESD772详解

ESD 3D打印材料全面说明:PETG-ESD、ABS-ESD、PC-ESD对比

ESD测试的详细解释

ESD和EOS失效模式介绍

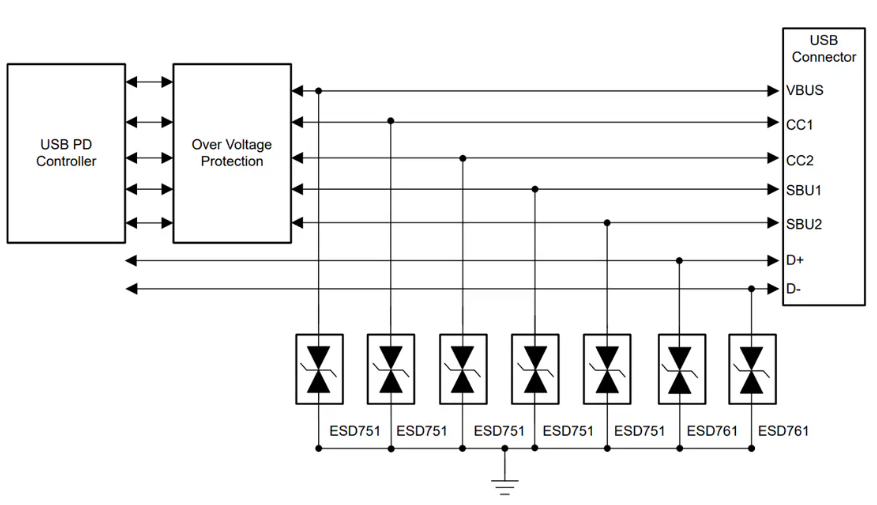

ESD751与ESD761:24V单通道ESD保护二极管技术解析

传感器走向“AI on-chip”与低功耗集成化

Abrupt Junction Varactor Diode Chip skyworksinc

【干货】ESD如何选型

概伦电子芯片级HBM静电防护分析平台ESDi介绍

关于On-chip ESD 资源的介绍和分析

关于On-chip ESD 资源的介绍和分析

评论