4月18日,在台积电召开第一季度财报会议中,台积电指出3nm技术已经进入全面开发的阶段。5月15日,三星在Foundry Forum活动中,发布了公司第一款3nm工艺的产品设计套件。由此看来,在英特尔还在纠结10nm如何向前发展之际。先进工艺的战火已经在台积电和三星的推动下,燃烧到了3nm。

去年,三星的Foundry Forum活动中强调了先进封装的重要性;今年,三星的Foundry Forum则将重点放在了先进制程的进度上。就此,我们也能够很明显地感受到,三星与台积电之间的竞争越发激烈。

战略部署:3nm何时到来?

在先进制程方面,台积电和三星的关系可以说是针尖对麦芒,两者之间的龙争虎斗也着实精彩。2015~2016年,三星Foundry先进制程能力的逐步成熟,从台积电那里夺得了不少大客户订单。2016~2017年,台积电先进制程的进一步成熟,并凭借InFO技术独揽苹果大单。2017年,三星又宣布将晶圆代工部分独立,扩大纯晶圆代工业务份额,直接对标台积电。至此以后,两者之间关于先进制程的抢滩战越来越激烈。

就目前公开的消息来看,台积电和三星都已经透露了一些关于3nm工艺节点上的进展。目前来看,5nm、3nm节点主要面向FPGA等高性能计算领域,智能处理器和5G芯片。而2019年被视为是5G商用元年,在接下来的两三年中,5G将会被大规模使用。或许,这也是两大晶圆代工龙头纷纷选择透露3nm进程的诱因之一。

2018年12月,据***媒体报道称,台积电的3nm晶圆厂方案已经获得***主管部门批准,选址***南部科技园区。据悉,台积电3nm工厂建设预计会花费超过200亿美元,同时有望带动相关供应商跟进建厂。依照台积电规划蓝图,3nm应可在2021年试产、2022年量产,成为全球第一家提供晶圆代工服务,同时解决很多AI人工智能芯片功效更强大的晶圆代工厂。

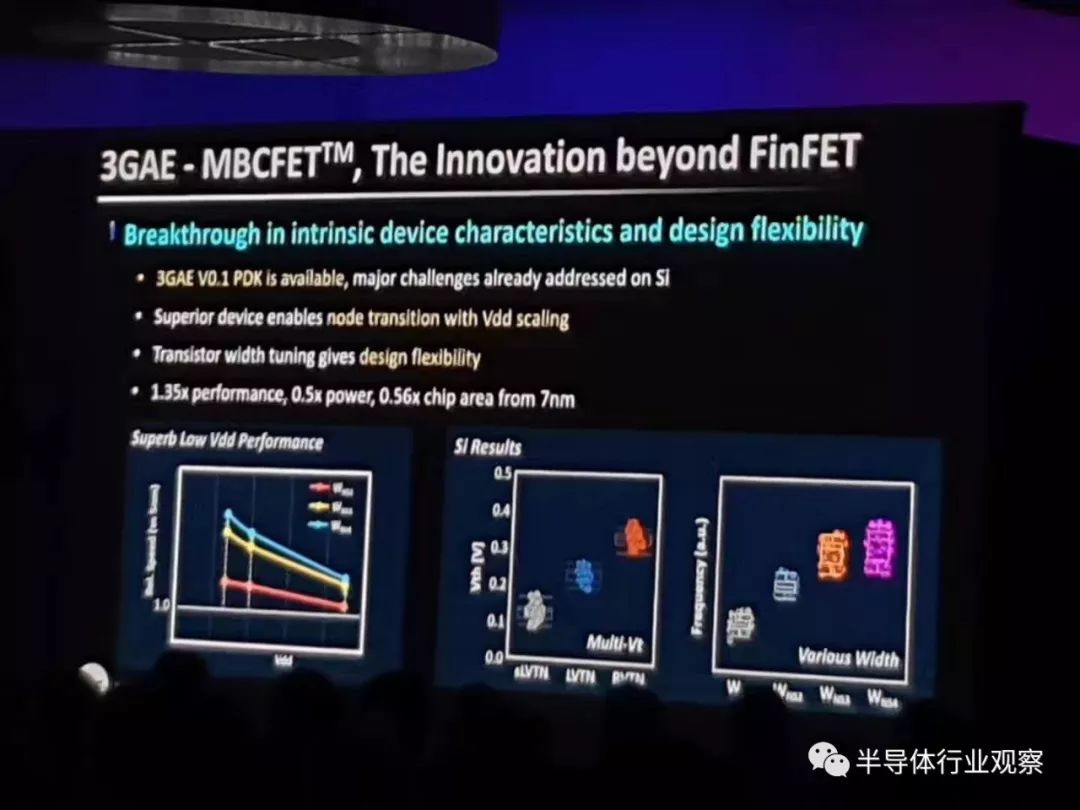

前不久,三星也公布了未来的制程工艺路线图,公司计划今年推出7nm EUV工艺,明年有5/4nm EUV工艺,2020年则会推出3nm EUV工艺,同时晶体管类型也会从FinFET转向GAA结构。据悉,三星3GAE工艺中还在开发当中,不过他们4月份就发布了3GAE工艺的PDK 1.0工艺设计套件,旨在帮助客户尽早开始设计工作,提高设计竞争力,同时缩短周转时间(TAT)。

基于GAA的工艺节点有望在下一代应用中广泛采用,例如移动、网络通讯、汽车电子、人工智能(AI)和IoT物联网等。三星还透露,通过使用全新的晶体管结构可使性能提升35%、功耗降低50%,芯片面积缩小45%。不过,三星官方没有明确3GAE工艺量产时间,但根据市场猜测,三星3nm在2021年实现量产是大概率事件。

而就以上消息来看,三星将早于台积电一年推出3nm工艺。谁能更快地推出可靠的新工艺,谁就有可能掌握在该制程上的最大话语权。为了能够赢得3nm这场抢滩战的胜利,都需要哪些技术来助攻?

助攻一:晶体管结构

目前,先进制程多数采用立体结构,即"FinFET"(鳍式场效晶体管),此结构的通道是竖起来而被闸极给包围起来的,因为形状像鱼类的鳍而得名,如此一来闸极偏压便能有效调控通道电位,因而改良开关特性。但是FinFET在经历14/16nm、7/10nm阶段后,不断拉高的深宽比(aspect ratio)让前段制程已逼近物理极限,再继续微缩的话,先不提电性是否还能有效提升,就结构而言就已有许多问题。

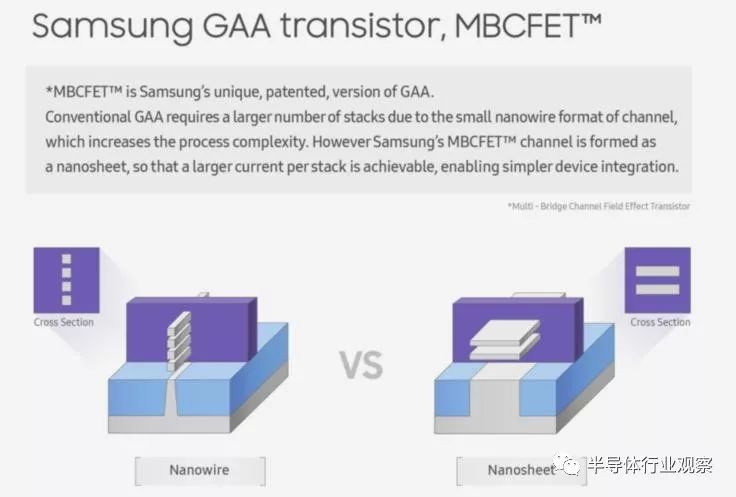

为了扩展,通道和栅极之间的接触面积需要增加,Gate-All-Around(GAA)设计被提了出来。GAA调整了晶体管的尺寸,以确保栅极也位于通道下方,而不仅仅在顶部和侧面。这允许GAA设计垂直堆叠晶体管,而不是横向堆叠晶体管。

三星方面,据公开消息整理,三星与IBM合作开发了GAAFET(Gate-All-Around)工艺节点,同时,三星也已宣布对早期工艺进行定制。三星Foundry市场副总裁Ryan Sanghyun Lee称,自2002年以来,三星一直在开发其GAA技术的专有实现,称为多桥通道FET(MBCFET)。该公司指出,其MBCFET技术使用纳米片器件来增强栅极控制,这可以显着改善晶体管的性能。据悉,它可以通过用纳米片代替Gate All Around的纳米线来实现每堆更大的电流。取代增加了传导面积,允许增加更多的栅极而不增加横向足迹。三星声称MBCFET的设计将改善工艺的开关行为,并允许处理器将工作电压降至0.75V以下。MBCFET的关键点在于该工艺与FinFET设计完全兼容,不需要任何新的制造工具。

在前不久三星举行的Foundry Forum上,三星称3nm工艺时代不再使用FinFET晶体管,而是使用全新的晶体管结构——GAA(Gate-All-Around环绕栅极)晶体管,通过使用纳米片设备制造出了MBCFET(Multi-Bridge-Channel FET,多桥-通道场效应管),该技术可以显著增强晶体管性能,主要取代FinFET晶体管技术。

在台积电方面,官方公布有关于3nm技术方面的消息较少。据芯科技消息称,台积电3nm制程技术已进入实验阶段,业内人士更透露,3nm制程在"Gate All Around(GAA) "、环绕式闸极技术上已有新突破。业内人士进一步表示,台积电已经做出环绕式闸极的结构,外型就像类圆形般,但因为尺寸比前一代缩小30%,也必须导入新材料InAsGe nanowire and Silicon nanowire,因此制程技术上相当困难,尤其是在蚀刻部分是大挑战,不过以优势来说,环绕式闸极的结构将可以改善ESD静电放电、且优化尖端放电的问题,材料厂的高管也认为,环绕式闸极的结构得以继续微缩栅长尺寸。

由此可见,GAA架构将成为3nm工艺上不可缺少的技术。

助攻二:EUV

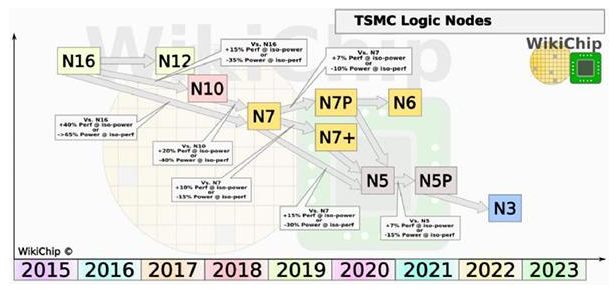

在上文三星所提到的先进制程路线图时,我们不止一次看到了EUV的身影。同时,我们也通过台积电在今年来的动作上,发现了EUV对于先进制程能够得到进一步发展的重要性——前不久,台积电宣布已完成其5纳米工艺节点的基础设施设计,该节点将利用该公司的第二代极紫外(EUV)以及深紫外(DUV)光刻技术。

据Techshop消息称,从3月底开始,台积电准备开始使用极紫外光刻技术批量生产7nm晶圆。ASML已经为台积电在2019年计划的30个系统中分配了18个。接下来,台积电的7nm EUV产量将全面运行,该公司的5nm工艺将转向风险生产状态。EUV将继续用于5nm,预计可行至3nm。到2019年底,台积电将在5nm节点上进行芯片设计,预计到2020年初量产。据悉,2018年,7nm EUV仅占台积电销售额的9%。今年,新工艺有望占其总销售额的四分之一。

在三星方面,去年 10 月,三星就宣布了准备初步生产 7nm 工艺,这是三星首个采用 EUV 光刻技术的工艺节点。据悉,三星已提供业界首批基于EUV的新产品的商业样品,并于今年年初开始量产 7nm 工艺。与其前身的10nm FinFET相比,三星的7LPP技术不仅大大降低了工艺复杂性,而且层数更少,产量更高,而且面积效率提高了40%,性能提高了20%,功耗降低了50%。到2020年,三星希望通过新的EUV系列为需要大批量生产下一代芯片设计的客户提供额外的容量。作为EUV的先驱,三星还开发了专有功能,例如独特的掩模检测工具,可在EUV掩模中执行早期缺陷检测,从而可以在制造周期的早期消除这些缺陷。据悉,三星位于韩国华成的S3生产线正在生产基于EUV的工艺的芯片产品。此外,三星还在华城部署了新的EUV生产线,该生产线预计将在2019年下半年完成,并从明年开始增产。

助攻三:封装

除此之外,先进封装也是各大代工厂的主攻方向。

此前有媒体报道称,台积电完成全球首颗3D IC封装,预计将于2021年量产。台积电此次揭露3D IC封装技术成功,正揭开半导体制程的新世代。目前业界认为,此技术主要为是为了应用在 5 纳米以下先进制程,并为客制化异质芯片铺路,当然也更加巩固苹果订单。Digitimes的研究也指出,为了搭配先进制程微缩及异质芯片整合趋势,台积电研发整合的10nm逻辑芯片及DRAM的整合扇出层叠封装(InFO-PoP),以及12nm系统单芯片与8层HBM2存储器的CoWoS封装等均进入量产,并推出整合多颗单芯片的整合扇出型基板封装(InFO-oS)、整合扇出存储器基板封装(InFO-MS)、整合扇出天线封装(InFO-AIP)等新技术。

三星推出了可与台积电晶圆级扇出型封装(InFO)抗衡的FOPLP-PoP封装,其目标2019年前为新制程建立量产系统,藉此赢回苹果供应订单。但DIGITIMES认为,FOPLP 仍面临不小的挑战,以目前 FOPLP 刚起步的状况来看,经济规模将是技术普及的最大挑战,在初期良率还不够好的状态下,FOPLP 产能要达到理想的成本优势,短期内恐不易达成。在其他先进封装上,针对2.5D封装,三星推出了可与台积电CoWoS封装制程相抗衡的I-Cube封装制程,在2019年三星晶圆代工论坛上,该公司的FD-SOI(FDS)流程和eMRAM的扩展以及一系列最先进的封装解决方案也在今年的Foundry论坛上亮相。据悉,三星今年将完成28FDS工艺,18FDS和1Gb容量eMRAM的继任者的开发。

投资规模

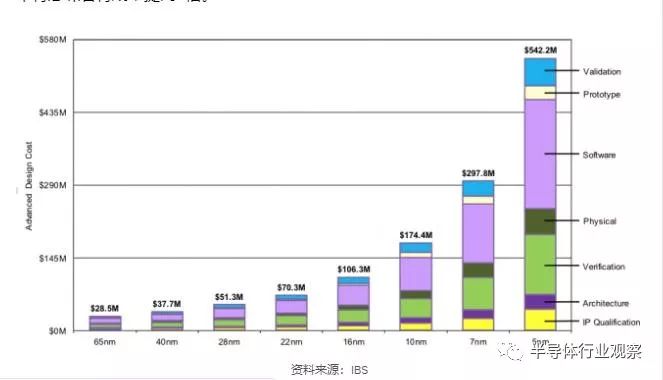

无论是晶体管架构,还是EUV,亦或是先进封装,都是先进制程在向前发展的过程中不可缺少的技术。但每一项技术,都需要大量的资金来做支持。

国际商业战略(IBS)首席执行官汉德尔•琼斯(Handel Jones)曾表示,“该行业需要大幅增加功能,并小幅增加晶体管成本,以证明使用3纳米。3nm工艺开发成本将达到40亿至50亿美元,而每月40,000片晶圆的晶圆厂成本将达到150亿至200亿美元。”

为此,三星电子于4月24日宣布,三星电子将在2030年投资1150亿美元用于系统半导体领域的研发和生产技术。根据已批准的未来12年计划,这1150亿美元中,将投资73万亿韩元(634亿美元)用于韩国的研发(这可能意味着芯片研发和工艺技术的研发),60万亿韩元(521亿美元)将投资于用于制造逻辑芯片的生产设施和基础设施为各种客户。

台积电方面,根据台积电14日董事会消息称,台积电通过了1,217.81亿元资本预算,除升级先进制程产能外,也用于转换部分逻辑制程产能为特殊制程产能。台积电预定今年度资本支出金额约100亿美元至110亿美元,其中80%经费将用于3 纳米、5纳米及7纳米先进制程技术。台积电预期,今年7纳米与第二代7纳米制程将贡献约25%业绩。另外有10%经费用于先进封装与光罩,10%用于特殊制程。

三星与台积电除了在3nm制程上争夺激烈,在其他先进制程方面的碰撞也不少。自2019年以来,台积电接连发布了6nm、5nm、5nm+的发展路线。三星方面,虽在7nm的进度上稍显逊色,但其EUV技术却不容小觑。另外,从本次三星积极布局3nm的动作上来看,也许,三星正在企图利用3nm技术来反超台积电。

-

芯片

+关注

关注

463文章

54463浏览量

469668 -

功耗

+关注

关注

1文章

844浏览量

33344

发布评论请先 登录

回顾台积电与三星的3nm争斗

回顾台积电与三星的3nm争斗

评论