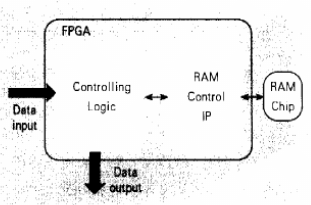

1. 背景 这篇文章主要介绍了DDR3IP核的写实现。 2. 写命令和数据总线介绍 DDR3 SDRAM控制器IP核主要预留了两组总线,一组可以直接绑定到DDR3 SDRAM芯片端口,一组是留给

2020-12-31 11:17:02 6783

6783

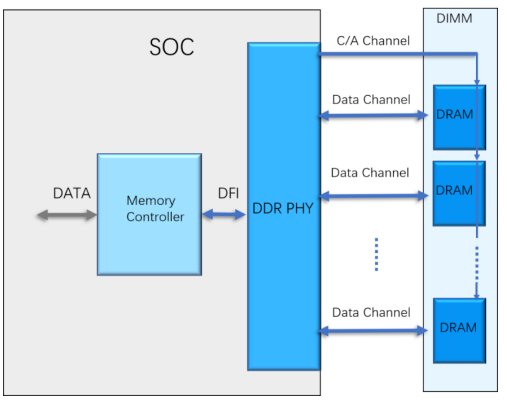

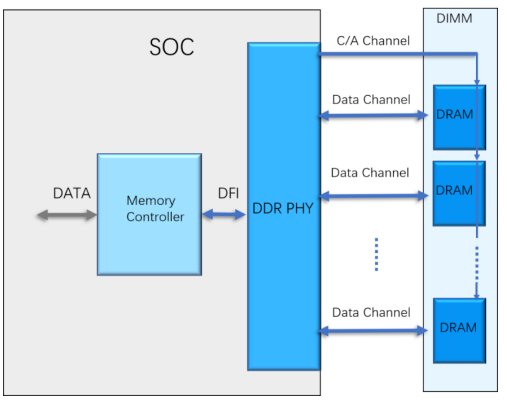

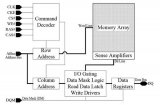

DDR PHY是DRAM和内存控制器通信的桥梁,它负责把内存控制器发过来的数据转换成符合DDR协议的信号,并发送到DRAM。

2021-04-20 11:37:25 5307

5307

DDR内存控制器是一个高度集成的组件,支持多种DDR内存类型(DDR2、DDR3、DDR3L、LPDDR2),并通过精心设计的架构来优化内存访问效率。

2025-03-05 13:47:40 3578

3578

完全可以用靠近输入输出引脚处的逻辑资源来实现DDR触发器,而且最后的结果表明,这种实现方式可以满足时序要求。 从图4中也可以看到,控制器内部有两个时钟,clk和clk_90,两者之间的相位差为90°。图中

2018-12-18 10:17:15

交叉存取来提高带宽。一个易于使用和可预测的存储器控制器,如:ECP3 DDR3存储器控制器,在用户基于其对数据处理的基本算法的了解的情况下来分配存储器缓冲区时,可以最小的硬件和软件开销来实现最大的带宽

2019-05-24 05:00:34

小,256Kb-16Mb 5.集成度低,单位容量价格高 6.静态功耗低,运行功耗大 DRAM 1.速度较慢 2.需要刷新来保持数据 3.需要MCU带外部存储控制器 4.容量大,16Mb-4Gb 5.集成度高,单位容量价格低 6.运行功耗低

2020-12-10 15:49:11

围设备。外围设备连接的引脚连接到微型计算机功能,称为输入/输出端口(I/O端口)。端口是微型计算机和外围设备连接的端子。如果您想从微型计算机打开/关闭LED,您可以通过执行程序中的端口控制来实现。端口

2021-09-10 09:14:16

6655时钟PLL配置与DDR3的配置1 时钟概述PLL与PLL控制器的逻辑组成和处理流程如图1所示。PLL控制器能够通过PLLDIV1到PLLDIV16这些分频器灵活便利的配置和修改内部的时钟信号

2018-01-24 21:27:10

4的JEDEC标准DDR4接口的变体,它包含了对完整系统支持所需的独特功能。本文将帮助工程师了解Xilinx FPGA控制器的Everspin STT-DDR4设计指南

2021-01-15 06:08:20

你好任何人都可以指导我,Xilinx ISE中的DDR控制器是否有任何IP实现。如果没有如何实现DDR控制器以上来自于谷歌翻译以下为原文Hi can any one guide me

2019-02-27 12:13:51

/ p作为输入时钟连接到CLKGENERATOR,DDR控制器在Phy侧运行800Mhz,在控制器运行200Mhz.Slave AXI总线宽度为AXI.DDRis 512bits。卡皮尔古普塔project_6.srcs.rar 6322 KB

2019-09-10 07:58:12

Rambus DRAM与CTM时钟同步输出数据。如果时钟与数据信号的布线长度等相同,则时钟与数据具有相同的延迟时间到达DRAM控制器,所以DRAM控制器可以与时钟同步接受数据。 另一方面

2008-12-04 10:16:36

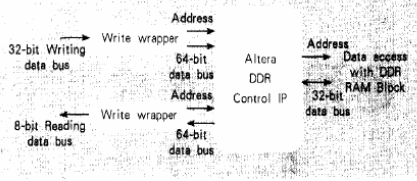

本文和设计代码由FPGA爱好者小梅哥编写,未经作者许可,本文仅允许网络论坛复制转载,且转载时请标明原作者。Altera DDR2控制器使用IP的方式实现,一般很少自己写控制器代码。ddr

2020-02-25 18:33:00

为什么XMC库不使用控制器的端口输出寄存器TESTBOARD_150PC_OUT ?

程序库仅使用端口输出修改寄存器 Pn_OMR 来设置或清除数字输出。

2024-03-06 06:17:41

我是一名labview FPGA程序员,使用的是NI 7975 fpga模块,它具有kintex 7 fpga。该模块具有外部DDR3 DRAM 0f 2GB以及kintex 7 fpga资源。数据应该从芯片到芯片之间会有多少延迟?这是DDR3 DRAM双端口(同时读写操作可能??)???

2020-05-20 14:42:11

这是我自己写ddr2控制器的写操作,但为什么写的地址不按顺序写,有谁做过吗?

2017-03-20 16:36:20

我可以使用mig生成ddr控制器(xc6vlx130t)吗?mig向导只支持ddr2和ddr3!

2020-06-12 07:32:48

请求。物理层接口前端连接至内存控制器模块,后端连接外部存储设备,其主要功能是捕获DDR3发出的数据,产生DDR3所需要的控制指令信号,并通过输入输出缓存发送所有DDR3的控制信号、地址信号以及数据信号

2018-08-02 09:34:58

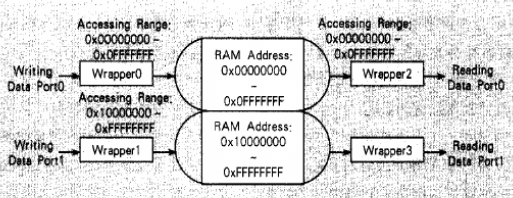

作者:吴连慧,周建江,夏伟杰摘要:为了解决视频图形显示系统中多个端口访问DDR3的数据存储冲突,设计并实现了基于FPGA的DDR3存储管理系统。DDR3存储器控制模块使用MIG生成DDR3控制器

2018-08-02 11:23:24

的DDR3存储管理系统。DDR3存储器控制模块使用MIG生成DDR3控制器,只需通过用户接口信号就能完成DDR3读写操作。DDR3用户接口仲裁控制模块将中断请求分成多个子请求,实现视频中断和图形中断的并行

2024-06-26 18:13:42

DDR控制协议

DDR3读写控制器主要用于生成片外存储器DDR3 SDRAM进行读写操作所需要的时序,继而实现对片外存储器的读写访问。由摄像头采集得到的图像数据通常数据量较大,使用片内存储资源

2025-10-21 14:30:16

如何实现双路输出控制器的设计?

2022-02-11 07:57:24

DDR3存储器控制器面临的挑战有哪些?如何用一个特定的FPGA系列LatticeECP3实现DDR3存储器控制器。

2021-04-30 07:26:55

你好使用Xilinx的任何一个端口MIG DDR2 SDRAM控制器都是我遇到了问题我有vhdl顶级系统,其中我实例化ddr2控制器我的ddr2包装器与testcase一起工作正常(由MIG提供

2019-08-19 10:47:06

你好如何在不使用DDR内存控制器的情况下设计FPGA BRAM(或任何其他内存模块_SD,DDR以外的本地等)大容量存储单元?当我通过示例设计“VC707_bist”替换DRAM控制器和BRAM

2019-04-04 15:10:55

的工作时钟频率。然而,设计至DDR3的接口也变得更具挑战性。在FPGA中实现高速、高效率的DDR3控制器是一项艰巨的任务。直到最近,只有少数高端(昂贵)的FPGA有支持与高速的DDR3存储器可靠接口的块

2019-08-09 07:42:01

嗨,我已经搜索了很多关于配置PS DRAM控制器(DDRC)板参数的信息,链接如下,http://www.xilinx.com/support/answers/46778.htm, 我想知道如何获得包装长度?谢谢!

2019-11-07 08:43:39

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器 Zynq UltraScale+ MPSoC VCU DDR 控制器是一款专用 DDR 控制器,只支持在 Zynq

2021-01-07 16:02:09

如何调试 Zynq UltraScale+ MPSoC VCU DDR 控制器?

2021-01-22 06:29:21

嵌入式控制器的输入端口设计分析,不看肯定后悔

2021-05-31 06:19:13

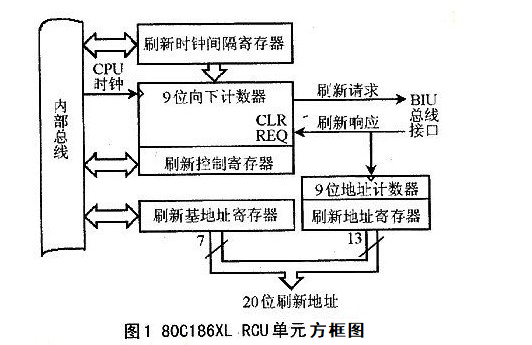

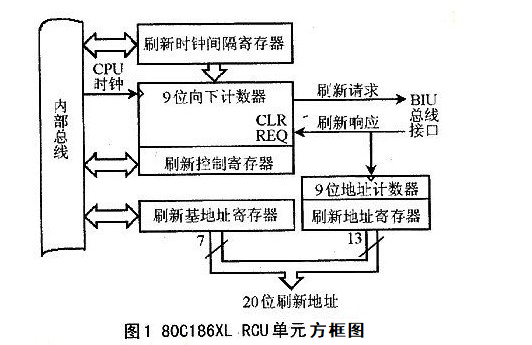

摘要:介绍怎样在嵌入式CPU 80C186XL DRAM刷新控制单元的基础上,利用CPLD技术和80C196XL的时序特征设计一个低价格、功能完整的DRAM控制器的方法,并采用VHDL语言编程实现

2011-02-24 09:33:15

学单片机的都必须清楚微控制器的输入输出,点灯是练习输出,而输入最基础的就需要去练习——按键。

2021-11-29 07:38:40

大家好,我想设计自己的DDR控制器并在FPGA上验证它。我将在verilog中实现我刚开始阅读JESDC79C DDR规格..但我很困惑如何编写那些初始化序列?请建议如何处理这个设计DDR控制器

2019-04-29 11:59:22

有没有办法重置和重新初始化 DDR 控制器?DRAM 类型是 LPDDR4。

我们的目标:我们尝试为组装有不同大小 RAM 的电路板系列实施解决方案。

为了获得可重现的结果,我们寻求在尝试下一个配置

2023-05-16 09:03:04

本文介绍了怎样在嵌入式CPU 80C186XL DRAM刷新控制单元的基础上,利用CPLD技术和80C196XL的时序特征设计一个低价格、功能完整的DRAM控制器的方法,并采用VHDL语言编程实现。

2021-04-28 07:10:38

DDR SDRAM在嵌入式系统中有哪些应用?DDR SDRAM的工作方式有哪几种?怎样去设计DDR SDRAM控制器?

2021-04-30 07:04:04

FPGA与DDR2存储器接口DDR2控制器的设计原理是什么?DDR2控制器的应用有哪些?

2021-04-30 06:28:13

设计实现了一种基于FPGA 的,可用于多数据缓存的、能够高效利用带宽的多端口SDRAM 控制器。本文使用状态机的设计思想,采用Verilog 硬件描述语言设计了时序控制程序。得到的SDR

2009-08-27 09:43:33 23

23 DDR2 SDRAM控制器的设计与实现

本文介绍了&&," -&,+. 的基本特征!并给出了一种&&," -&,+. 控制器的设计方法!详述了其基本结构和设计思想!并使用+JC:8B 公

2010-02-09 14:57:51 64

64 本文采用Altera 公司的Stratix 系列FPGA 实现了一个三端口非透明型SDRAM 控制器,该控制器面向用户具有多个端口,通过轮换优先级的设计保证了多个端口平均分配SDRAM的带宽且不会降

2010-03-03 14:37:14 11

11 本文介绍了DDR3 SDRAM 的基本特点和主要操作时序,给出了一种基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的设计方法。详述了控制器基本结构和设计思想,分析了各模块功能与设计注意事项,并

2010-07-30 17:13:55 30

30 输入电压高达38V的汽车级、四输出控制器-MAX17019

MAX17019是高输入电压、4路输出控制器,用于汽车系统。

2009-01-22 13:12:11 1338

1338 文章对适用DDR2 SDRAM控制器的结构、接口和时序进行了深入研究与分析,总结出一些控制器的关键技术特性,然后采用了自顶向下(TOP-IX)WN)的设计方法,用Verilog硬件描述语言实现控制器,

2011-09-01 16:36:29 174

174 ADI,全球领先的高性能信号处理解决方案供应商,最近推出 GPIO(通用输入/输出)端口扩展器和键盘矩阵控制器 ADP5585和 ADP5589

2011-09-14 14:17:53 2714

2714 本文提出一种新颖的解决方案:利用80C186XL的时序特征,采用CPLD技术,并使用VHDL语言设计实现DRAM控制器。

2012-02-02 11:29:58 1863

1863

带自测功能的DDR2控制器设计,感兴趣的可以看看。

2016-01-04 15:23:32 0

0 基于等价输入干扰估计器的永磁同步电机控制器的设计与实现,有兴趣的同学可以下载学习

2016-04-26 18:16:42 22

22 Xilinx FPGA工程例子源码:DDR SDRAM控制器参考设计VHDL代码

2016-06-07 11:44:14 19

19 Xilinx FPGA工程例子源码:DDR SDRAM控制器verilog代码

2016-06-07 14:13:43 40

40 基于协议控制器的DDR3访存控制器的设计及优化_陈胜刚

2017-01-07 19:00:39 16

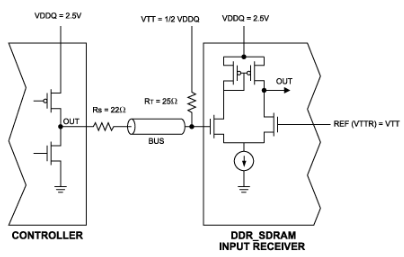

16 引言 LTC3876 是一款完整的 DDR 电源解决方案,可与 DDR1、DDR2、DDR3 和 DDR4 较低的电压兼容。该 IC 包括 VDDQ 和 VTT DC/DC 控制器和一个高精度线性

2017-05-10 16:37:39 12

12 DDR 控制器部产品营销总监 概述 DDR DRAM内存控制器要满足众多市场竞争的需求。一款出色的内存控制器必须能够增加存储器接口的带宽,满足CPU、图形处理、系统实时DRAM的延迟需求,同时符合

2017-11-18 18:23:12 3509

3509 为了解决视频图形显示系统中多个端口访问DDR3的数据存储冲突,设计并实现了基于FPGA的DDR3存储管理系统。DDR3存储器控制模块使用MIG生成DDR3控制器,只需通过用户接口信号就能完成DDR

2017-11-18 18:51:25 7989

7989

提出一种便于用户操作并能快速运用到产品的DDR2控制器IP核的FPGA实现,使用户不需要了解DDR2的原理和操作方式的情况下,依然可以通过IP核控制DDR2。简单介绍了DDR2的特点和操作原理,并

2017-11-22 07:20:50 5930

5930

DDR SDRAM的接口特性:其输入输出引脚与SSTL-Ⅱ电气特性兼容,内部提供了DDR触发器、锁相环等硬件资源。使用这些特性,可以比较容易地设计性能可靠的高速DDR RAM控制器。本文介绍一种采用FPGA与IP来实现DDR RAM控制和验证的方法。

2017-11-24 16:00:22 4673

4673

DRAM (动态随机访问存储器)对设计人员特别具有吸引力,因为它提供了广泛的性能,用于各种计算机和嵌入式系统的存储系统设计中。本文概括阐述了DRAM 的概念,及介绍了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2018-06-07 22:10:00 95076

95076 本文透过对于静态随机存取内存(SRAM)单元缩减布局面积的研究,提出一种新的 存取技术 ,可望提升动态随机存取内存( DRAM )单元的访问速度。 超频与内存的关联性 提升供应电压以及降低环境温度有助于增加微处理器、芯片组、主存储器的频率频率。

2018-03-28 12:03:00 5022

5022

DDR 同步动态随机存取存储器 (Synchronous Dynamic Random Access Memory, SDRAM)控制器使用双倍数据速率(Dual Data Rate,DDR)版本

2018-05-30 09:29:00 8

8 本文首先介绍的是PID控制器的工作原理,其次介绍的是pid控制器的输入输出,最后介绍了PID控制器的参数整定以及PID控制器的控制实现,具体的跟随小编一起来了解一下。

2018-06-01 09:09:01 31261

31261 Random Access Memory的缩写,即同步动态随机存取存储器。而DDR SDRAM是Double Data Rate SDRAM的缩写,是双倍速率同步动态随机存储器的意思。

2019-02-04 11:40:00 9513

9513 本应用说明描述了一个参考系统,该系统演示了Microblaze™处理器系统中多通道(MCH)片上外围总线(OPB)双数据速率(DDR)同步DRAM(SDRAM)控制器的使用。MCH OPB DDR

2019-09-12 14:14:00 0

0 、PSRAM、MRAM等存储芯片供应商英尚微电子解析这款比脑力更强大的DDR SDRAM控制器。 任何DRAM控制器背后的智商都是与命令时序和执

2020-07-24 14:25:27 1196

1196 DRAM作为PC必备器件之一,大家自然对DRAM较为熟悉。但是,大家知道DRAM存储具有哪些分类吗?大家了解DRAM控制器是如何设计出来的吗?如果你对DRAM以及本文即将要阐述的内容具有兴趣,不妨继续往下阅读哦。

2020-10-31 11:51:19 4799

4799

Zynq UltraScale+ MPSoC VCU DDR 控制器是一款专用 DDR 控制器,只支持在 Zynq UltraScale+ MPSoC EV 部件上与 Zynq

2021-02-23 06:00:10 15

15 100V 输入 DC/DC 控制器产生正或负的稳压输出

2021-03-19 08:09:16 4

4 隔离式 8 端口 PoE PSE 控制器无需光耦合器以实现最低的解决方案成本

2021-03-20 14:54:07 5

5 四端口和单端口 LTPoE++ PSE 控制器提供高达 90W

2021-03-20 22:50:58 9

9 本应用指南描述了在 Virtex™-4 XC4VLX25 FF668 -10C 器件中实现的 DDR SDRAM 控制器。该实现运用了直接时钟控制技术来实现数据采集,并采用自动校准电路来调整数据线上的延迟。

2021-03-26 14:42:41 4

4 本文首先分析了DDR SDRAM的基本特征,并提出了相应的解决方案详细介绍了基于J EDEC DDR SDRAM规范的DDR SDRAM控制器设计方案。该控制器采用Verilog HDL硬件描述语言实现,并集成到高性能SoC中。

2021-03-28 10:57:24 23

23 AN-284:用模拟输入/输出端口实现无限采样保持电路

2021-04-22 16:19:39 12

12 LTC3718:适用于DDR/QDR存储器终端的低输入电压DC/DC控制器产品手册

2021-05-22 16:14:04 6

6 基于FPGA的DDR3SDRAM控制器设计及实现简介(arm嵌入式开发平台PB)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现简介资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的DDR3SDRAM控制器设计及实现(嵌入式开发式入门)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 13:07:09 37

37 的性能更高,并且不额外占用其他的可编程逻辑资源 (PL)。使用它的时候,在硬件设计方面和设计流程上,和之前的软核控制器(DDR4 IP)也有着很大的不同。今天我们来介绍一下I/O planning方面的设计考虑和实现流程。

2022-07-06 10:42:17 5678

5678 USB音频输入/输出控制器DP108 简述和特征

2022-10-26 18:01:52 2288

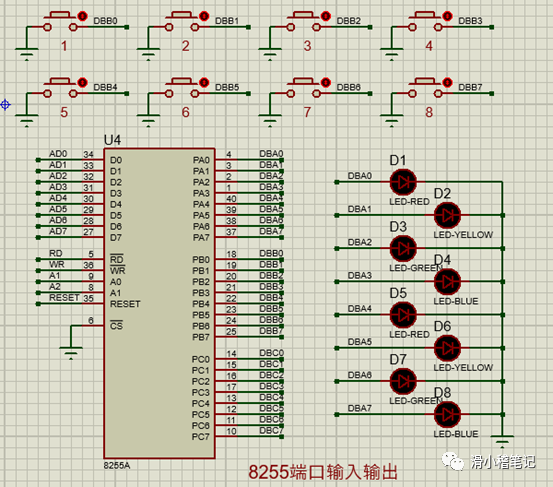

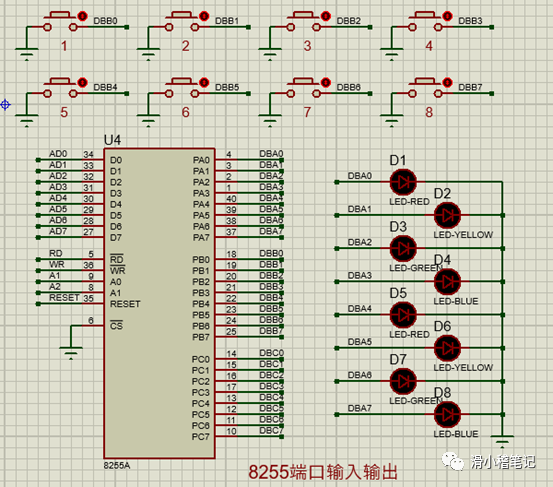

2288 8086的输入输出控制是通过8255芯片控制的,用LED代表输出的数据,按键代表输入的数据,八个LED接在8255的PA端口上,八个按键接在PB端口上,通过8086控制8255A进行数字量的输入与输出。

2023-03-02 09:56:04 3809

3809

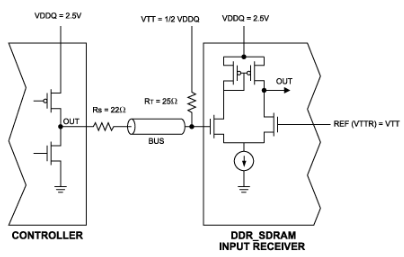

双倍数据速率(DDR)同步动态随机存取存储器(SDRAM)最近越来越受欢迎。DDR 内存需要跟踪主内存电压 VDDQ 的主动端接 VTT。本应用笔记提供开关稳压器方案,利用MAX1957脉宽调制(PWM)降压控制器为VTT端接提供1/2跟踪输出。

2023-03-13 09:35:23 3102

3102

的作用。

编写程序:编写控制程序,包括输入和输出信号的逻辑关系和运算方法。

连接设备:将需要控制的设备连接到PLC控制器的输入和输出端口上。

2023-03-25 09:41:14 1694

1694 电子发烧友网站提供《完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表.pdf》资料免费下载

2024-03-13 10:16:45 1

1 电子发烧友网站提供《完整DDR,DDR2,DDR3 和LPDDR3 存储器电源解决方案同步降压控制器数据表.pdf》资料免费下载

2024-04-09 09:49:32 0

0 DDR和LPDDR都是动态随机存取存储器(DRAM)的类型,它们在计算机和移动设备中用于临时存储数据。

2024-05-12 15:19:00 4796

4796 在工业自动化领域中,PLC(Programmable Logic Controller,可编程逻辑控制器)因其高度的可靠性、灵活性和强大的功能而备受青睐。PLC系统通过其输入端口接收外部信号,经过

2024-06-19 14:11:05 7327

7327 近日,DRAM(动态随机存取存储器)市场传来重磅消息,由于服务器需求持续强劲及产能排挤效应显著,多家大厂决定在第三季度对DDR5内存价格进行新一轮调整。据供应链最新消息,三星电子与SK海力士这两大DRAM巨头已正式发出通知,宣布DDR5内存的单季价格将实现15%以上的显著上涨。

2024-08-21 15:40:01 1224

1224 TPS51116为 DDR/SSTL-2、DDR2/SSTL-18、DDR3/SSTL-15、DDR3L、LPDDR3 和 DDR4 内存系统提供完整的电源。它将同步降压控制器与 3A 灌电流/拉

2025-04-29 16:38:02 1034

1034

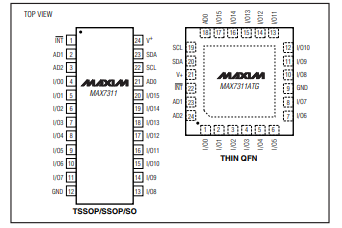

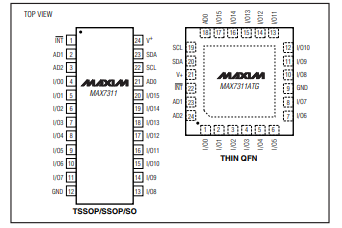

MAX7311 2线接口扩展器为兼容于SMBus™和I²C的应用提供16位并行输入/输出(I/O)端口扩展。MAX7311包含输入端口寄存器、输出端口寄存器、极性反转寄存器、配置寄存器、总线延时

2025-05-26 11:33:37 678

678

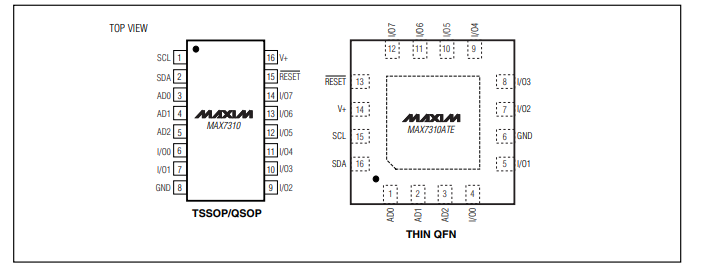

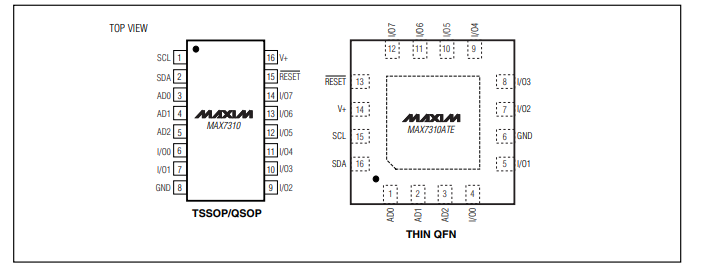

MAX7310为兼容于SMBus™和I²C的应用提供8位并行输入/输出端口扩展。MAX7310包含输入端口寄存器、输出端口寄存器、极性反转寄存器、配置寄存器、总线延时寄存器和一个SMBus/I²C

2025-05-26 15:41:31 827

827

在当今高速发展的3C领域(计算机外设、通信及消费电子),对存储器的性能与功耗提出了更高要求。DRAM动态随机存取存储器作为核心存储部件,其性能表现直接影响设备整体效能。Etron凭借其活缓冲DRAM

2025-12-01 13:42:00 254

254 FPC401四端口控制器:高速网络时代的端口控制利器 在如今高速发展的网络通信领域,端口控制的高效性和稳定性显得尤为重要。德州仪器(TI)推出的FPC401四端口控制器,为SFP+、QSFP+

2025-12-19 09:45:02 143

143

电子发烧友App

电子发烧友App

评论