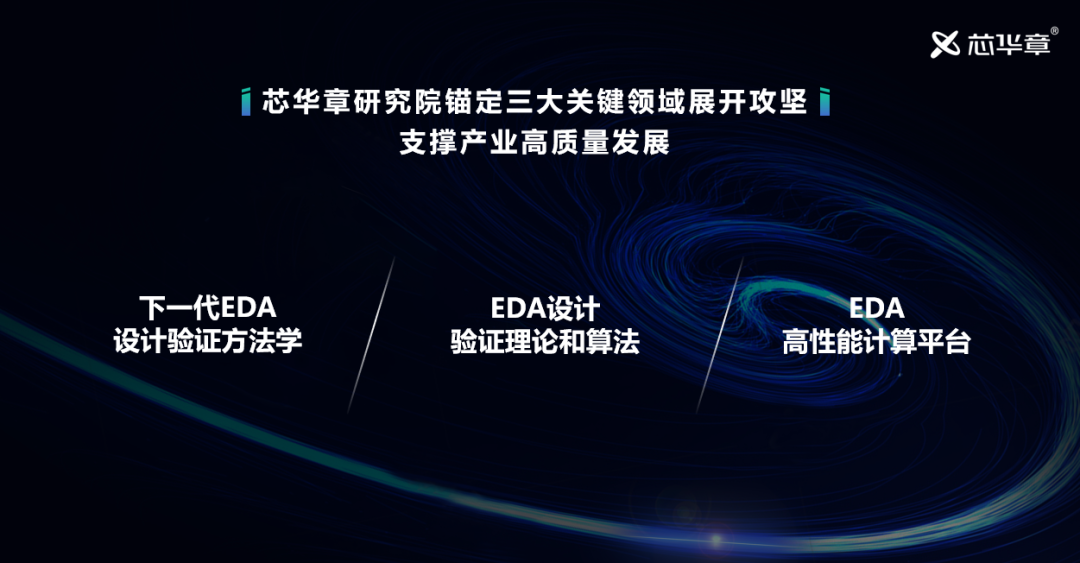

电子发烧友网报道(文/黄晶晶)国产EDA厂商芯华章主要发力数字芯片验证领域,七大产品系列包括:硬件仿真系统、FPGA原型验证系统、智能场景验证、形式验证、逻辑仿真、系统调试以及验证云。在最近,芯华章

2022-05-12 17:58:56 2472

2472

Combinational equivalence是使用EDA工具进行等价性比对中最成熟的FEV技术,一般情况下是将RTL和原理图网表进行等价性比对。

2022-07-19 09:48:35 1301

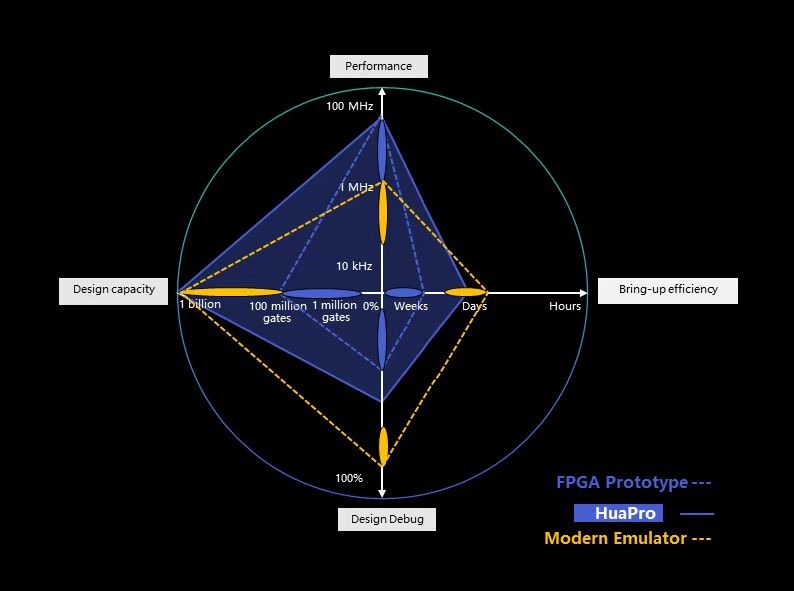

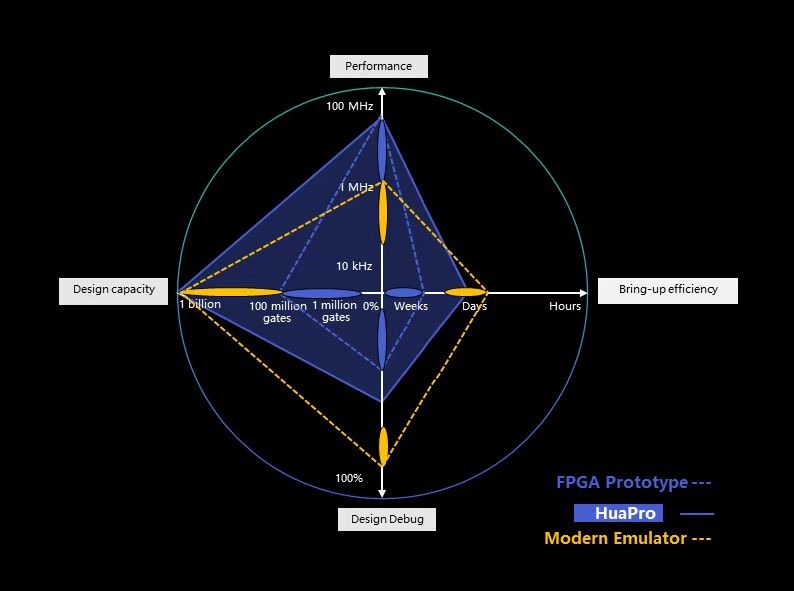

1301 12月2日,芯华章生态及产品发布会在上海成功举办。作为国内领先的系统级验证EDA解决方案提供商,芯华章正式发布高性能FPGA双模验证系统桦捷HuaPro P2E,以独特的双模式满足系统调试和软件开发

2022-12-02 17:01:44 1117

1117

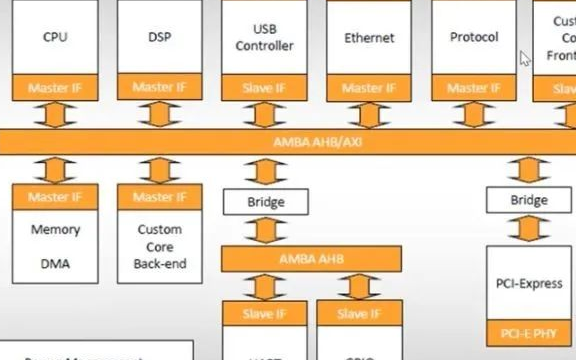

(Dubhe-90)的高性能RISC-V众核子系统IP平台。

StarLink-700是赛昉科技自研的支持缓存一致性的Interconnect Fabric IP,是国内首款Mesh架构互联总线IP

2023-11-29 13:37:35

3月18日消息,继推出智能语音专用处理器R328之后,近日全志科技正式发布主打AI语音专用的重磅产品R329,这是全志科技首款搭载Arm中国全新AI处理单元(AIPU)的高算力、低功耗AI语音专用芯片。

2020-11-23 14:18:03

物理库为后续后端半定制设计提供物理实现基础。 后端半定制设计是指使用布局布线工具并基于后端全定制阶段完成的标准单元库及IP库并根据前端设计完成整个芯片的版图设计,这个过程由称为数字后端

2020-12-29 11:53:01

数字后端工程师(CAD)工作经验, 微电子, 专业QQ:2361362181 邮箱:carry.wang@yaxunhr.com 工作地点:珠海。职位描述:岗位职责:从事各项目的自动布局布线和完善

2013-04-08 17:23:48

数字IC是什么意思?数字IC前端设计流程有哪些?数字IC后端设计流程有哪些?

2021-10-20 06:24:49

数字IC设计之“数字SOC全流程漫谈从0到1”讲师背景:阎如斌老师毕业于慕尼黑工业大学的硕士研究生,具有非常丰富的IC研发经验。在集成电路的从业10多年之久,同时也是叩持电子和IC修真院的创始人,并

2020-12-07 17:39:10

本科及以上学历,信息电子相关专业,英语四级以上; 2.掌握HDL语言及EDA工具,有编解码芯片设计经验者优先;3.熟悉数字图像处理、嵌入式系统软硬件开发或CPU处理器者优先。芯片验证工程师岗位职责

2017-08-15 17:30:37

Checking):电气规则检查,检查短路和开路等电气规则违例;等等。工具为Synopsys的Hercules实际的后端流程还包括电路功耗分析,以及随着制造工艺不断进步产生的DFM(可制造性设计)问题。物理版图验证

2020-02-12 16:09:48

数字芯片设计流程:功能验证之前与工艺库没多大联系,验证芯片设计的功能是否正确,针对抽象的代码进行功能验证理想值。一致性验证确保生成的网表和代码设计功能一致;DFT之后是数字后端。静态时序分析,从逻辑

2021-11-10 06:14:28

要求:1.本科及以上学历,信息电子相关专业,英语四级以上; 2.掌握HDL语言及EDA工具,有编解码芯片设计经验者优先;3.熟悉数字图像处理、嵌入式系统软硬件开发或CPU处理器者优先。 芯片验证工程师

2017-08-15 17:23:32

Rule Checking):电气规则检查,检查短路和开路等电气规则违例;等等。工具为Synopsys的Hercules实际的后端流程还包括电路功耗分析,以及随着制造工艺不断进步产生的DFM(可制造性

2020-02-25 14:44:09

Checking):电气规则检查,检查短路和开路等电气规则违例;等等。工具为Synopsys的Hercules实际的后端流程还包括电路功耗分析,以及随着制造工艺不断进步产生的DFM(可制造性设计)问题。物理版图

2020-03-20 10:14:53

数字后端,顾名思义,它处于数字IC设计流程的后端,属于数字IC设计类岗位的一种。在IC设计中,数字后端所占的人数比重一直是最多的,而且随着芯片规模不断加大,后端工程师需要的人数将会越来越多。一般来说

2021-01-13 06:31:48

时,需要将问题反馈到社区。由于开源社区无人负责,需要被动等待对方响应并解决问题,这就又有一个不可预估的时间成本。自研ETL:BI软件里的自研ETL能做到全面可视化,每一个节点的任务定义、来源表和目的表

2020-08-27 09:44:07

,代码的编写,要会使用硬件描述语言,也就是上面有提到的verilog/VHDL等,当然,也会要使用一些仿真软件。后端设计需要的则会更加多一些了,包括综合,到P&R,以及最后的STA,这些工具里

2011-12-19 16:01:13

GDSⅡ的设计流程: 这个可以理解成全定制的设计流程,一般用于设计模拟电路和数模混合电路。 整个流程如下(左侧为流程,右侧为用到的相应EDA工具): 一个完整的全定制设计流程应该是:电路图输入、电路仿真、版图设计、版图验证(DRC和LVS)、寄生参数提取、后仿真、流片

2012-01-11 13:49:27

1.1 从RTL到GDSⅡ的设计流程: 这个可以理解成半定制的设计流程,一般用来设计数字电路。整个流程如下(左侧为流程,右侧为用到的相应EDA工具): 一个完整的半定制设计流程应该是:RTL代码

2018-08-16 09:14:32

,检查短路和开路等电气 规则违例;等等。工具为Synopsys的Hercules实际的后端流程还包括电路功耗分析,以及随着制造工艺不断进步产生的DFM(可制造性设计)问题,在此不说了。物理版图验证完成

2018-08-13 17:05:29

来源EETOPIC的设计过程可分为两个部分,分别为:前端设计(也称逻辑设计)和后端设计(也称物理设计),这两个部分并没有统一严格的界限,凡涉及到与工艺有关的设计可称为后端设计。前端设计的主要流程:1

2016-06-29 11:30:46

,融入OS”为核心,建立起了丰富的Linux开发生态,目前开发板已经成功适配了全志自研Tina Linux、Ubuntu、RT-Thread Smart、Debian、Fedora......等数款

2022-08-23 09:24:13

)【D1哪吒·Tina SDK,全志原厂发布】版本:V1.0时间:2021年5月1日更新说明:基于Linux 5.4内核,全志自研源码下载方法见:https://bbs.elecfans.com

2021-05-20 14:09:42

资料,实现资源、经验共享。 岗位要求:1、具有3年以上数字类芯片或FPGA逻辑 SOC子系统设计经验,熟悉芯片开发流程;2、熟练掌握芯片SOC内嵌子系统架构分析、系统设计、验证经验,具有板级SOC子系统

2020-02-29 11:06:28

1) 数字前端(设计、验证) 北京2)数字后端设计工程师 北京 3)通信算法工程师 北京 4)ADC/DAC模拟电路设计工程师北京5)图像/视频算法工程师 北京6)高级系统工程师 北京7)高速

2017-04-05 10:03:08

设计、验证能力都具备。 2)数字后端设计工程师 工作职责: 1.负责芯片的后端物理实现,从NETLIST到GDSII。 2.负责芯片物理设计的时序收敛,DRC/LVS,Power plan等。 职位

2017-03-03 14:53:07

中国移动旗下专业芯片子公司,中移芯昇(芯昇科技有限公司)携中国移动首款基于 RISC-V 内核的 MCU 芯片 ——CM32M4xxR 隆重亮相。围绕物联网芯片国产化,中移芯昇聚焦 RISC-V

2022-03-22 18:09:15

数字逻辑的可验证性是指,数字逻辑(RTL代码)中所具备的有助于验证工程师开展验证工作和加快验证收敛的设计属性。 数字逻辑设计工程师写代码时,通常要考虑逻辑电路的延迟,面积,功耗等特性。如果这些

2023-04-04 17:24:02

不断壮大,希望PineTab-V能为推动RISC-V生态贡献更多力量。”JH7110是全球首款量产的高性能RISC-V多媒体处理器,此次成功赋能入门级平板电脑,将进一步验证RISC-V芯片应用于生产力设备的可行性。

2023-04-14 13:56:10

华为举行 2022 华为全屋智能及全场景新品春季发布会,余承东带来了华为智能门锁 Pro 新品。这是全球首款鸿蒙 HarmonyOS 智能门锁。这款新产品有哪些新特性呢?

2022-03-18 11:42:50

半定制/全定制混合设计的特点,提出并实现了一套半定制/全定制混合设计流程中功能和时序验证的方法。论文从模拟验证、等价性验证和全定制设计的功能验证三个方面对FF-DX的分支控制部件进行功能验证。对于模拟

2011-12-07 17:40:14

的,在后端不同的约束下具有不同的实现。FEC等价性检查的第一步是建立映射关系,这个建立的过程可由工具实现,也可以认为指定。映射的点可以是输入、输出、寄存器以及其他人为指定的比较点等等。映射完成后,FEV工具

2022-07-22 14:56:37

首个基于Chiplet的“启明930”AI芯片。北极雄芯三年来专注于Chiplet领域探索,成功验证了用Chiplet异构集成在全国产封装供应链下实现低成本高性能计算的可行性,并提供从算法、编译到部署

2023-02-21 13:58:08

国芯自搜通用刷版修改工具软件 [/hide]

2010-09-02 19:07:01

导读:国美GOMEPOD智能音箱搭载了科大讯飞先进的语音识别AI技术,可以通过语音交互实现全屋多设备间的连接,是国内首款支持免提通话的智能音箱。

11月29日消息,以“智美家.生活

2018-11-30 09:26:17

必须包裹在工具流程中。工具必须做得够聪明来管理重要细节(如接口、组态和初始化需求)以便连结不同的组件并放在同一作业中。理想上此新系统功能性的复杂设计内容汇集基本上和传统工具流程完全一样的工具流程

2011-10-16 22:55:10

基于OpenHarmony、数字管家开发宿舍全屋智能,实现碰一碰开门、碰一碰开灯、碰一碰开风扇以及烟感检测。因为各项目开发流程大体相似,本文主要以碰一碰开门为例介绍如何在现有OpenHarmony

2022-03-24 09:31:11

华为开发者大会 2021(Together)上,Harmony OS 3 开发者预览版正式发布,华为鸿蒙又是一个历史性的进步啊,而且,华为还表示,将发布自研鸿蒙编程语言!!!编程语言是什么?这其实是

2021-10-25 16:53:43

工控上位机软件开发全流程自研-上位机软件开发-工业级控制系统一、上位机软件开发底层设计二、上下位机通信的安全性三、上位机软件接收与存储研发四、数据清洗与图形展示研发五、上位机软件发送指令与回调六

2021-07-19 08:42:25

在前不久的电动·未来品牌盛典上,比亚迪发布了旗下全新混合动力车型:比亚迪宋DM。而近日宋DM也悄然的抵达了北京的比亚迪4S店中,下面就一起了解一下这款车究竟如何吧。 所谓全擎全动力就是指一款车型

2017-06-09 18:52:33

工具也有相同和不同的。1、数字Asic设计流程前端到后端使用工具通用型数字Asic(从上到下)在验证算法时一般使用C语言或者verilog来对系统算法进行建模,使用行为级描述来对算法功能的正确与否进行

2013-01-07 17:10:35

关于时序逻辑等效性的RTL设计和验证流程介绍。

2021-04-28 06:13:14

本科及以上学历,信息电子相关专业,英语四级以上; 2.掌握HDL语言及EDA工具,有编解码芯片设计经验者优先;3.熟悉数字图像处理、嵌入式系统软硬件开发或CPU处理器者优先。芯片验证工程师岗位职责

2017-08-15 17:31:54

本科及以上学历,信息电子相关专业,英语四级以上; 2.掌握HDL语言及EDA工具,有编解码芯片设计经验者优先;3.熟悉数字图像处理、嵌入式系统软硬件开发或CPU处理器者优先。芯片验证工程师岗位职责

2017-08-15 17:28:15

芯片设计流程IC的设计过程可分为两个部分,分别为:前端设计(也称逻辑设计)和后端设计(也称物理设计),这两个部分并没有统一严格的界限,凡涉及到与工艺有关的设计可称为后端设计。前端设计的主要流程:1

2020-03-20 10:27:35

芯片设计流程及工具IC的设计过程可分为两个部分,分别为:前端设计(也称逻辑设计)和后端设计(也称物理设计),这两个部分并没有统一严格的界限,凡涉及到与工艺有关的设计可称为后端设计。前端设计的主要流程

2020-02-12 16:07:15

Rule Checking):电气规则检查,检查短路和开路等电气 规则违例;等等。工具为Synopsys的Hercules实际的后端流程还包括电路功耗分析,以及随着制造工艺不断进步产生的DFM(可制造性

2019-08-16 11:08:08

完成,而且还可以提供给客户有壁垒性的独家服务。苹果通过自研的芯片和自己开发的操作系统,在手机、平板和电脑上提供相同的体验,让同行难以望其项背,在终端市场销售和口碑赢得了高人气。现在推进射频芯片、无线

2022-01-02 08:00:00

群主好,我想请教数字电路的系统级设计验证工具及流程?即系统工程师常用的硬件描述语言,系统验证工具以及设计验证的基本流程,多谢!

2012-09-05 15:11:23

是Galaxy Design System, 验证部分是Discovery platform. 从前到后的全流程设计,VCS, DC, DFTC, Formality, Prtimetime

2012-12-28 17:00:22

要求:1.本科及以上学历,信息电子相关专业,英语四级以上; 2.掌握HDL语言及EDA工具,有编解码芯片设计经验者优先;3.熟悉数字图像处理、嵌入式系统软硬件开发或CPU处理器者优先。 芯片验证工程师

2017-08-15 17:26:25

转自https://m.ithome.com/html/714391.htm

2023 RISC-V 中国峰会8月23日在北京召开,平头哥在会上发布了首个自研 RISC-V AI 平台。

据介绍,该

2023-08-26 14:14:40

Symtavision工具为Luxoft公司提供的一款分布式嵌入式系统时间特性建模、分析和验证工具,主要应用于汽车领域。经纬恒润联合Symtavision工具厂商能够为客户提供完整的系统级时间特性

2022-04-13 14:10:59

为了在早期阶段发现电路设计错误,需要对包含未知部分的实现电路和规范电路进行等价性验证。本文提出了一种“分而治之”的方法,把电路划分成若干子电路,使用四值逻辑模

2010-07-30 17:39:27 17

17 数字前端设计流程,使用PT进行STA lSYNOPSYS Prime Time l只是一个时序分析工具,本身不对电路做任何修改。 l在ASIC流程中对于电路进行任何修改过后都应该使用STA工具检查其时序,以保证电

2011-10-28 10:28:08 41

41 数字后端流程 1. 数据准备。对于 CDN 的 Silicon Ensemble而言后端设计所需的数据主要有是Foundry厂提供的标准单元、宏单元和I/O Pad的库文件,它包括物理库、时序库及网表库,分别以.lef、

2011-10-28 10:31:06 39

39 本文首先介绍了ic设计的方法,其次介绍了IC设计前段设计的主要流程及工具,最后介绍了IC设计后端设计的主要流程及工具。

2018-04-19 18:04:45 11661

11661 据芯华章科技创始人、董事长兼CEO王礼宾透露,芯华章即将推出市场上首款支持国产计算机架构的国产验证EDA工具。该工具会采用全新的系统架构,不仅兼容现有国际和国内的计算机架构,更有利于支持新一代多核

2020-11-05 16:44:06 641

641 数字IC设计流程是每个IC从业者的第一课,无论你是做前端,后端,还是验证,都需要对芯片的整个设计流程有个基本的了解。 本文章主要介绍以下三点内容: 一. 数字IC设计的流程及每个流程需要

2020-12-09 10:12:11 6448

6448

;主要包括:基本的RTL编程和仿真,前端设计还可以包括IC系统设计、验证(verification)、综合、STA、逻辑等值验证 (equivalence check)。其中IC系统设计最难掌握,它需...

2021-11-06 16:51:05 26

26 芯华章成功发布4款验证产品并收获业界高度的认可与关注!这离不开行业、生态伙伴一直以来的信任与支持!

2021-12-22 15:43:31 2491

2491 EDA(集成电路设计工具)智能软件和系统领先企业芯华章正式发布四款拥有自主知识产权的数字验证EDA产品,以及统一底层框架的智V验证平台,在实现多工具协同、降低EDA使用门槛的同时,提高芯片整体验证效率,是中国自主研发集成电路产业生态的重要里程碑。

2021-12-22 15:48:33 2048

2048 12月,中国IC设计产业一年一度的盛会ICCAD在无锡成功举办。本次,芯华章科技董事长兼CEO王礼宾在主题演讲中,为产业同仁带来解决验证三大痛点的“高效、协同、易用”的全新方案;而在展示区域,芯华章新发布的四款数字验证EDA产品首亮相,全面的展示与生动的现场演示,吸引了产业同仁的目光焦点。

2021-12-31 10:52:27 4068

4068 芯华章科技正式宣布,CMOS毫米波雷达芯片开发的领导者加特兰微电子与芯华章达成合作,采用芯华章的高性能FPGA原型验证系统产品-桦捷(HuaPro-P1),验证新一代复杂芯片的设计。

2022-02-10 09:32:02 1609

1609 芯来科技将正式采用芯华章自主研发的新一代智能验证系统穹景 (GalaxPSS)及数字仿真器穹鼎 (GalaxSim)等系列EDA验证产品,加速新一代复杂RISC-V处理器IP的设计研发。

2022-03-03 10:32:25 1968

1968 EDA(集成电路设计工具)智能软件和系统领先企业芯华章正式发布基于创新架构的数字验证调试系统——昭晓Fusion DebugTM 。该系统基于芯华章自主开发的调试数据库和开放接口,可兼容产业现有

2022-05-11 09:55:33 832

832 2022年5月11日,EDA(集成电路设计工具)智能软件和系统领先企业芯华章正式发布基于创新架构的数字验证调试系统——昭晓Fusion DebugTM 。

2022-05-11 10:09:19 1287

1287 2022年5月11日,EDA(集成电路设计工具)智能软件和系统领先企业芯华章正式发布基于创新架构的数字验证调试系统——昭晓Fusion DebugTM 。该系统基于芯华章自主开发的调试数据库和开放

2022-05-11 10:44:24 1749

1749

近期,芯华章正式发布了基于创新架构的数字验证调试系统——昭晓Fusion Debug™。在研讨会暨新产品发布会上,中兴微电子有线系统部部长贺志强、平头哥上海半导体技术IP验证及软硬协同验证负责人

2022-05-30 16:31:54 1722

1722 芯片验证就是采用相应的验证语言,验证工具,验证方法,在芯片生产之前验证芯片设计是否符合芯片定义的需求规格,是否已经完全释放了风险,发现并更正了所有的缺陷,站在全流程的角度,它是一种防范于未然的措施。

2022-07-25 11:48:49 5263

5263 形式验证工具(Formal Verification Tool)是通过数学逻辑的算法来判断硬件设计的功能是否正确,通常有等价性检查(Equivalence Checking)和属性检查(Property Checking)两种方法。

2022-08-25 14:35:21 1034

1034 近日,芯华章科技宣布对高性能仿真软件领先企业瞬曜电子进行核心技术整合,将超大规模软件仿真技术融入芯华章智V验证平台,以增强其丰富的系统级验证产品组合,巩固芯华章敏捷验证方案。同时,傅勇正式加盟芯华章

2022-09-26 10:03:15 274

274 的使用过程演示,吸引了来自先进通信、智能汽车、信息科技、人工智能、高端GPU等数字领域的数十家企业到场参与,并对产品验证效果给予高度认可。 现场直击 深度演示系统级验证创新方案 这次,芯华章更是将产品带到现场,通过实机和产品

2022-10-20 18:21:55 331

331

量产、落地和强化专家级技术支持队伍建设,进一步夯实芯华章数字验证全流程服务能力,为数字产业发展提供安全、可靠的高质量工具链。 面对新兴技术环境下,系统应用创新在验证规模、效率和完备性等方面提出的巨大挑战,芯华章以终为始,打造了统一底层架构的智

2022-11-28 09:40:36 344

344 融资将用于加快实现产品量产、落地和强化专家级技术支持队伍建设,进一步夯实芯华章数字验证全流程服务能力,为数字产业发展提供安全、可靠的高质量工具链。 面对新兴技术环境下,系统应用创新在验证规模、效率和完备性等方面提出的巨大挑战,芯华章以终为始,打造了统一底层

2022-11-28 15:02:47 399

399 “借助芯华章的FPGA原型验证系统HuaPro,我们进一步提升了光芯片的设计和验证效率,其优秀的软硬协同验证能力给我们留下了深刻的印象。作为集成硅光子技术的坚定支持者,我们相信与芯华章的密切合作,不仅将促进光电混合Chiplet芯片的设计、仿真、验证等EDA流程优化

2022-11-30 09:32:57 689

689 的联合研究,并在光芯片设计流程中,正式导入芯华章智V验证平台EDA工具,形成垂直解决方案,以提高光芯片设计和验证效率,满足数据通信、AI及光学计算等应用领域日益增长的数据处理与运算需求。 AI、5G、工业物联网以及自动驾驶汽车等新兴

2022-11-30 10:17:32 317

317

不断发展的SoC和Chiplet芯片创新,对高性能硬件验证系统有更多虚拟或物理验证、深度调试、提前软件开发的需求,这些需求往往需要切换多种EDA工具。在大规模芯片的验证流程中,硬件仿真和原型验证都是

2022-12-09 10:49:16 793

793 12月26日-27日,中国IC设计产业一年一度的盛会ICCAD在厦门成功举办。系统级验证EDA解决方案提供商芯华章此次携多项自研创新产品亮相,现场结合应用场景带来生动使用演示,其中最新发布的高性能

2022-12-28 10:36:02 783

783 带UPF的低功耗设计流程中包括了前端VCS-NLP功能仿真,后端VC LP静态验证,以及在DC综合和ICC2布局布线中低功耗单元的插入,例如level shifter,isolation cell

2023-02-26 09:48:42 1306

1306 技术支持队伍建设,进一步夯实芯华章数字验证全流程服务能力,为数字产业发展提供安全、可靠的高质量工具链。 基于芯华章先进的数字验证EDA工具,信科资本将积极协助中国信科集团旗下二进制半导体、宸芯科技等企业引进全方位的

2023-03-14 10:18:18 520

520

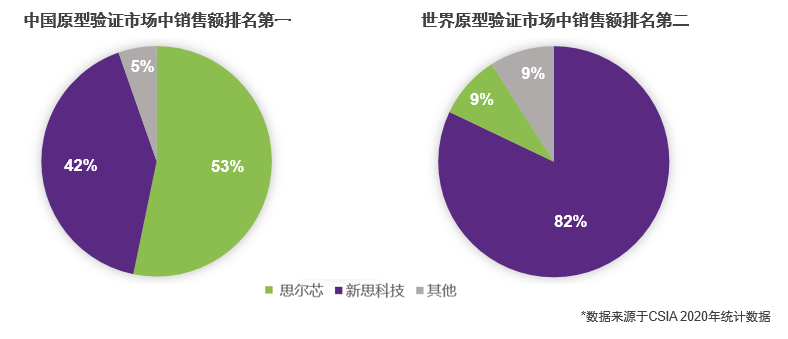

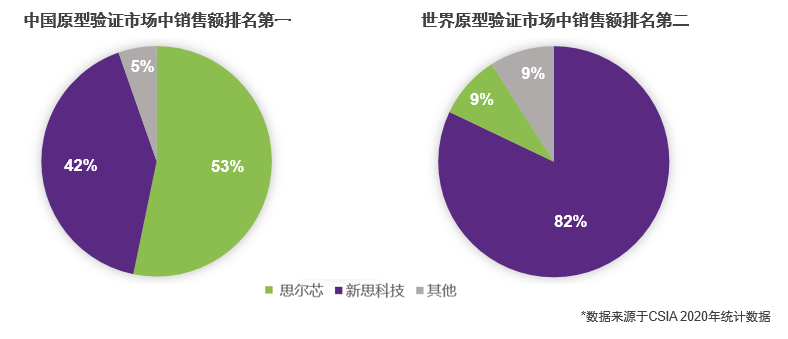

设计的全自动编译。目前已在多个芯片设计企业推广使用。帮助汽车电子、CPU、AI、5G、云计算等SoC设计所需的复杂验证。随着 OmniArk 芯神鼎的发布,思尔芯将逐渐形成数字前端验证全流程的解决方案。 原型验证市场领先 集成电路EDA工具是芯片设计与

2023-03-23 18:03:00 1042

1042

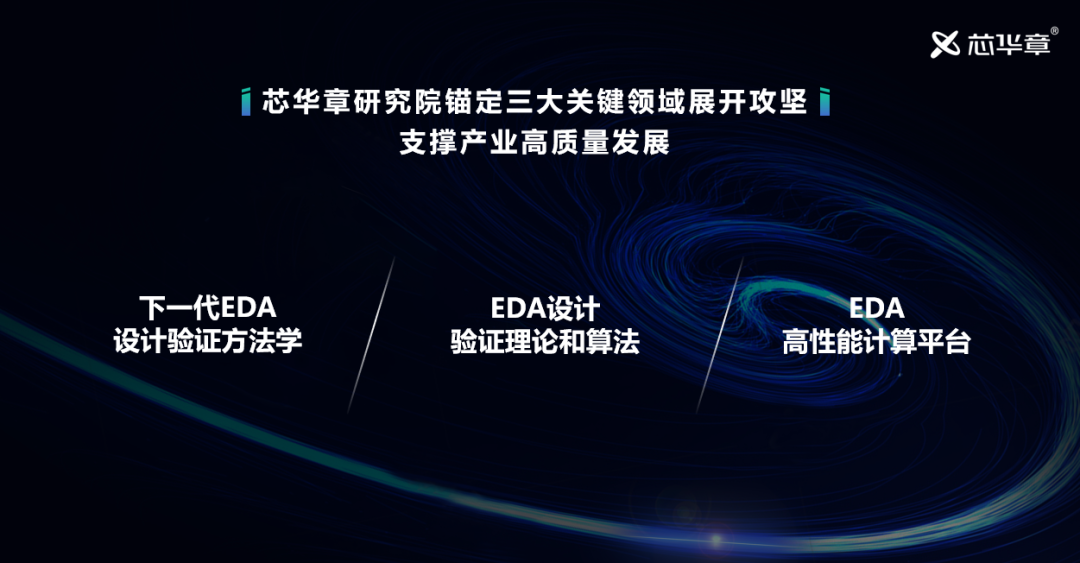

商界20位潜力女性代表,芯华章副总裁兼董事会秘书王喆,受邀参与“她智慧·科技创新驱动未来”主题论坛,分享数字化浪潮下国产EDA发展脉络,展示硬核科技女性风采。 谈及国产EDA的快速发展,王喆表示: “在过去二十多年数字化迅猛发展的土壤中间,伴

2023-05-31 10:07:35 339

339 验证其实是一个“证伪”的过程,从流程到工具,验证工程师的终极目的都只有一个。

2023-05-31 10:34:49 1069

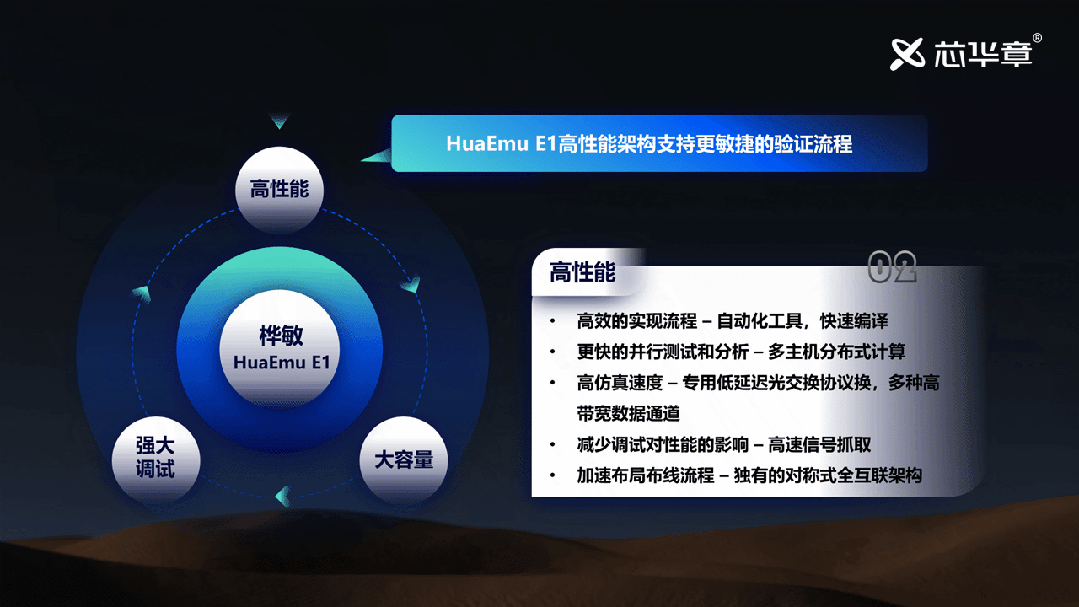

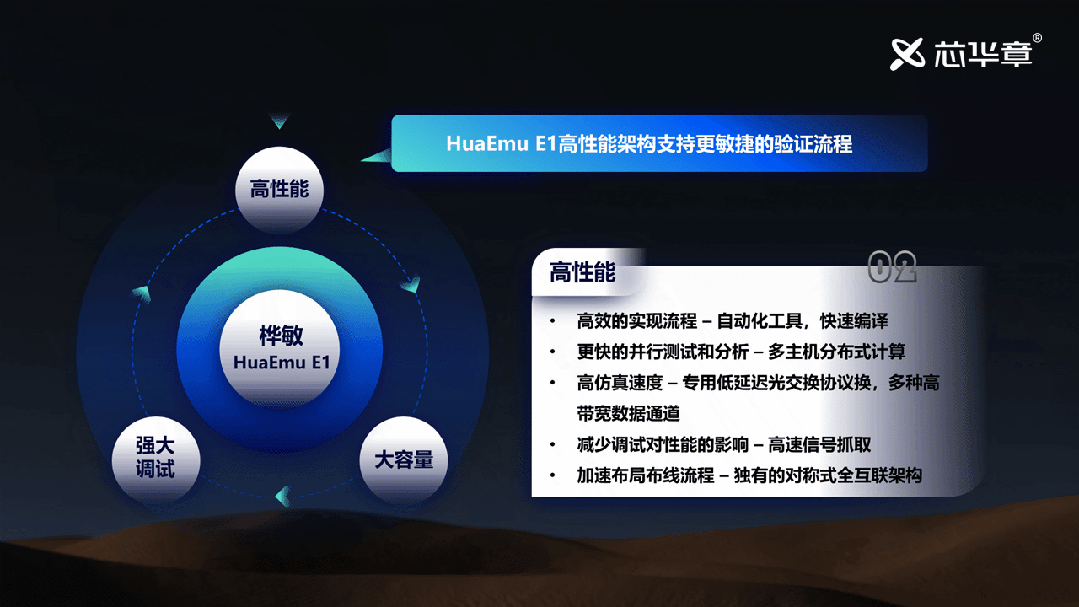

1069 2023年6月15日,国内领先的系统级验证EDA解决方案提供商芯华章,正式发布国内首台设计上支持超百亿门大容量的硬件仿真系统桦敏HuaEmu E1,可满足150亿门以上芯片应用系统的验证容量。产品

2023-06-15 14:44:28 390

390 桦敏HuaEmu E1 2023年6月15日,国内领先的系统级验证EDA解决方案提供商芯华章,正式发布 国内首台设计上支持超百亿门大容量的硬件仿真系统桦敏HuaEmu E1,可满足150亿门以上芯片

2023-06-16 10:48:55 404

404

伴随先进工艺节点不断进步,系统定义芯片的日益普及,数字系统的应用场景也越来越复杂,芯片设计规模迎来指数级增长,进入百亿门级时代。特别是芯片集成度越来越高,商业IP的重复应用越来越广泛,以及系统级芯片

2023-06-20 15:43:16 225

225

硬件仿真器被称之为EDA工具皇冠上的明珠,其地位十分重要。近日,国内EDA厂商芯华章正式发布硬件仿真系统桦敏HuaEmu E1,是国内首台可满足150亿门以上芯片应用系统的验证容量的产品。至此

2023-06-26 17:33:31 1218

1218

经过3年多的发展,芯华章全球500多人汇聚eda行业精英和尖端科技人才,eda数字验证领域已从芯片发布验证系统解决方案156项自主知识产权申请,港内平台化,智能化,云化底层构架的验证系统级产品行业提供完整敏捷的数字验证eda工具

2023-08-04 12:01:02 501

501 首届IDAS设计自动化产业峰会将于9月18日在武汉中国光谷科技会展中心举行。作为国内领先的系统级验证EDA解决方案提供商,芯华章受邀参展,将带来完整的数字验证全流程工具及客制化解决方案,与全球行业

2023-08-29 09:10:02 554

554

英诺达发布了自主研发的静态验证EDA工具EnAltius®昂屹® DFT Checker,该工具可以在设计的早期阶段发现与DFT相关的问题或设计缺陷。

2023-09-13 09:05:18 746

746 会议,活动着重关注系统集成、IC设计及验证及电子设计自动化(EDA)的标准制定,并云集业界专家集中探讨在UVM、形式验证、验证策略、性能分析、联合仿真等领域的技术、工具和标准以及最新思想。 芯华章专注于数字EDA验证领域, 本次受邀参与主题演讲及专场分享, 并携数字验证全流程解决方

2023-09-13 16:15:01 471

471

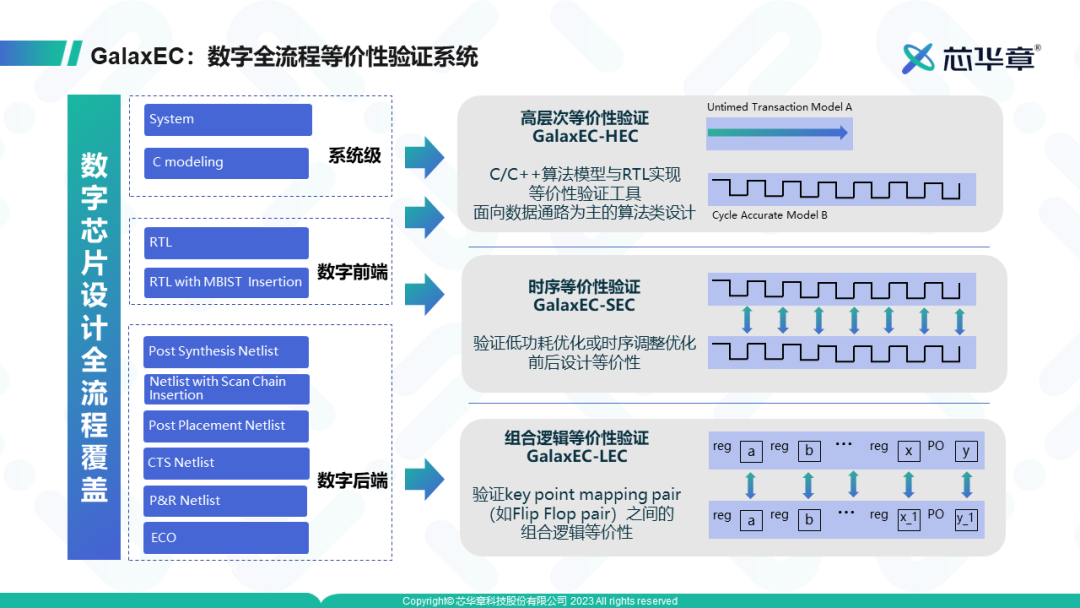

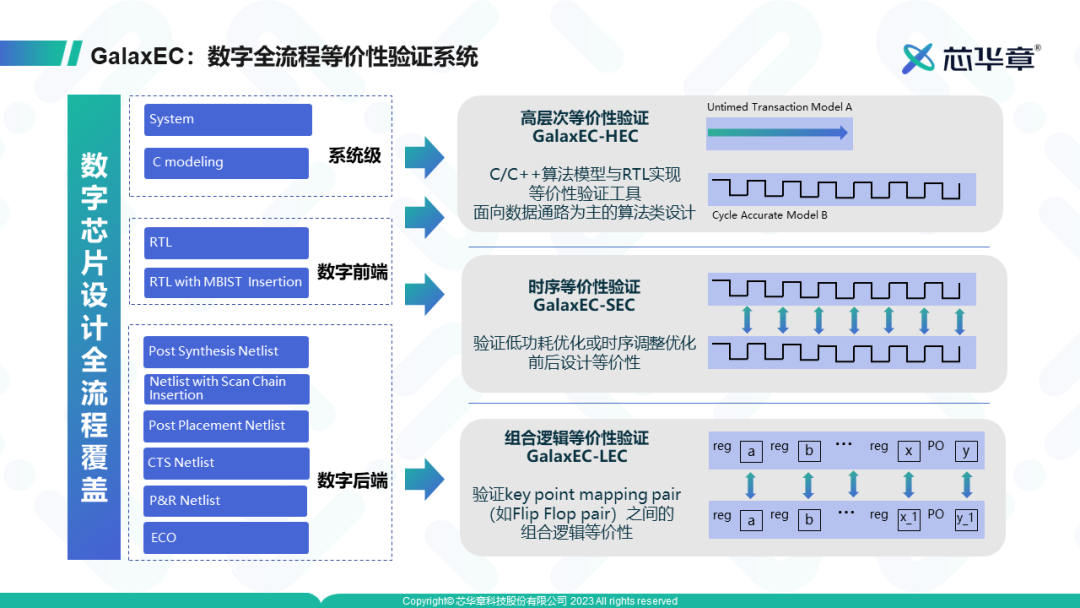

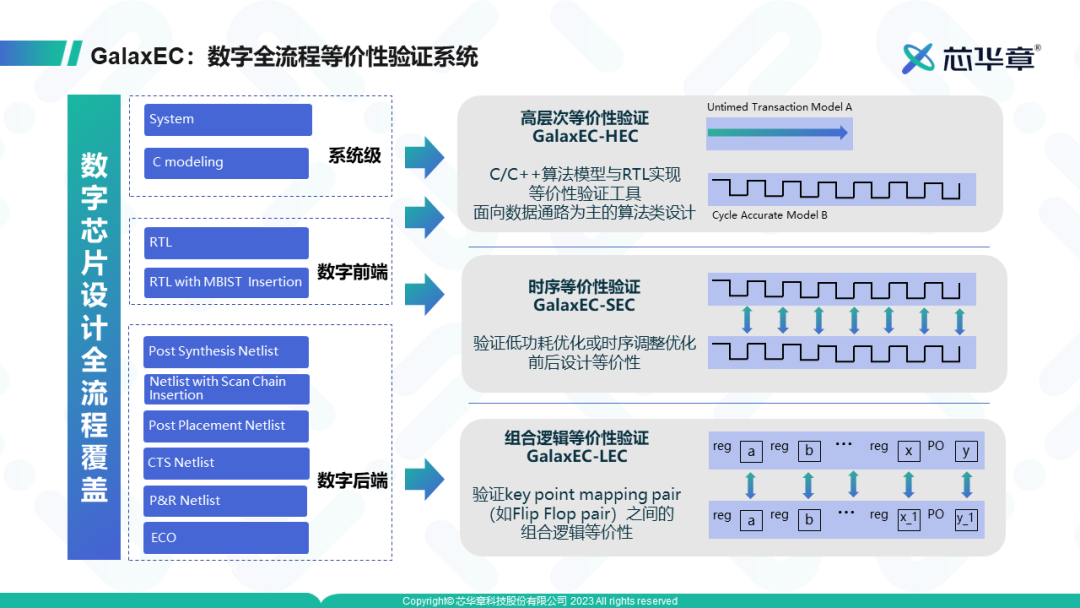

及相关专业人士,业内领先的系统级验证EDA解决方案提供商芯华章,隆重发布 首款自主研发的数字全流程等价性验证系统穹鹏GalaxEC 。 随着GalaxEC的发布, 芯华章自主EDA工具完成了对数字验证

2023-09-19 11:05:04 227

227

近日,芯华章系统级EDA数字仿真工具GalaxSim获德国莱茵TÜV集团(以下简称“TÜV莱茵”)ISO 26262 TCL3功能安全工具认证,能够支持汽车安全完整性标准最高ASIL D级别的芯片

2023-12-06 15:43:51 179

179

近日,芯华章系统级EDA数字仿真工具GalaxSim获德国莱茵TÜV集团(以下简称“TÜV莱茵”)ISO 26262 TCL3功能安全工具认证,能够支持汽车安全完整性标准最高ASIL D级别的芯片

2023-12-07 09:30:02 151

151

为更好地推动EDA工具国产化,加快构建产业生态体系,3月13日,芯华章科技宣布与珠海南方集成电路设计服务中心(珠海ICC)达成战略合作,后者将引进芯华章智V验证平台及数字验证全流程工具,为中心

2024-03-13 10:01:48 123

123

电子发烧友App

电子发烧友App

评论