摘 要: 讨论了用伪随机序列实现程序加密保护及其可编程逻辑器件实现的原理、方法和具体操作,给出了在微机软件和单片机/DSP系统中程序加密的实际运用举例。

可编程逻辑器件(PLD)经历了PAL、GAL、CPLD 和FPGA几个发展阶段。使用PLD具有设计灵活、调试方便、系统可靠性高等众多优点,并有利于硬件设计的保护,防止他人对电路的分析、仿照,使其成为科研实验、样机试制和小批量产品的首选方案。

随着计算机、单片机技术的发展和广泛应用,软件加密成为知识产权保护的重要手段。目前微机软件加密的方法可分为两大类:软加密和硬加密。软加密主要有密码方式、软件自校验方式、钥匙盘方式等多种。随着软加密的发展,解密软件也大量出现。硬加密由于具有加密强度大、可靠性高等特点,已广泛用于微机软件保护。硬加密将硬件和软件相结合来实现软件的加密,软件在运行时需与硬件正确交换数据,否则程序不运行,或不能执行主要功能,典型的产品有:插在计算机总线上的加密卡,接在计算机并口或USB口的软件狗(加密锁)、微狗等。软件狗大多用E2PROM存储密码数据,电路简单,成本低,但用SOFT-ICE等软件进行软件狗的解密和复制并不很困难。在这种情况下,软件狗内部增加了一个单片机称为微狗,通过对数据的处理来提高软件的加密强度;少数专业的硬加密生产商则采用独自的ASIC芯片。加密卡的原理与软件狗和微狗的相似,不同的是通过总线操作,使得设计更灵活、功能更强,只是安装不方便。

随着某一加密产品加密操作方式的公开,其解密也就为期不远。新出现的解密软件能模拟绝大部分软件与加密狗间的数据交换过程,从而达到解密;国产的加密卡和微狗,大多外用E2ROM存储配置数据和用户密码,获取这些数据就可能解密、甚至复制微狗,因此加密方法的独特性、手法的反常规性在加密应用中非常重要。单片机/DSP系统的控制及外围电路都相对简单,对软件的跟踪比较容易分析硬件的设计思想和实现功能,而目前对其软件的保护并不受重视,并且单片机/DSP系统没有现成的加密产品,设计者应结合系统软、硬件的要求灵活决定。我们利用PLD器件本身的加密保护特性,由其产生的伪随机序列实现单片机/DSP系统和计算机应用程序的加密,具有简单方便,解密难度大的特点,同样可用PLD器件实现更复杂的加密方法如 EDS。

1 硬件加密的PLD实现原理

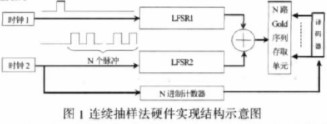

硬件加密必须综合考虑加密方法的可行性、有效性、硬件复杂度等因素,由逻辑电路产生大量密码的一种简单有效的方法是使用线性反馈移位寄存器,其产生的伪随机数据已广泛用于数据通信中的加扰、扩频、跳频和数据加密。图1所示是具有防跟踪、产生2N-1个N 位伪随机数据的加密电路原理框图,密码生成所用触发器和门电路少,并且密码是加电后动态产生的,不同的预置产生的数据不同,因此密码的强度、隐蔽性优于加密狗和微狗(卡)。

N位移位寄存器产生的伪随机码作为读取的密码或输入数据解密的密钥,在移位时钟的作用下,可输出2N-1个N位的有效密码或密钥。对某一具体电路,移位寄存器初值不同时,这2N-1个随机数有2N-1种排序,可预置伪随机数产生器的原理电路如图2所示。要使移位寄存器产生一确定的值,首先置其初值,然后置移位计数器初值并允许时钟电路产生移位时钟;当移位计数器计满时,产生一个数据准备好状态可供软件读取,该状态同时阻断时钟电路,停止移位操作,并且启动防跟踪记数器的时钟产生电路;若在规定的时间内读取密码字或者写入待解密数将清零防跟踪记数器,否则超时使防跟踪记数器满导致触发器翻转,打开三态门,扰乱输出数据,虽然这时读/写数据能清零防跟踪记数器,阻断其时钟,但必须重加电或系统复位才能断开三态门。

N位移位寄存器产生的伪随机码作为读取的密码或输入数据解密的密钥,在移位时钟的作用下,可输出2N-1个N位的有效密码或密钥。对某一具体电路,移位寄存器初值不同时,这2N-1个随机数有2N-1种排序,可预置伪随机数产生器的原理电路如图2所示。要使移位寄存器产生一确定的值,首先置其初值,然后置移位计数器初值并允许时钟电路产生移位时钟;当移位计数器计满时,产生一个数据准备好状态可供软件读取,该状态同时阻断时钟电路,停止移位操作,并且启动防跟踪记数器的时钟产生电路;若在规定的时间内读取密码字或者写入待解密数将清零防跟踪记数器,否则超时使防跟踪记数器满导致触发器翻转,打开三态门,扰乱输出数据,虽然这时读/写数据能清零防跟踪记数器,阻断其时钟,但必须重加电或系统复位才能断开三态门。

对加密电路的正确操作步骤是:在主程序中预置移位计数器和移位寄存器初值,在子程序的一处判断移位是否完成,另一处读密码或写待解密数,在另一子程序判断或取解密数据,以防止跟踪。

为在使用较少触发器情况下保证程序正常运行并能有效地防止解密跟踪,应恰当地选择防跟踪计数器的时钟,若用移位寄存器时钟源,则需要较高的分频才能满足高速的数据产生、适当的延时时间;因此在实际使用中,应根据需要,选择系统可能提供的低频持续脉冲信号作为防跟踪计数器的时钟。在微机系统中,尤其在WINDOWS操作系统的分时事件驱动运行模式下,由于系统固有的存储器刷新、时钟中断,以及运行中硬件中断、DMA操作、任务切换,必须有较长的防跟踪延时才能保证合法程序正常运行,要注意在软硬盘操作时对密码数据操作的影响。

2 应用举例

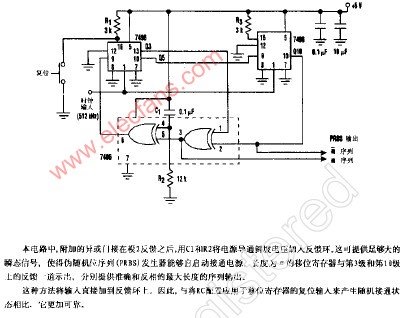

2.1 并行口加密电路

2.1 并行口加密电路

在PC机系统中,一般打印机并行接口包括单向输出的8条数据线D0~D7和四条控制线、5条状态输入线,因此每次读操作只读取4bits密码,其加密电路原理框图如图3所示。由于并行口不提供电源,将联机控制信号SLCT置高提供的电流很小,因此直接挂在并行口上的电路必须选用规模不大的低功耗器件。

经并行口控制移位寄存器产生密码的基本操作步骤是:(1)SLCT置高加电;(2)STROBE触发经D0~D8写入16位控制字,选通加密电路,否则打印口正常;(3)初始化信号INIT置低,STROBE选择预置移位寄存器和移位计数器;(4)INIT置高选通移位时钟;(5)检测数据是否准备好;(6)换行控制AUTO LF置高,在STROBE脉冲作用下数据按4bits输出供CPU读取;(7)SLCT置低断电。

防跟踪记数器由移位计数器满状态启动,其溢出脉冲使触发器翻转选通三态门,扰乱输出数据。防跟踪记数器和移位寄存器时钟可由门电路构成的RC振荡器产生。

2.2 ISA总线加密电路

与并行口方式相比,通过总线方式对加密电路的移位寄存器和移位记数器的预置、输入数据的异或解密等操作更灵活、方便,并可与其它电路结合,其原理框图与图1相似。总线接口电路对端口地址和控制信号译码,产生移位寄存器和移位记数器输入写、移位寄存器及异或解密输出读信号,读信号清零防跟踪记数器并阻断其时钟。在ISA总线接口中,移位寄存器时钟用OSC或总线时钟BCLK,而防跟踪记数器时钟可采用移位时钟或状态持续变化的总线控制信号及状态信号,如:地址锁存信号BALE、刷新指示信号REFRESH、DMA操作允许信号AEN(因用于I/O地址译码,隐蔽性好)等,用REFRESH信号时计数器规模小、运行可靠,但是切断该信号防跟踪功能不起作用,密码数据仍正常产生。

2.3 单片机/ DSP系统程序加密电路

早期的单片机系统大都用扩展EPROM作为程序存储器,这种方式目前在高速单片机/DSP中仍然很常用。对于程序量小,不需外部程序寻址的简单系统(如微狗),采用内置EPROM/FLASH RAM、带加密控制字的MCU(如GMS97C2051)本身就能可靠地保护程序;因此我们的讨论只限于用扩展程序存储器的系统。

早期的单片机系统大都用扩展EPROM作为程序存储器,这种方式目前在高速单片机/DSP中仍然很常用。对于程序量小,不需外部程序寻址的简单系统(如微狗),采用内置EPROM/FLASH RAM、带加密控制字的MCU(如GMS97C2051)本身就能可靠地保护程序;因此我们的讨论只限于用扩展程序存储器的系统。

对扩展程序存储器的加密保护可通过对其数据和地址线的异或/取反扰乱来实现,其目的都是不能直接获取程序存储器内部保存的数据。由于X=X+K+K,X=X,因此在系统工作时由硬件实现代码和密钥的异或/取反操作可得到正确的程序(文献[2]中用二级异或提高加密强度的观点不正确,因为Y=X+K1+K2=X+K),其原理如图4所示。通常单片机加密的方式是密钥固定不变,或CPU读取程序代码的同时,从另一片EPROM读取密码,使每一代码对应一密钥。这两种方式的解密只需用简单的组合逻辑电路,对前一种方式,用逻辑分析法很容易求解逻辑关系而解密,后一种方法进行逻辑分析的工作量虽然大大提高,但密钥本身容易被直接获取。因此我们用m序列产生器动态产生密钥,将解密的组合逻辑电路与时序逻辑相结合,而较复杂时序逻辑的分析是很困难的。

对8031、MC6085兼容系列的单片机系统,编程使开始的一段初始化程序顺序执行,系统复位时自动对移位寄存器设初值,复位后程序存储器的读信号同时作为移位时钟,使每条指令的密钥不断变化;在第一次执行循环、跳转指令前,程序发控制字阻断移位时钟,使以后的程序密钥相同。在高速DSP系统中,一般上电后将低速EPROM中的程序加载到高速SRAM中运行,可使EPROM的读控制信号一直作为移位时钟,使密钥不断变化;如果用串行口方式加载,程序解密操作与数据通信中的数据解扰相同,数据输出时钟直接作为移位时钟。单片机/DSP作为微机系统的协处理器时,单片机/DSP的代码一般经总线装载,可将加密代码与移位寄存器输出的密钥异或解密,输出到单片机/DSP的程序RAM。

系统运行时,用于MCU/DSP程序保护的防跟踪计数器时钟一直有效,这样可以防止仿真器的跟踪。防跟踪计数器要用程序读或其相关信号清零,有的DSP从内部RAM运行程序时,程序读无相应输出信号,这时可用定时器中断或程序中及时插入的代码来清零。

上述介绍应用移位寄存器产生伪随机数据对程序进行加密的一些方法,曾在我们设计的系统中得到验证,整个电路的设计不复杂,占用PLD 器件的资源不多,完全可结合在系统的硬件逻辑设计中。使用8/16位的移位寄存器时,密钥量有限,制约了加密的复杂度,使用者应根据设计要求和自己的经验,引入各种非常规的操作方式,这样就可以用简单的硬件电路,很好地实现软件和系统的保护。

- 伪随机序(5146)

相关推荐

PLD/FPGA的分类和使用有哪些?

PLD/可编程逻辑器件的入门知识

PLD在消费电子领域的应用

PLD在消费电子领域的应用

PLD在消费电子领域的挑战

PLD的应用

加密芯片

随机函数不是很随机

AES 256加密认证芯片介绍 带加密认证功能的EEPROM

FPGA电路实现:m序列及应用

GPS数据加密系统的DES IP怎么实现?

M487芯片CRYPTO模块中对称加密AES功能测试方案

MATLAB中计算方式生成随机序列

MM32 MCU加密方法

PIC16F628A中的随机输出

PSoC 3伪随机序列PRC问题

PSoC 4 伪随机序列 (PRS)

Quartus VHDL程序问题

[Mill]FPGA无线通信课程连载——扰码的原理及实现

[求助] 将设计的伪随机码发生器组合成整体进行调用

[求助]基于FPGA的伪随机码发生器的设计与实现

keil-O2优化时系统自带的伪随机数会导致死机

stm32伪随机的使用

【LinkIt 7687试用体验】8.加密算法中真随机数的产生方法

【NUCLEO-F412ZG试用体验】之硬件随机数。

【assingle分享】labview随机数发生器

【原创】基于FPGA的M序列发生器设计

【总结】LabVIEW随机数发生器

【锆石A4 FPGA试用体验】——小炮与锆石A4的故事(11)——基于FPGA的m序列发生器

一种基于FPGA的真随机数发生器设计与实现

一种基于混沌和小波变换的大容量音频信息隐藏算法

利用DSP系统实现多路测量信号扩频传输实现

基于FPGA技术的Logistic映射PN序列

基于FPGA的扩频系统设计(附代码)

如何实现FPGA滑动相关法伪码捕获?

学习笔记 | 基于FPGA的伪随机数发生器(附代码)

定制化加密芯片优势和产品特点

定制型加密芯片这是一款采用随机变量交换系统的认证加密芯片,请问定制化加密芯片优势在哪里?

扩频通信系统的分类及原理

无线通信中的扰码

有谁知道控制PRS伪随机序列模块吗?

求教!!LabVIEW怎样数据的随机化

真随机数发生器在信息安全系统中的应用

通过USBN9603/P89C51平台实现USB接口硬件加密

采用PLD实现视频接口设计

高安全、高性能、高性价比 加密芯片 分享

高安全、高性能、高性价比 加密芯片 分享

伪随机系列及编码.ppt

0

0一种基于随机序列的RFID安全协议

12

12用单片机实现SRAM工艺FPGA的加密应用

24

24CDMA伪随机码

5

5基于随机码数列的文件加密算法的实现

28

28基于混沌序列密码的网络信息加密系统

22

22Galileo系统伪随机序列生成及其FPGA实现

7

7基于PLD及FPGA的频率与相位测量系统设计与实现

30

30基于过拟合神经网络的混沌伪随机序列

6

6彩色图像的双随机相位加密隐藏技术

28

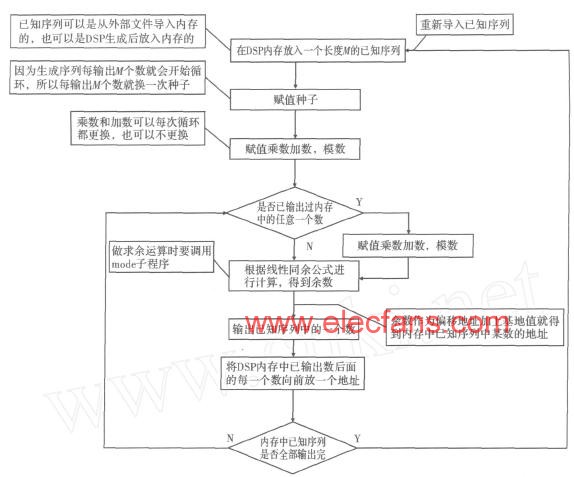

28基于DSP的任意长度伪随机序列产生方法

10

10一种混沌伪随机序列发生器的FPGA实现

52

52M序列伪随机码在测距回答概率控制中的应用

1529

1529

M序列伪随机码在测距回答概率控制中的应用

1091

1091

伪随机序列及PLD实现在程序和系统加密中的应用

660

660

FPGA的伪随机序列发生器设计

3332

3332

基于DSP的任意长度伪随机序列产生方法

1997

1997

Lorenz系统混沌加密算法研究

30

30一类序列信号检测器的实现方案

41

41基于TDERCS伪随机序列发生器的FPGA设计与实现

27

27基于计算全息的菲涅尔双随机相位加密技术

37

37基于Altera的DSP Builder工具箱的伪随机序列产生器设计方法

0

0用FPGA硬件实现多路伪随机序列应用适应光学SPGD控制算法设计

1631

1631

混沌动态随机分组与随机调制FRFT旋转因子

1

1Logistic方程混沌信号加密实现

1

1基于SPGD控制算法自适应光学系统的伪随机序列的设计与要求

2662

2662

如何设计一个用于数字图像加密的序列密码算法

0

0基于SRAM的可重配置电路PLD

675

675

基于伪随机序列的噪音干扰FPGA实现

2102

2102如何使用FPGA实现伪随机数发生器

24

24 电子发烧友App

电子发烧友App

评论