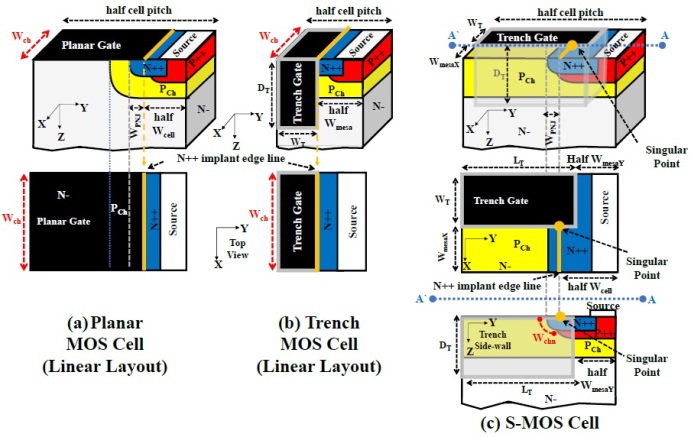

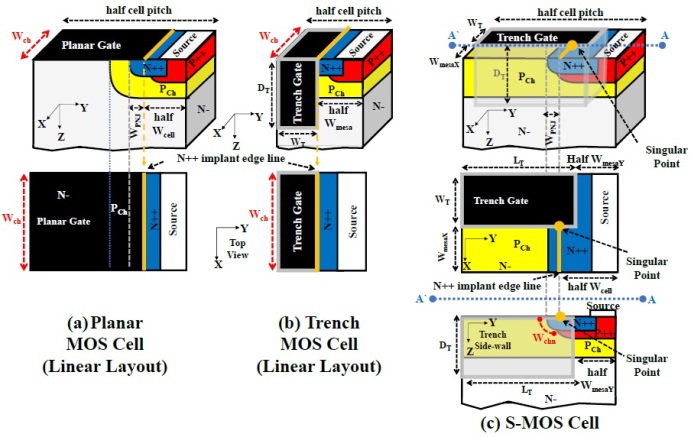

结构上调整和实施了 S-MOS 概念。如参考文献中所述,提供了全套静态和动态结果,用于将 S-MOS 与采用平面和沟槽 MOS 单元设计的参考 SiC MOSFET 2D 结构进行比较。

2022-07-26 09:10:48 573

573

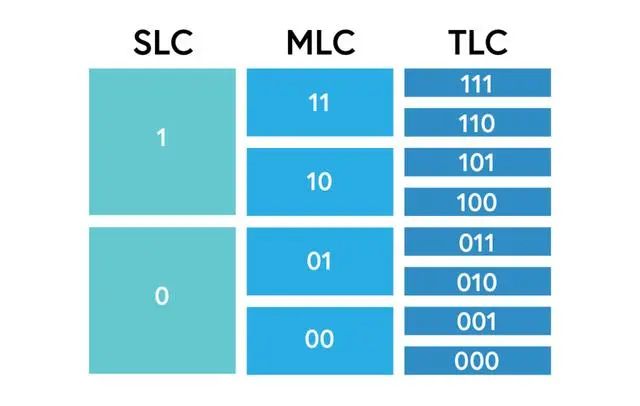

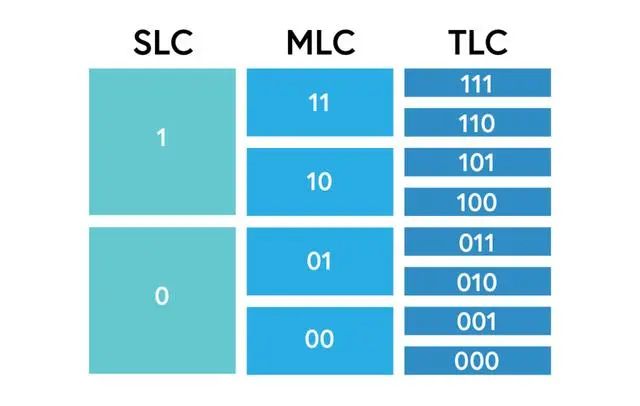

就基本的 SSD 存储单元而言,有 SLC、MLC、TLC 和 QLC。其中,TLC 是最受欢迎的,不过,QLC 最终将取代它们。在 I/O 方面,有 SATA 和 NVMe。

2022-08-26 16:41:35 3275

3275

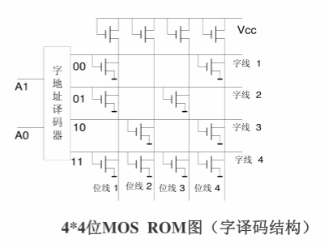

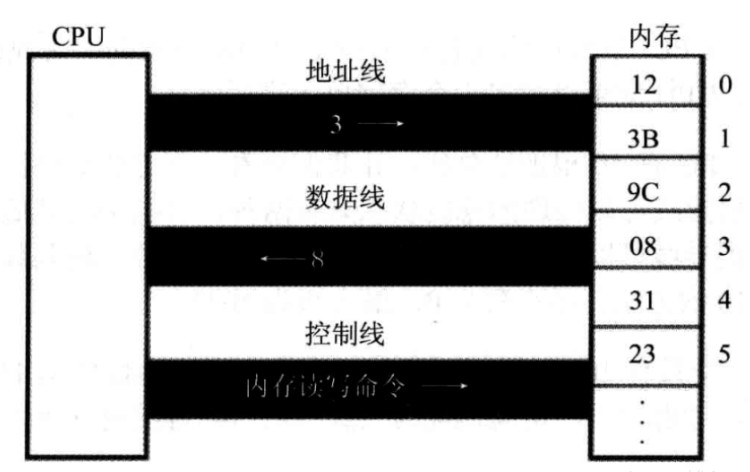

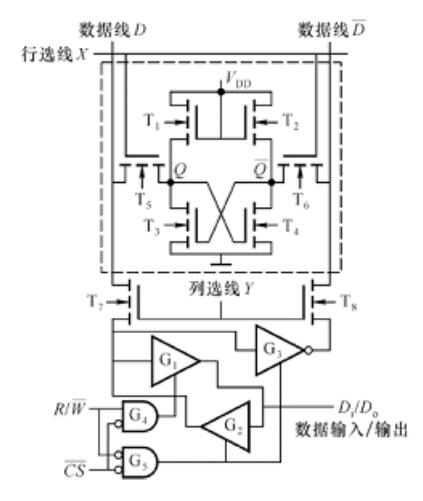

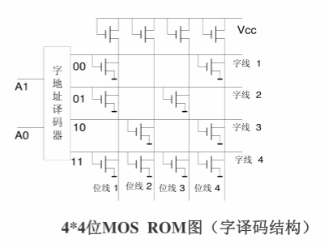

地址译码器根据地址信号总线,选中相应的存储单元。假设译码器有j条地址输入线,则可以寻址2的j次方个存储器单元,则存储矩阵由2的j次方个存储器单元组成,每个存储单元为k位。

2022-10-18 17:08:18 4345

4345

在芯片设计时,通常需要用到各种类型的存储单元,用以临时或者永久地存储数据。根据应用场合的不同,所用到的存储单元也不同。本文对常见的几个存储单元进行了介绍,并简述了其工作原理和特点。需要特别

2022-12-02 17:36:24 1953

1953

SDRAM英文名是:Synchronous Dynamic Random Access Memory,即同步动态随机存储器,同步指存储器的工作需要参考时钟。

2023-04-04 17:11:32 3338

3338

牛津大学设计了一种新型计算机存储单元,可以同时通过电和光信号对其进行访问或写入,大幅度提升了带宽和功率效率,也进一步推动了芯片级光子学技术的发展。

2020-01-21 08:38:00 1375

1375 80C51单片机片内RAM低128个存储单元划分为哪4个主要部分?各部分主要功能是什么?

2011-10-08 16:10:02

方式边界对齐的数据存放方法主存的基本结构和工作过程存储系统的层次结构半导体存储器静态MOS存储器 SRAM静态MOS存储单元静态MOS存储器的结构动态MOS存储器 DRAM四管动态MOS存储元的工作原理

2021-07-28 07:59:20

mos管的基本参数,大家熟悉的必然是Ids电流,Ron导通电阻,Vgs的阈值电压,Cgs、Cgd、Cds这几项,然而在高速应用中,开关速度这个指标比较重要。上图四项指标,第一项是导通延时时间,第二项

2018-12-05 14:15:27

MOS管的半导体结构MOS管的工作机制MOS管的驱动应用

2021-03-08 06:06:47

MOS管是由加在输入端栅极的电压来控制输出端漏极的电流。MOS管是压控器件它通过加在栅极上的电压控制器件的特性,不会发生像三极管做开关时的因基极电流引起的电荷存储效应,因此在开关应用中,MOS管的开关速度比三极管快。

2023-03-12 05:16:04

张飞电子第四部,MOS管不像三极管的BE有固定压降,所以不知道怎么计算。运放那边输出开路时,MOS管导通,具体是怎么工作的。1、刚开始,三极管基极电流怎么算,可以用15/(7.5K+2K)估计

2021-04-27 12:03:09

本帖最后由 一只耳朵怪 于 2018-6-1 09:28 编辑

四个MOS管这么排列,Q3Q4是打开,Q1Q2是关闭, 电源是12V为啥AB两点的电压也有11多V,MOS是如何导通的呢,体二极管也是对立的。

2018-05-31 19:41:07

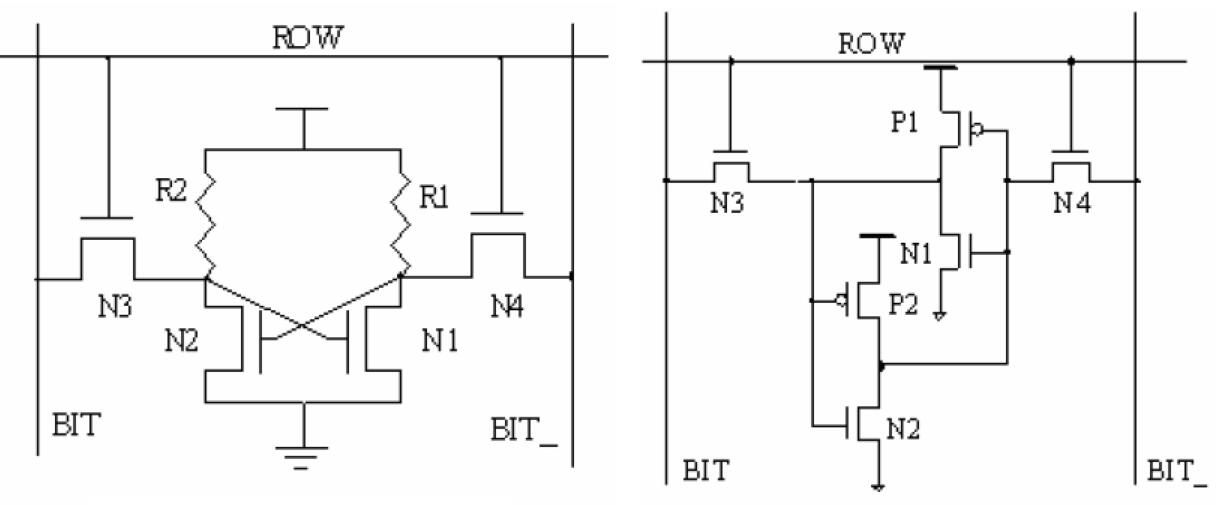

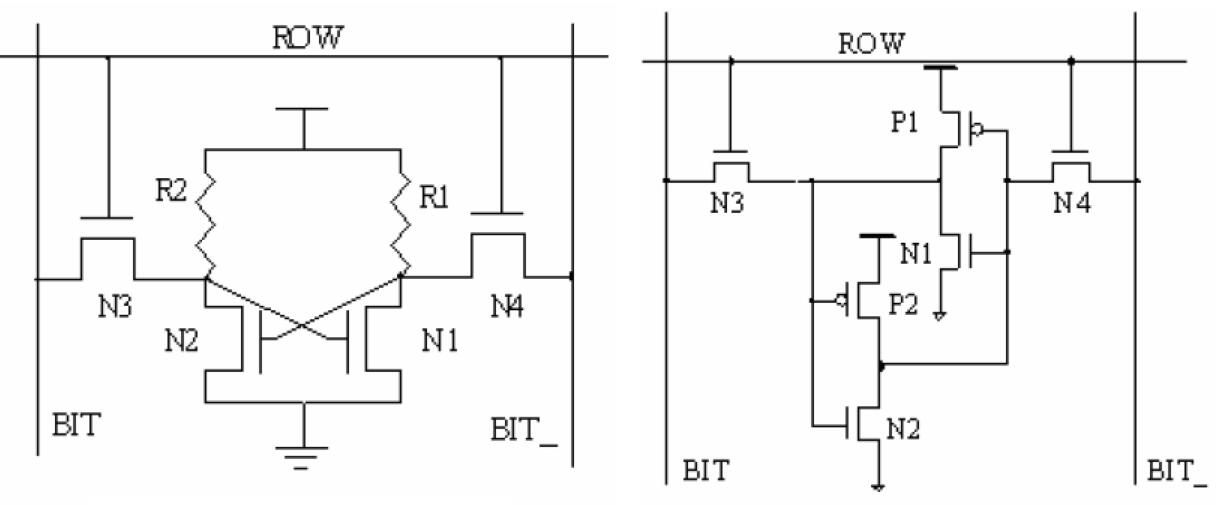

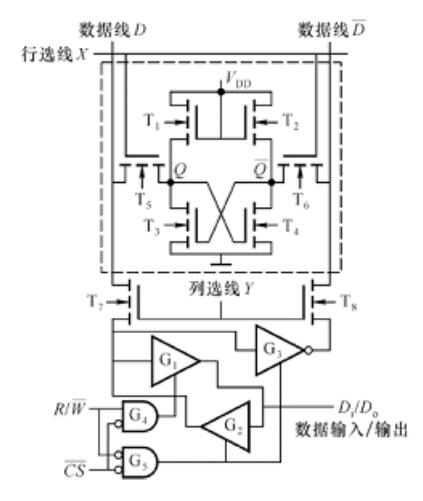

存储单元”是构成“静态存储器”(SRAM)的最基本单元。其中每一个BIT存储在4个晶体管构成的2个交叉耦合的反相器中。而另外2个晶体管作为“写控制电路”的控制开关。 有趣的是,搭建这个电路需要严格对称

2017-01-08 12:11:06

的四大法则。 法则之一:用N沟道orP沟道 选择好MOS管器件的第一步是决定采用N沟道还是P沟道MOS管。在典型的功率应用中,当一个MOS管接地,而负载连接到干线电压上时,该MOS管就构成了低压侧

2016-01-26 10:30:10

四引脚的Mos管那里有卖?{:soso__15078172537441236116_2:}

2012-08-09 14:47:33

四引脚的Mos管那里有卖?{:soso__15078172537441236116_2:}

2012-08-09 14:50:14

存储位元与存储单元是什么含义?数据通信的方式可以分为哪几种呢?

2022-01-21 07:17:58

设存储器读/写周期为 0.5us, CPU在1us内至少要访问一次。试问采用哪种刷新方式比较合理? 两次刷新的最大时间间隔是多少? 对全部存储单元刷新遍所需的实际刷新时间是多少?

2021-10-26 07:05:19

1.(判断题)DRAM上电时存储单元的内容是全0,而Flash上电时存储单元的内容是全1。(4分) A.正确B.错误 FLASH可保存 上电后不知道是啥2.(判断题)眼图可以用来分析高速信号的码间

2021-07-22 08:57:49

判断题:DRAM上电时存储单元的内容是全0,而Flash上电时存储单元的内容是全1

2017-08-23 09:29:31

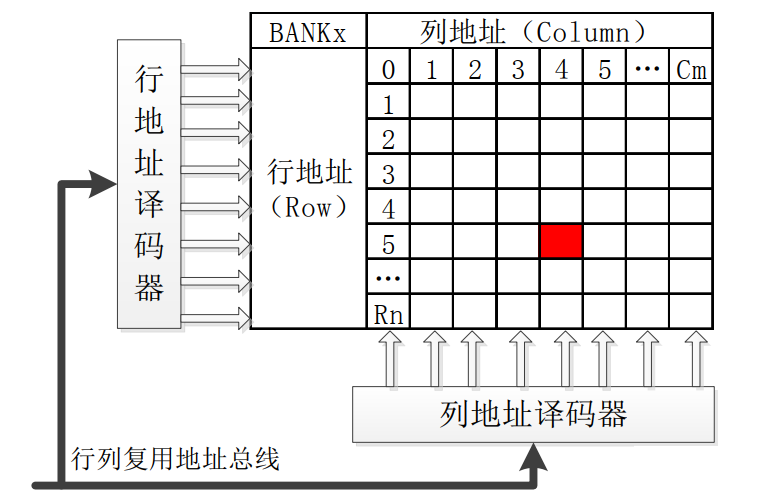

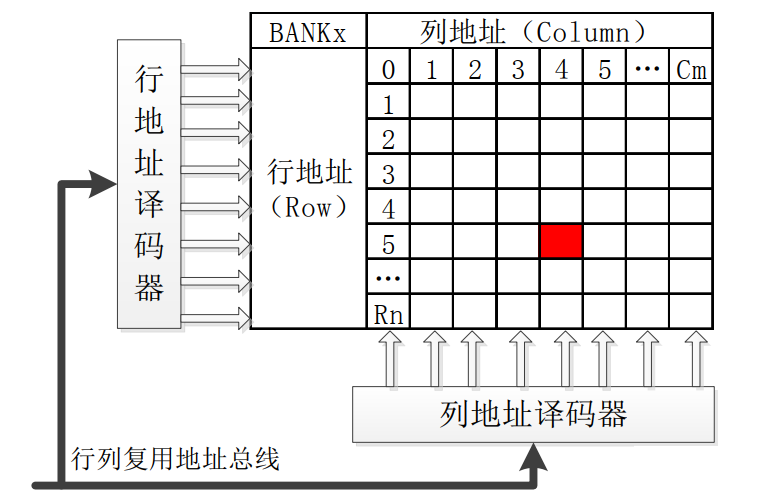

芯片。这时得到了4个 字长为4得芯片,这四个芯片按字方向扩展得到16K,说明一块DRAM芯片存储单元数位4K.而刷新是针对每块芯片来说的,所以我们只需要研究一块芯片的刷新机制按照存储矩阵形式,得到共有

2022-03-02 06:18:45

`具有EEPROM的存储单元的意法半导体动态NFC标签可以通过I2C接口和13.56Mhz的NFC来读写操作。M24SR系列产品提供给设计者广泛的特性: • 支持NFC forum 4类标准

2015-07-06 09:55:13

Nand Flash的物理存储单元的阵列组织结构Nand flash的内部组织结构,此处还是用图来解释,比较容易理解:图2.Nand Flash物理存储单元的阵列组织结构[url=][img=1,0

2018-06-12 10:10:18

请教Arm专家大侠: SOC内SRAM各存储单元, 其“每次上电冷启动后、还未写入应用数据前的初始状态数据”是否是由其硬件电路保证总是一样的(全0或全1)?不会随机变化(有时为0有时为1)? 能否从硬件原理角度简单说明下? 谢谢。

2022-08-19 15:37:40

五大部分组成,即存储单元阵列、地址译码器(包括行译码器和列译码器)、灵敏放火器、控制电路和缓冲/驱动电路。在图中A0-Am-1为地址输入端,CSB. WEB和OEB为控制端,控制读写操作,为低电平有效

2022-11-17 14:47:55

静态RAM的基本构造块是SRAM存储单元。通过升高字线的电平触发存储单元,再通过位线对所触发的存储单元进行读出或写入。在静态CMOS存储器中,存储单元阵列将会占去整个存储器芯片面积的一半以上,在一些

2020-06-05 15:18:24

niosii编译提示on-chip menmory 存储单元不够,怎么解决?

2015-01-18 09:31:43

的多少,即电容端电压的高低来表示“1”和“0”。DRAM每个存储单元所需的场效应管较少,常见的有4管,3管和单管型DRAM。因此它的集成度较高,功耗也较低,但缺点是保存在DRAM中的信息__场效应管栅极

2011-11-28 10:23:57

主存中存储单元地址是如何进行分配的?存储芯片的容量有多大?

2021-10-19 08:25:52

4.2.1.主存中存储单元地址的分配:存储字长:存储器中一个存储单元(存储地址)所存储的二进制代码的位数,即存储器中的MDR的位数。字(word) : 若干个字节组成一一个”字” ( word)。一

2021-07-28 06:43:06

什么是MOS管?MOS管的工作原理是什么?MOS管和晶体三极管相比有何特性呢?

2022-02-22 07:53:36

的通路,称为位线。每一个存储单元都能通过选择适当的字线和位线被唯一地定位。宇芯有限公司介绍关于SRAM存储器的读操作分析。 图1 六管单元的读出操作 SRAM存储单元读操作分析存储单元的读操作是指被

2020-04-29 17:27:30

存储单元构成由6个晶体管单元构成由4个晶体管单元(高电阻负载型单元)构成数据的写入方法<"1" 时>Word线电位为 high给予Bit线的电位(D=low, D=high

2019-05-27 20:59:42

存储器是由哪些存储单元构成的?存储器是用来做什么的?单片机中的数据存储器RAM有哪些特性呢?

2022-01-17 06:52:14

而影响后面的各项工作和事宜。立深鑫电子为大家总结出如何正确选取MOS管的四大法则。 法则之一:用N沟道orP沟道 选择好MOS管器件的第一步是决定采用N沟道还是P沟道MOS管。在典型的功率应用中

2018-11-08 14:13:40

在分析传统SRAM存储单元工作原理的基础上,采用VTC蝴蝶曲线,字线电压驱动,位线电压驱动和N曲线方法衡量了其静态噪声容限。 在这种背景下,分析研究了前人提出的多种单元优化方法。这些设计方法,大部分

2020-04-01 14:32:04

你好如何在不使用DDR内存控制器的情况下设计FPGA BRAM(或任何其他内存模块_SD,DDR以外的本地等)大容量存储单元?当我通过示例设计“VC707_bist”替换DRAM控制器和BRAM

2019-04-04 15:10:55

基于传统六晶体管(6T)存储单元的静态RAM存储器块一直是许多嵌入式设计中使用ASIC/SoC实现的开发人员所采用的利器,因为这种存储器结构非常适合主流的CMOS工艺流程,不需要增添任何额外的工艺步骤。那么究竟怎么样,才能实现嵌入式ASIC和SoC的存储器设计呢?

2019-08-02 06:49:22

怎么把单片机存储单元清0或置1?

2023-10-16 07:59:42

击穿,测量阻值很大,说明管子内部断路。动态测量区分MOS管和IGBT管先用万用表给管子的栅极施加电压,是场效应管建立起沟道,然后测量D、S及c、e之间的阻值,根据阻值的差异来区分MOS管和IGBT管

2019-05-02 22:43:32

怎么随机存取存储器ram中的存储单元

2023-09-28 06:17:04

静态存储单元和其读写控制电路组成的记忆体电路,对此的详细内容在四个晶体管搭建静态存储单元,加两个晶体管搭建写控制电路一文中。LY62L5128是一个CMOS SRAM。容量512KB(512K X 8

2016-08-30 04:32:10

MOSFET呢?既然Vgs不能大于20V,那我们就可以在G和S之间,加一个20V的稳压管,来防止干扰脉冲或是静电破坏MOSFET。 四,单片机控制MOSFET的应用技巧 说到底,MOS管主要是应用,按照

2018-11-08 14:11:41

模式也使得DRAM的集成度高于SRAM,一个DRAM的存储单元仅需要一个晶体管和一个小电容,而每个SRAM单元需要四道六个晶体管和其它的零件,故DRAM在大容量以及价格上会有优势。 FlashFLASH

2019-09-18 09:05:09

关于使用TMC5160芯片控制两相四线步进电机运动,用八个N型MOS管去控制电流流向,那么这几个MOS管是怎么工作的,为什么可以做到一端高侧MOS管导通,低侧MOS管截止呢?

2019-01-22 11:20:30

全局字线由行地址的高几位经全局字线译码器译码产生,它将贯穿整个存储阵列来驱动各个子模块的块内字线译码器;而块内字线则由全局字线、块选信号以及低几位的行地址相与产生,块内字线直接与存储单元的存取管相连

2020-05-19 16:20:45

为了完成直接数字频率合成技术的任意波形发生器的动态存储器的设计,文章采用了K4S641632B-TC75芯片,用S-AMP 负责实现放大/驱动,解决了存储单元中的电容容量很小的问题,保证了

2009-08-25 14:35:59 12

12 对第一代开关电流存储单元产生的时钟馈通误差做了合理的近似分析,设计了一种高性能开关电流存储单元。该电路仅在原存储单元的基础上增加了一个MOS管,使误差降为原来的4%,

2010-07-05 14:50:48 22

22 低电压甲乙类开关电流存储单元

引言 开关电流存储单元是电流模式采样数据信号处理系统的基本单元电路,其性能的优

2007-08-15 16:06:29 563

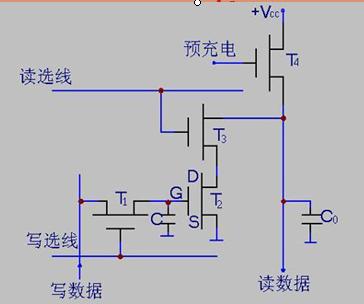

563 三态MOS动态存储单元电路

2009-10-10 18:45:49 1213

1213

用MOS管构成的存储矩阵

2009-12-04 12:24:50 1632

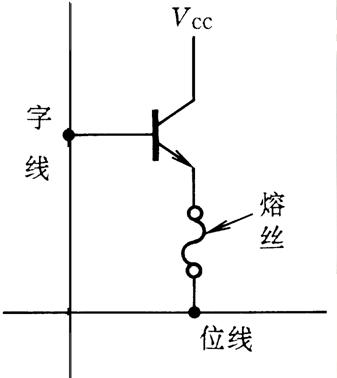

1632 熔丝型PROM的存储单元

2009-12-04 12:25:26 2228

2228

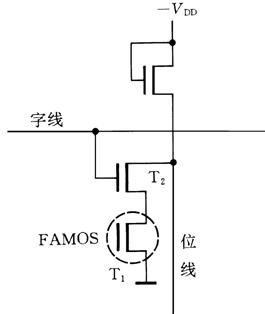

使用FAMOS管的存储单元

2009-12-04 12:27:29 875

875

E2PROM的存储单元

2009-12-04 13:03:57 1468

1468 E2PROM存储单元的三种工作状态

2009-12-04 13:04:45 1334

1334 六管NMOS静态存储单元

2009-12-04 15:30:03 6567

6567 单管动态MOS存储单元

2009-12-04 16:50:24 3757

3757 有比型动态MOS反相器

2009-12-04 17:31:04 1383

1383 无比型动态MOS反相器

2009-12-04 17:41:33 1372

1372 应用于超低电压下的SRAM存储单元设计_刘冰燕

2017-01-07 21:39:44 0

0 使用赛道存储单元的近阈值非易失SRAM_孙忆南

2017-01-07 21:45:57 1

1 记忆技术不停滞不前。存储器结构的变化速度更快和更有效的结构的创建和使用在连续几代人如DRAM SDRAM DDR DDR1、2、3、等。

2017-06-06 14:22:11 5

5 。O工P存储器的种类很多,很多是基于熔丝和反熔丝,本文介绍的O工P存储器基于反熔丝结构。在反熔丝O工P存储器中,通过对选中单元的编程改变了存储单元内部的结构。理想的读机制下,没有编程的存储单元读取时会读出0,而通过编程的存储单元在读取时会读出1。反

2017-11-07 11:45:21 11

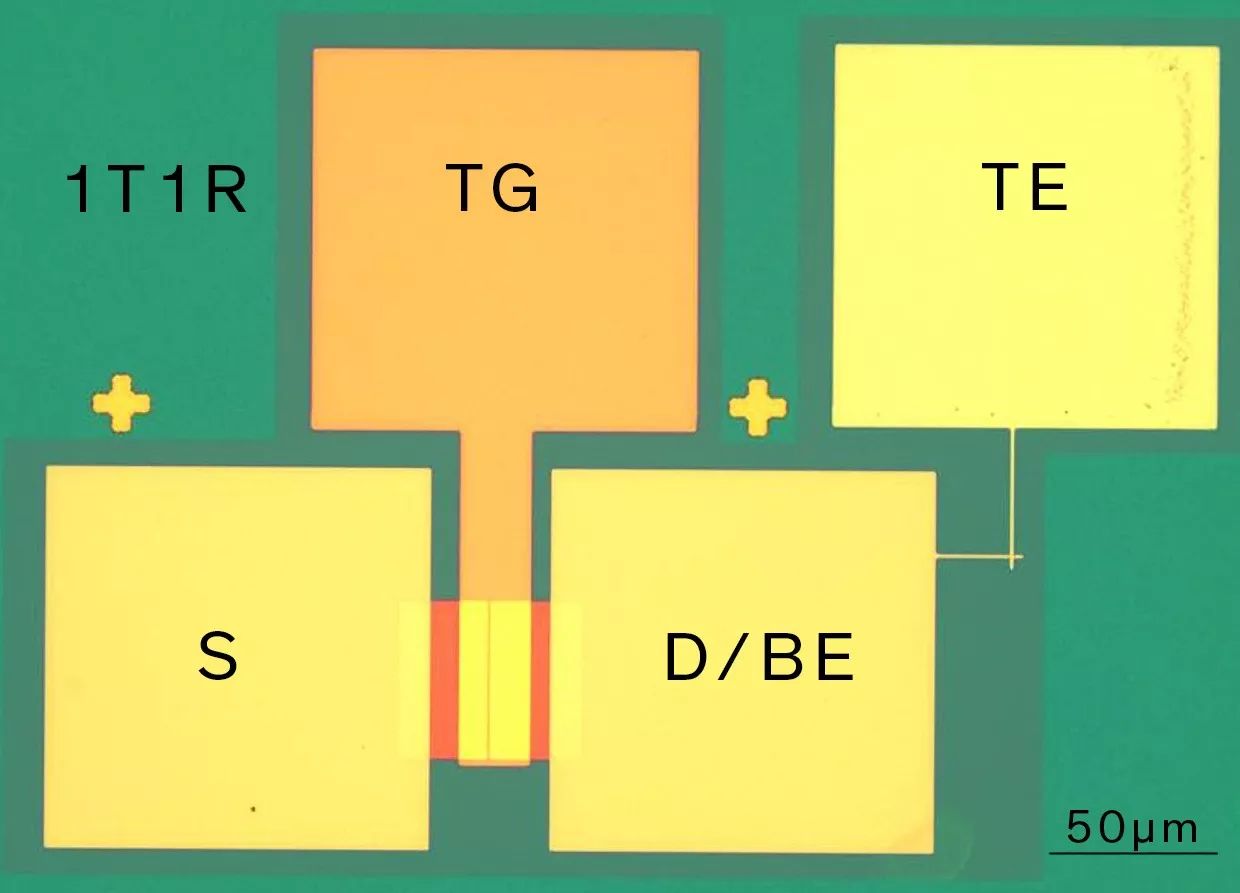

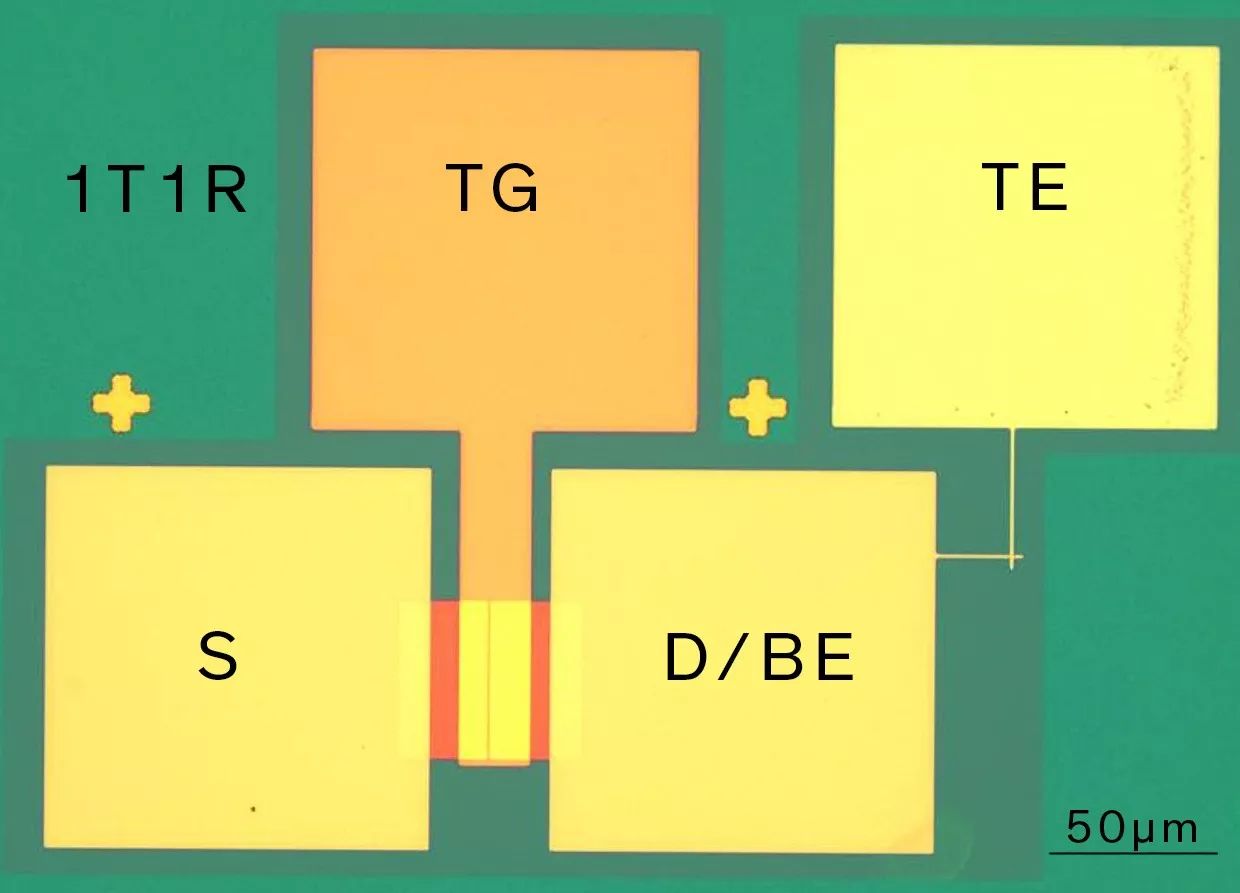

11 斯坦福研究人员开发的芯片被称为“单晶体管单阻变存储器”(1T1R)单元。这种1T1R存储单元相对于含有阻变存储器但没有晶体管的存储单元,能够提供极大好处。

2018-01-23 17:23:59 6482

6482

东芝公司近日发布了BENAND产品。该产品基于单层存储单元(SLC)NAND闪存,并且内嵌错误纠正功能(ECC)。BENAND产品正式批量生产的时间为2012年3月。BENAND在东芝公司最先

2018-10-08 17:11:00 1940

1940 存储单元的地址是从0开始的一个一维数据地址。

2019-10-13 14:30:00 12833

12833

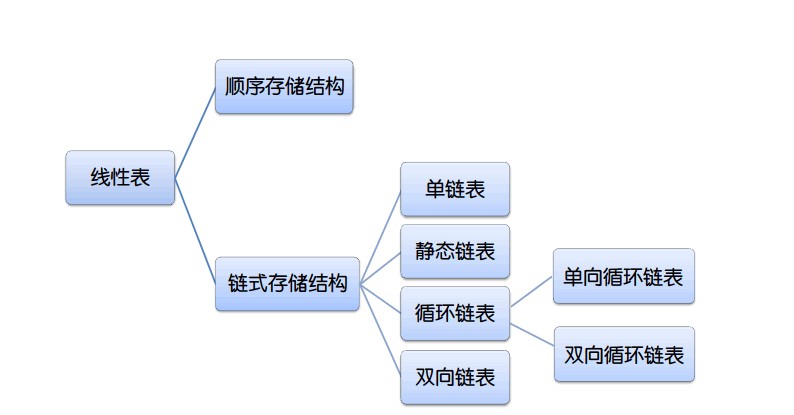

顺序存储方法: 该方法把逻辑上相邻的结点存储在物理位置上相邻的存储单元里,结点间的逻辑关系由存储单元的邻接关系来体现。

2019-10-27 12:31:00 43885

43885

铠侠株式会社(Kioxia Corporation)宣布开发出创新的储存单元结构“Twin BiCS FLASH”。该结构将传统3D闪存中圆形存储单元的栅电极分割为半圆形来缩小单元尺寸以实现高集成化。

2019-12-24 17:01:22 3210

3210 存储单元的作用:可以进行读写操作以及存放数据。

2020-03-22 17:34:00 4034

4034 静态RAM的基本构造块是SRAM存储单元。通过升高字线的电平触发存储单元,再通过位线对所触发的存储单元进行读出或写入。在静态CMOS存储器中,存储单元阵列将会占去整个存储器芯片面积的一半以上,在一些

2020-05-14 09:19:47 3282

3282

个名为Row Hammer的顽固安全漏洞。 Spin Memory的垂直环绕栅晶体管可以缩小MRAM和RRAM存储单元。 Spin Memory将设备称为通用选择器(Universal

2020-09-04 16:10:13 2090

2090 静态存储区存放全部的全局变量, 这些变量将在链接之后产生, 程序执行完毕就释放, 程序执行的过程中它们占据固定的存储单元, 而不会动态的进行分配和释放。

2020-11-01 10:51:28 3292

3292

按照数据存取的方式不同,ram中的存储单元分为两种:静态存储单元一静态RAM(SRAM);动态存储单元动态RAM(DRAM)。 1.静态存储单元(SRAM):它由电源来维持信息,如触发器,寄存器

2020-12-02 14:31:30 2182

2182

该方法把逻辑上相邻的结点存储在物理位置上相邻的存储单元里,结点间的逻辑关系由存储单元的邻接关系来体现。

2020-12-02 10:17:55 35091

35091 数据必须首先在计算机内被表示,然后才能被计算机处理。计算机表示数据的部件主要是存储设备;而存储数据的具体单位是存储单元;因此,了解存储单元的结构是十分必要的。

2021-01-08 10:03:55 2269

2269 采用HSPICE分别对设计的存储单元、延迟单元和积分器电路进行了仿真,晶体管模型选用TSMC0.18μm标准数字工艺参数。电源电压为±1 V;输入电流iin=40μA,信号频率fin=100 kHz

2021-02-18 10:06:39 1450

1450

存储体是属于计算机系统的重要组成部分,以存储为中心的存储技术。存储单元通常按字节编址,一个存储单元为一个字节,每个字节能存放一个8位二进制数。

2022-01-03 16:17:00 8804

8804 存储解决方案的全球领导者铠侠株式会社(Kioxia Corporation)今天宣布发布通用闪存(UFS) 3.1版[1]嵌入式闪存设备。该设备采用了其创新的每单元4字节的四层存储单元(QLC)技术

2022-01-20 12:26:52 233

233 OCE28V256X是一种单电压(3.3V)、异步、rad-hard 32kbit x8内存设备,使用抗-基于保险丝的一次性可编程(OTP)存储单元。采用了标准的1 30nm CMOS工艺用于

2022-06-08 11:22:48 1

1 中国科学院上海微系统与信息技术研究所研究员宋志棠、王浩敏组成联合研究小组,首次利用GNR边缘接触制备了世界上最小的相变存储单元器件。

2022-08-02 14:26:26 902

902 闪速存储器(Flash Memory)又称闪存(Flash),是一种非易失性存储器,用存储单元阈值的高低表示数据。浮栅(Floating Gate )场效应管(见图5-80)是Flash存储单元采用的主要技术。

2022-08-08 15:46:00 1076

1076 问:PICC编译器会自己分配存储单元到其他bank吗?还是需要用户来强制分配呢? 答:你需要用一个bankx限定符来分配存储器到其他bank。例如: bank1 char fred; 这将

2023-01-22 16:30:00 448

448 在当前计算密集的高性能系统中,动态随机存储器(DRAM)和嵌入式动态随机存取存储器(embedded-DRAM,eDRAM)是主要的动态快速读/写存储器。先进的 DRAM 存储单元有两种,即深沟

2023-02-08 10:14:57 5004

5004 SSD主要由控制单元和存储单元(当前主要是FLASH闪存颗粒)组成,控制单元包括SSD控制器、主机接口、DRAM等,存储单元主要是NAND FLASH颗粒。

2023-09-25 09:45:51 161

161

SSD主要由控制单元和存储单元(当前主要是FLASH闪存颗粒)组成,控制单元包括SSD控制器、主机接口、DRAM等,存储单元主要是NAND FLASH颗粒。

2023-10-27 10:27:03 198

198

内部功能,这种产品也被称作异步 DRAM 。 DRAM 的存储单元的长宽比接近 1:1,为阵列(Array)形状,存储器的地址线则被分为行(Row)(地)址线和列(Column)(地)址线。行址线用来

2023-11-17 09:26:27 382

382 SRAM 中的每个存储单元由多个触发器构成。每个触发器可以存储一个位的数据,并在电源供电时一直保持该状态,不需要刷新操作。

2024-02-05 09:31:57 952

952

电子发烧友App

电子发烧友App

硬声App

硬声App

573

573

3275

3275

4345

4345

1953

1953

3338

3338

1375

1375 12

12 22

22 5

5 11

11 6482

6482

1940

1940 3210

3210 3282

3282

2090

2090 3292

3292 2182

2182

2269

2269 1450

1450

8804

8804 233

233 1

1 902

902 1076

1076 448

448 5004

5004 161

161

198

198

382

382

评论