相位噪声是时钟、射频频综最为关注的技术指标之一。影响锁相环相噪的因素有很多,比如电源、参考源相噪、VCO 自身的相噪、环路滤波器的设置等。其中,电源引入的低频噪声往往对锁相环的近端相噪有着很大

2022-08-05 10:25:00 3998

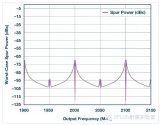

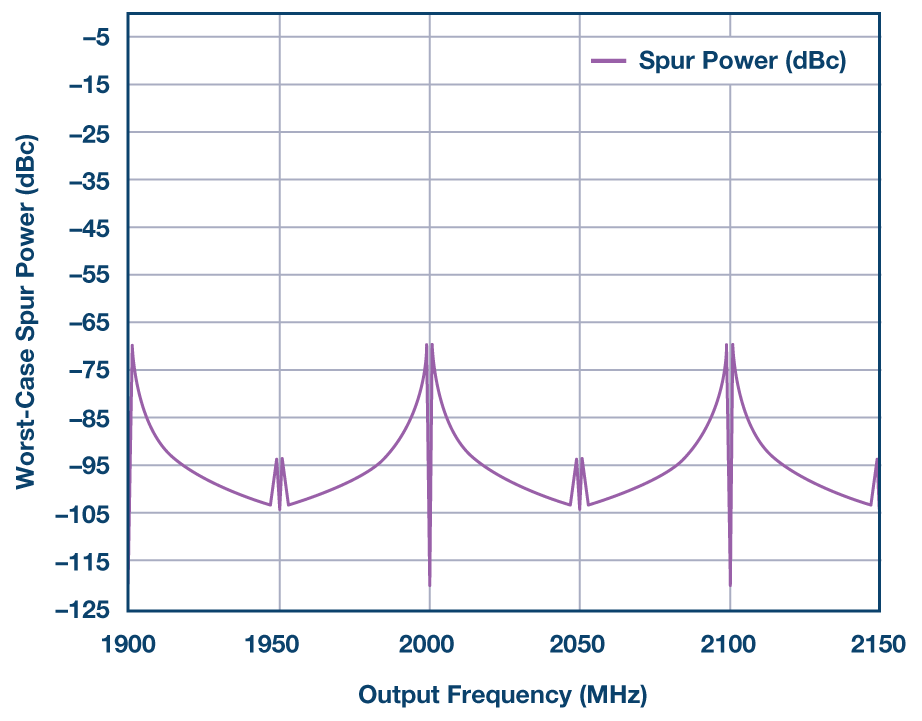

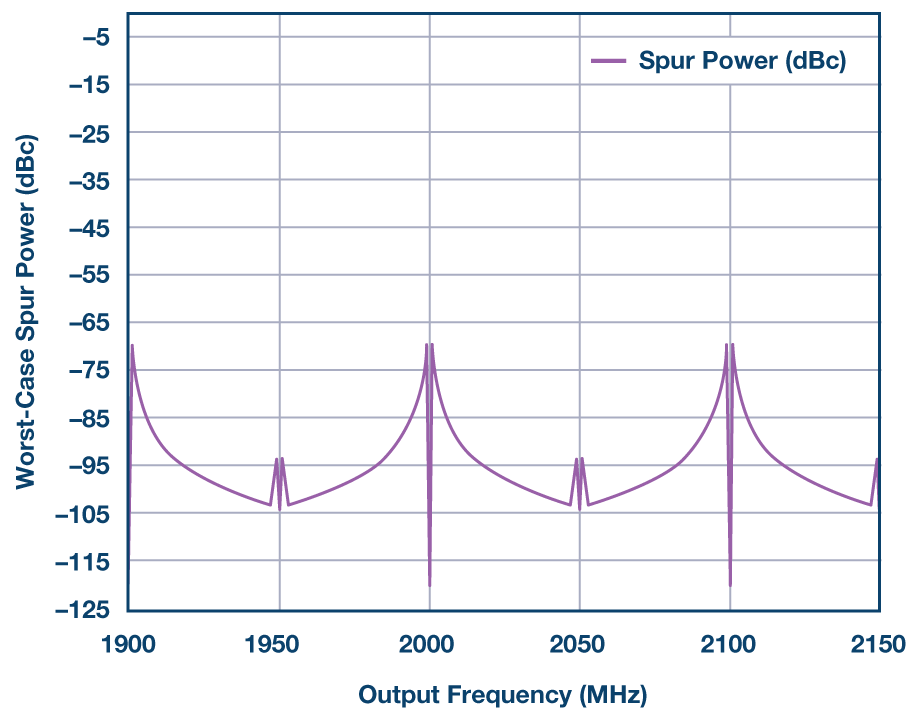

3998 锁相环 (PLL) 和压控振荡器 (VCO) 输出特定频率的RF信号,理想情况下此信号应当是输出中的唯一信号。但事实上,输出中存在干扰杂散信号和相位噪声。本文讨论最麻烦的杂散信号之一——整数边界杂散,它如何仿真与消除,你真的搞清楚了?

2023-05-22 11:10:35 10630

10630

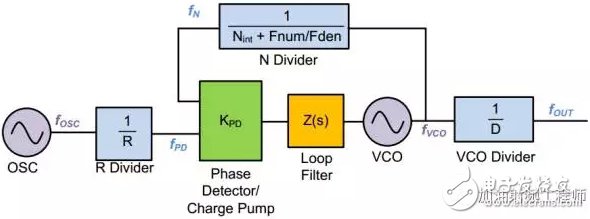

现在很多集成VCO的频率合成器的设计思想,都是利用输出端加分频器来扩展输出范围。

2019-08-22 06:18:43

达到高鉴相频率,低相噪的目的,甚至会超过小数分频的锁相环。另外也需要考虑由于采用了杂散补偿电路,所以该电路会增加环内的相位噪声。 从杂散性能上看,在较小的信道间隔(1MHz)上,小数分频的锁相环的杂散

2019-01-16 12:27:07

的锁相环杂散的分布规律是什么?A:小数分频的锁相环由于应用在工作的鉴相频率较高,所以其参考杂散也会分布到偏离载波很远的位置上,环路滤波器可以进行有效抑制。所以在实际使用中,这种参考杂散可以不予考虑

2017-04-27 15:58:16

).TX通道基带不发数据时,杂散和[size=13.3333px]噪底大概哪个量级?是否在FDD模式下可以关掉发射通道?[size=13.3333px]2).看到发射通道IQ调制器后,模拟部分有个衰减器

2018-12-27 09:24:47

AD9912 DVDD1.8V电源输出端 Pin3、5、7 。有500MHz的频谱分量输出,与其它pin比幅度最大,达-38dBm。2、怀疑AD9912内部存在无法关闭的固定2分频器,将sysclk

2019-03-08 15:14:23

我使用ADF4351,其输出在中心频率偏移184k附近有杂散输出,通过减小环路带宽,减小充电电流等,杂散有一定的降低, 此时带来靠近中心频率出的噪声升高,通过对比不同的板卡,都存在类似的现象,环路

2018-10-12 09:24:23

DC1959B-C,用于LTC6948IUFD-3超低噪声和杂散小数N分频合成器的演示板,集成VCO。演示电路采用LTC6948,具有集成VCO的超低噪声和杂散小数N分频合成器

2019-07-17 06:34:42

DC1959B-D,用于LTC6948IUFD-1超低噪声和杂散小数N分频合成器的演示板,集成VCO。演示电路采用LTC6948,具有集成VCO的超低噪声和杂散小数N分频合成器

2019-07-19 08:59:53

在使用HMC704中遇到非整数边界杂散问题,麻烦各位看看: REFin:100MHz, N=2, 鉴相频率50MHz输出分别为10025MHz,10050MHz和10075MHz环路滤波器带宽:1

2019-02-21 14:05:56

70MHz的时候,只改变AD9912的输出,HMC833寄存器不改变。 现在遇到的问题如下: 1.在低频段(1.5GHz内)有一大片鉴相频率整数倍的杂散信号存在,杂散信号与主信号间的差距大概在

2019-02-22 12:27:30

BiCMOS低噪声可编程分频器,采用3x3 mm无引脚表贴封装。 在400 MHz至6 GHz 输入频率范围内,该电路可编程并采用N = 1至N = 4分频。 该器件具有高电平输出功率(最高为6 dBm单端

2018-10-17 15:46:51

低噪声可编程分频器,采用3x3 mm无引脚表贴封装。 在400 MHz至6 GHz 输入频率范围内,该电路可编程并采用N = 1至N = 4分频。 该器件具有高电平输出功率(为6 dBm单端)、极低

2018-10-17 15:49:04

差了7dB

3.139G,无论是VCO输出还是4分频,8分频输出,其相噪都不会随功率变化,仅二分频会有此现象;

TICS pro配置如下

相噪测试数据如下:

请问该现象是否正常,造成该现象的原因是什么?

2024-11-08 16:16:51

请问鉴相频率和电荷泵电流关系如何评估,以及对杂散相噪的相关评估?

2024-11-11 06:58:46

手册中的图94找到一个4分频器,这个4分频器在5GHz输入时会产生1.25GHz输出,这个分频器的输出会泄露到输出吗?请帮忙解释一下1250MHz的杂散来源?另外图94的4分频能关闭吗?

谢谢!

2023-12-01 12:31:14

比如@100KHz处相位噪声-115dBc/Hz,过了二分频器或二倍频器后@100KHz处相噪为多少

2018-08-03 08:49:18

AD9522-4 / PCBZ,用于AD9522-4的评估板是一款超低噪声PLL时钟合成器,具有集成VCO,时钟分频器和多达24个输出。 AD9522具有自动保持功能和灵活的参考输入电路,可实现非常

2019-02-22 09:35:23

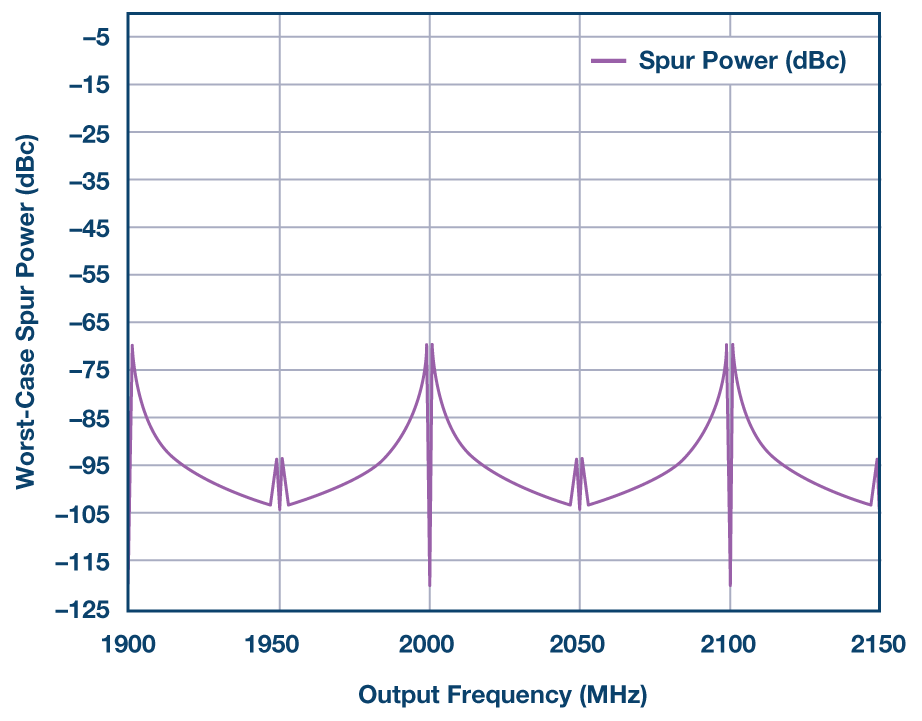

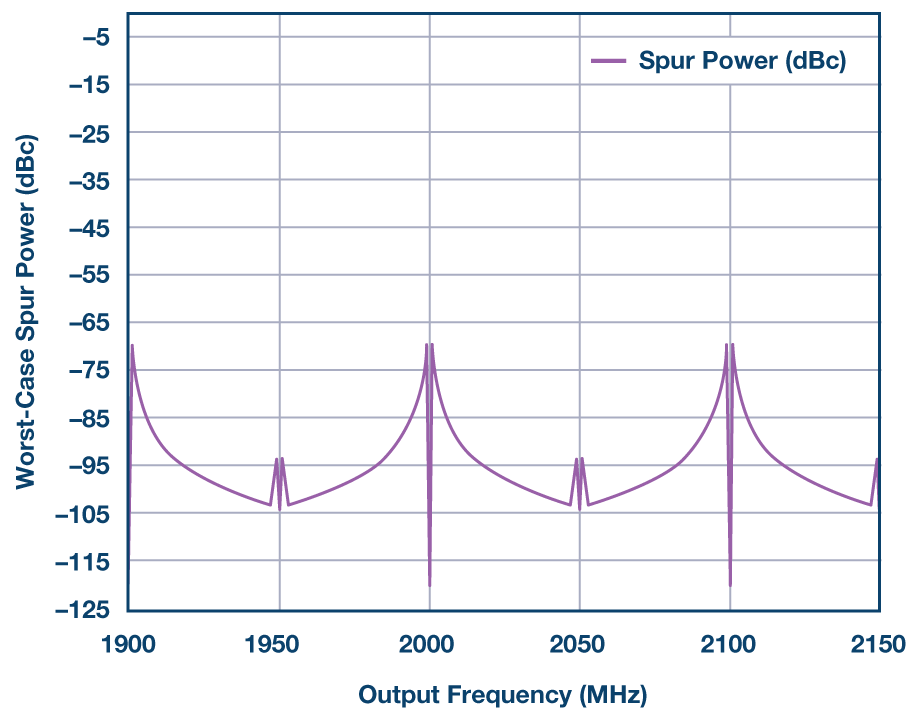

VCO输出的整数边界杂散最低。如何改变PFD频率?一般而言,在PLL/VCO系统中,PFD频率是固定的。然而,对于大部分可编程时钟分配源、PLL参考输入分频器和PLL小数N分频调制器架构来说,现在可以

2019-10-11 08:30:00

小数分频器整数边界杂散问题的提出小数分频器整数边界杂散的优化设计

2021-04-19 08:32:15

DDS的工作原理是什么如何降低输出信号杂散电平?DDS作为分频器在锁相环中的应用研究

2021-04-22 06:09:32

所示。该器件具有一个输出分频器(在VCO之后),但输出频率和VCO频率都接近20MHz的整数倍。这种设置将迫使任何PLL产生分数杂散。…

2022-11-18 07:51:05

20MHz的输入频率生成540.01MHz的输出频率,如图1所示。该器件具有一个输出分频器(在VCO之后),但输出频率和VCO频率都接近20MHz的整数倍。这种设置将迫使任何PLL产生分数杂散。 图1

2018-09-06 15:11:00

小弟正在调试一款X波段(9.6-10.8GHz)的锁相环,采用的是内部集成VCO的HMC778LP6CE芯片。在调试中,我发现在距中心频率50Hz整数倍的频率处有很多杂散,请问各位大神这些杂散

2014-07-21 15:47:54

DC1959B-B,用于LTC6948IUFD-2超低噪声和杂散小数N分频合成器的演示板,集成VCO。演示电路采用LTC6948,具有集成VCO的超低噪声和杂散小数N分频合成器

2019-02-28 09:49:17

DC1959B-D,用于LTC6948IUFD-4超低噪声和杂散小数N分频合成器的演示板,集成VCO。演示电路采用LTC6948,具有集成VCO的超低噪声和杂散小数N分频合成器

2019-02-28 09:33:14

后发现本振信号是经过VCO输出分频得到,不知道分频器有几个?一个PLL能否提供出两路不同的本振信号以供发射?

2018-12-18 09:18:58

您们好:最近做的项目中需要使用到分频比很大的分频器,故计划使用ADF4106作为分频器使用,请问ADF4106可以实现分频器的功能吗,可以的话相噪性能怎么样呢?谢谢!

2018-10-08 10:34:02

各位工程师,你们好!对于ADF4351的快速锁定模式,我有几点疑惑:1、和传统三阶环路滤波器拓扑相比,使用快速锁定拓扑对相噪和杂散有何影响?(在传统环路滤波器拓扑中的C1、C2、C3、R1、R2

2018-08-14 07:08:36

ADF4351输出,相噪远不及器件参考值理想。而且在离中心频率最近处的杂散出现在偏离中心频率5KHz的地方。从频谱来分析,我估计如果能减小或者消除该杂散,则相噪应该可以明显变好。电源我采用了两颗

2018-09-29 15:40:47

ADF4355,采用100MHz OCXO作为参考,输出2280MHz,鉴相频率100MHz,近端出现70Hz左右(及其倍数)的杂散,抑制度在47dBc左右,CP电流设置0.3mA,调整Bleed

2018-08-22 10:40:08

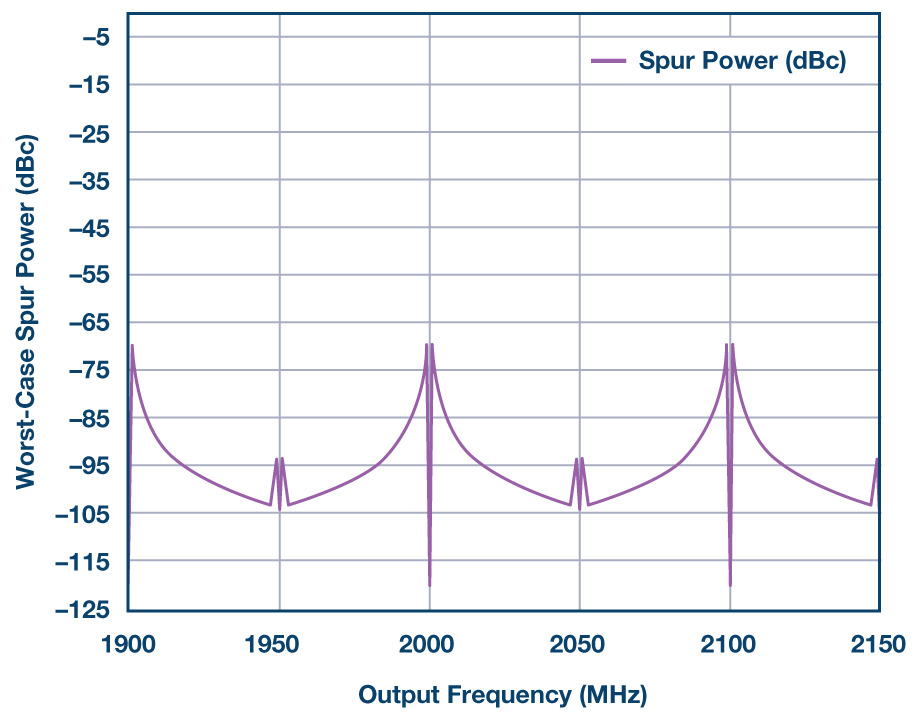

的?举例说明:鉴相频率50M,输出频率5015M,这个时候在5000M和5030M观察到杂散,约为-75dBc,同时输出信号的参考杂散也较强,约为-82dBc,请问有什么解决办法么?@

2019-02-15 13:26:51

)分频器、预分频器与计数器两大类,覆盖的频率范围都包含我需要的2GHz,我想知道,(1)和(2)这两类分频器有什么不同吗?是否是输入信号格式要求不同?第(1)的手册中没有提到相噪,是否(1)比(2)的相噪

2019-01-11 13:39:43

大家好,如下图所示,输出的1GHz信号近端有小数分频杂散,后发现有的频点没有,有的频点会更多,小数分频的分子分母是计算出来可以正好输出1GHz整数频率;

相关配置:环路滤波器是用的参考设计中

2024-11-11 06:05:42

使用HMC733和HMC702和分频器HMC492产生16GHz的信号,参考频率 120MHz,鉴相频率60MHz。我计算环路参数的时候需要将Kv除以2吗?因为VCO输出的频率经过功分和分频之后返回到HMC702的VCOIN端。

2018-08-19 07:18:43

P=8/9,B=12,A=2。外部电感为16nH。配置完毕后,锁定指示灯亮,但是输出中心频率附近有鉴相频率的杂散(即周围隔5M出现一个寄生信号),且测试调谐电压Vtune超过最大的2.5V。换过

2018-12-04 09:38:16

Hello! 请教个关于鉴相频率杂散与环路滤波器布线的问题。例如ADF4360,鉴相频率的杂散抑制的典型值为-70dBc左右,而实测为-60~-65dBc,也能接受,只是感觉各次倍频的鉴相频率太多

2018-11-07 09:03:01

。是否只用关心VCO工作频率范围(3.4-6.8G),不用关心输出分频器。A:跟温度无关,跟输出分频器也无关。附件AN-xxx_ADF4355-2_Bypass_VCO_Calibration_Rev _PrB.pdf109.2 KB

2019-01-16 07:30:47

倍频从而恶化相噪,难以满足系统要求DDS与PLL环外混频的方式由于输出信号的带宽和杂散主要取决于DDS而难以满足系统要求,而DDS内插PLL作为分频器的方式得到的信号杂散较低,频率分辨率小且能做到较宽

2019-06-21 06:32:34

定阻型功率分频器的设计与制作(三)-二阶功率分频器

2009-12-02 15:48:19 88

88 分频器设计与制作 (电子书):分频器的基本原理,分频器设计,分频频率和截止带衰减率的选择与使用,元件的选配及要求等内容,电感线圈的设计与制作。

2010-03-29 10:53:02 722

722

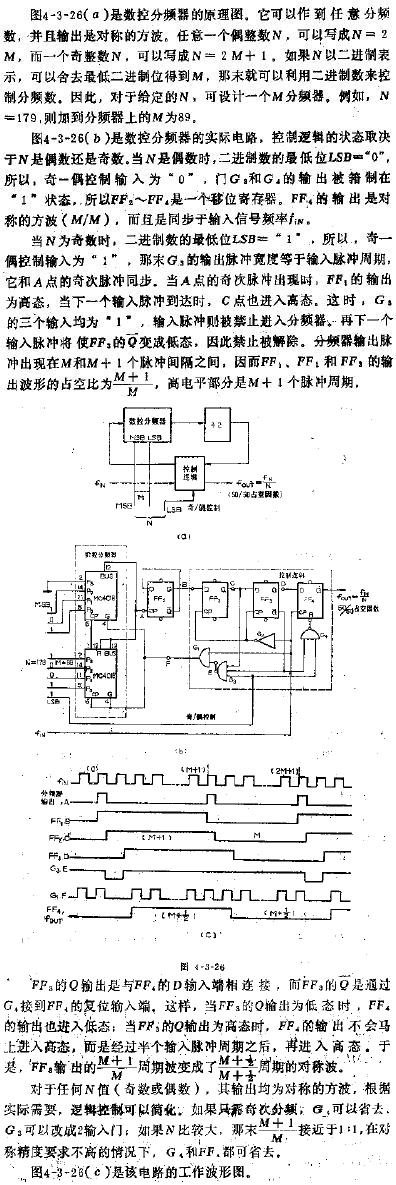

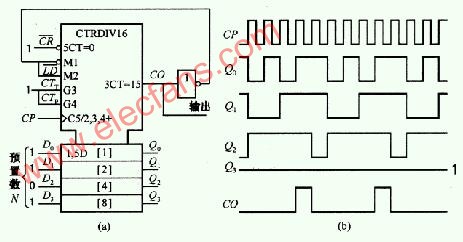

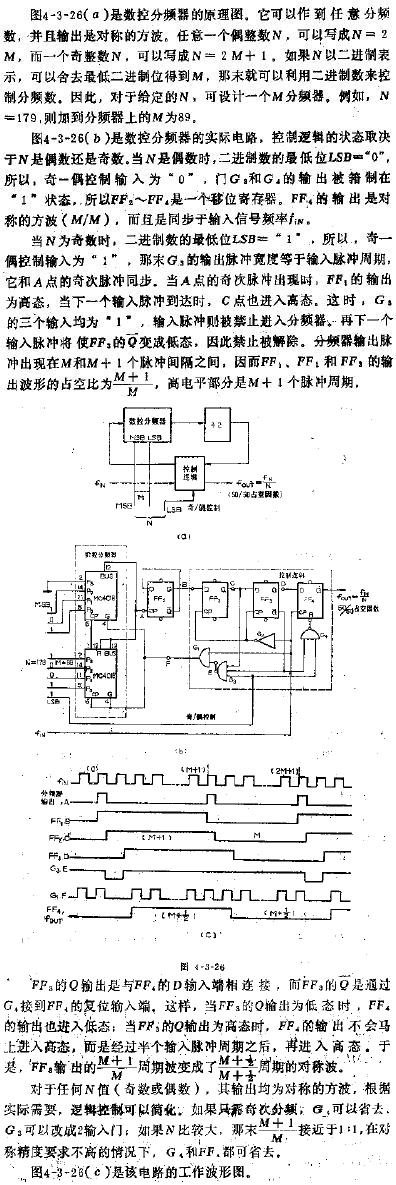

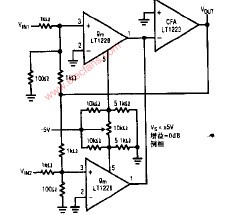

分频系数可变的分频器

2009-04-11 10:18:26 1553

1553

具有奇次和偶次分频的分频器

2009-04-11 10:22:12 1141

1141

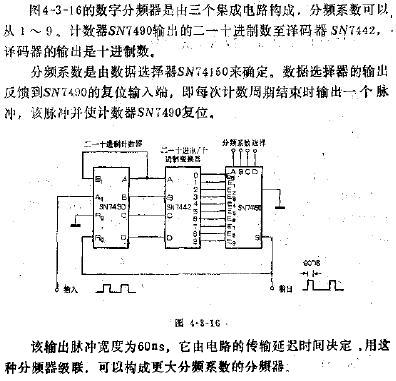

数控分频器

2009-04-11 10:25:27 1507

1507

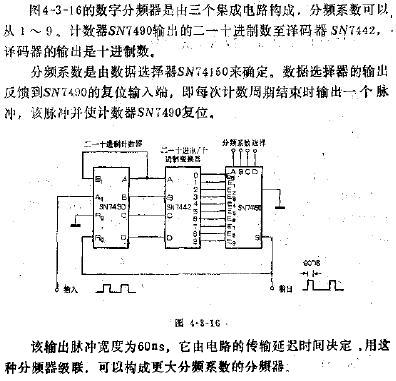

数字分频器

2009-04-11 10:26:21 3464

3464

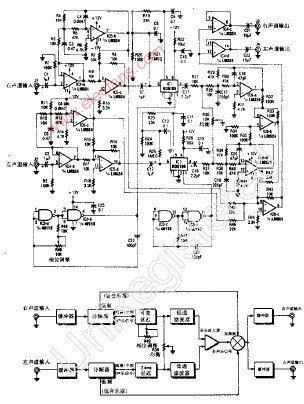

声乐分频器

2009-10-07 11:54:17 928

928

声乐分频器(续)

2009-10-07 11:55:27 664

664

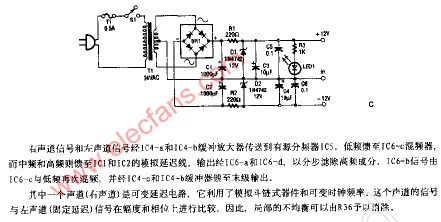

视频分频器

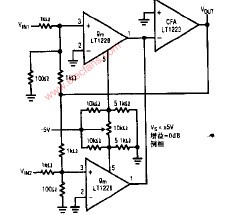

在电流反馈

2009-10-10 15:37:17 1291

1291

可编程分频器电路

可编程分频器:计数器可以对计数脉冲分频,改变计数器的模便可以改变分频比。根据这个原理,可以用集成计数

2010-01-12 13:58:07 3927

3927

什么是分频器 分频器介绍

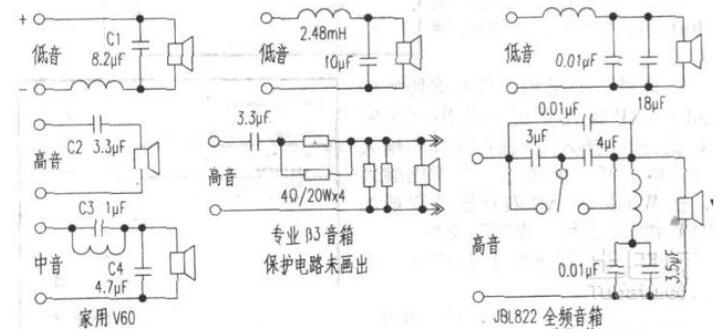

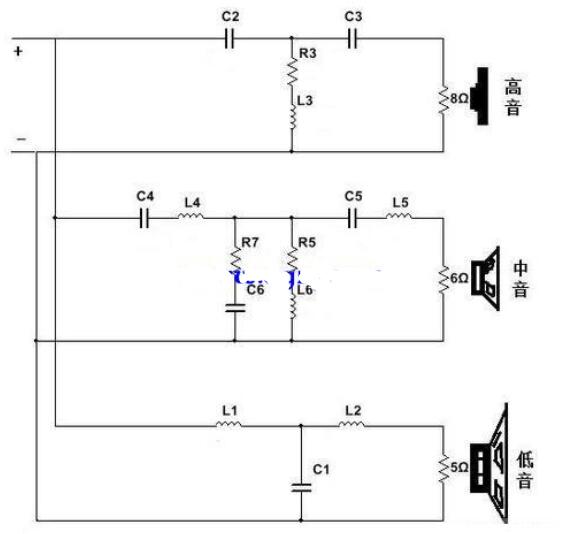

分频器是指将不同频段的声音信号区分开来,分别给于放大,然后送到相应频段的扬声器中再进行重放

2010-02-05 17:51:10 5001

5001 针对频率源的相噪会恶化采样数据的信噪比,杂散会降低接收机灵敏度,提出了一种低相噪低杂散的设计方法。该方法利用Hittite公司的新推出的集成VCO的锁相环芯片HMC830进行设计,供电

2011-10-25 17:29:13 188

188 介绍了一种基于FPGA的双模前置小数分频器的分频原理及电路设计,并用VHDL编程实现分频器的仿真.

2011-11-29 16:43:06 48

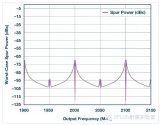

48 LMX2531 系列产品被广泛应用于无线通讯基站系统,相比较整数分频,采用小数分频可以获得更好的相位噪声性能,但是小数分频会导致杂散问题,特别是整数边界杂散尤为突出。本文介绍一种在尽可能保证相位噪声性能的基础上,改善整数边界杂散达10dB。

2013-04-27 15:51:04 3492

3492 v分析、优化和消除带VCO的锁相环在高达13.6 GHz处的整数边界杂散

2016-01-07 14:50:35 0

0 音响分频器原理,感兴趣的可以看看。

2016-09-27 15:19:03 15

15 低杂散锁相环中鉴频鉴相器与电荷泵的设计_李森

2017-01-07 22:14:03 3

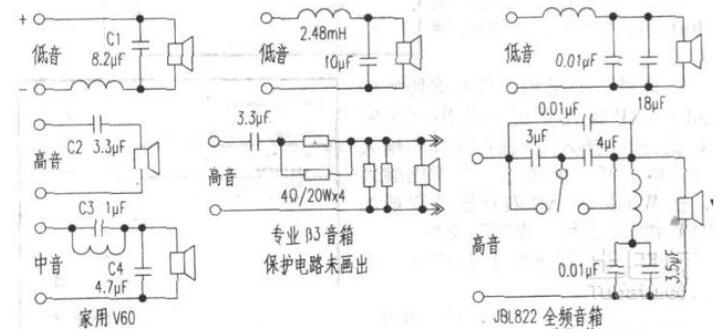

3 分频器一般常用于拥有高音和低音的单元,或者带有中音单元的音箱中,若缺少分频器这种拥有多单元的音箱就不能将不同频段的声音进行回放。而且分频器的种类以及质量的差异,也同时影响到音箱能否回放出更好的声音表现。

2017-11-24 14:16:18 18707

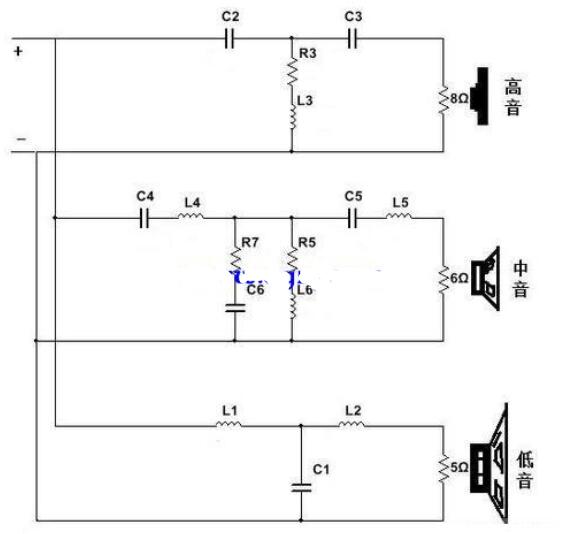

18707 分频器分为主动式、被动式、脉冲分频器三种。主动式电子分音器的原理就是要把适当频率讯号传给适当的单体,被动式分音器“功能、用途”是介于扩大器与喇叭之间,由于单一喇叭无法达到“全频段响应”,脉冲分频器利用汉稳态电路的计数功能实现分频的电路,又称为数字分频器。

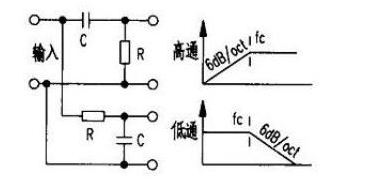

2018-01-10 15:36:20 15986

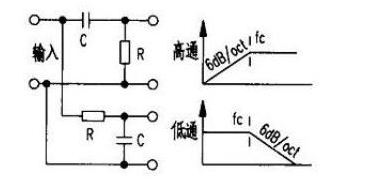

15986 音箱分频器可以将声音信号分成若干个频段。如二分频器就是由一个高通滤波器和一个低通滤波器组成。三分频则又增加了一个带通滤波器。分频器是音箱中的“大脑”,对音质的好坏至关重要。可以看出,分频器充分利用的电容器和线圈的特性达到分频。

2018-02-06 10:54:03 17853

17853 本文首先介绍了音箱分频器概念,其次介绍了音箱分频器结构与作用,最后介绍了_音箱分频器制作方法与图解。

2018-04-13 08:50:18 196012

196012 本文开始介绍了音箱分频器原理,其次介绍了音箱分频器分类与特点以及音箱分频器电路及作用,最后介绍了音箱分频器接线方法图解。

2018-04-13 09:32:27 121473

121473 本文首先介绍了为什么要使用电子分频器,其次阐述了电子分频器工作原理及作用、特点,最后介绍了电子分频器的调整方法、使用注意事项及发展趋势。

2018-05-24 14:46:53 28408

28408 本文首先介绍了什么是分频器,其次阐述了音箱箱体及音箱分频器结构和原理,最后介绍了音箱分频器特点和作用。

2018-05-25 17:47:16 15575

15575

本文首先介绍了分频器的分类及电子分频器的工作原理,其次介绍了主动分频器的优缺点,最后介绍了被动分频器的优缺点,具体的跟随小编一起来了解一下。

2018-05-28 14:52:31 53340

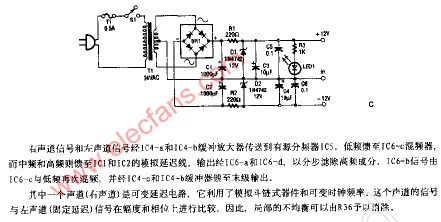

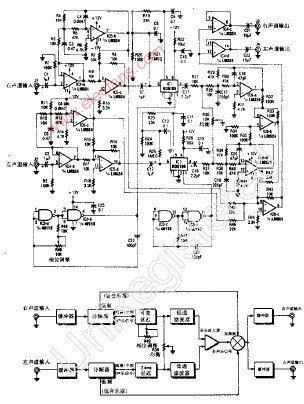

53340 采用有源分频器可以降低对功放带宽的要求;省去了大功率的LC元件;分频点也易于调整,且可以获得比功率分频更佳的效果。这里介绍两种有源二分频器电路。如图9-4所示为有源二分频器组成的功放电路

2018-08-10 16:19:37 25920

25920

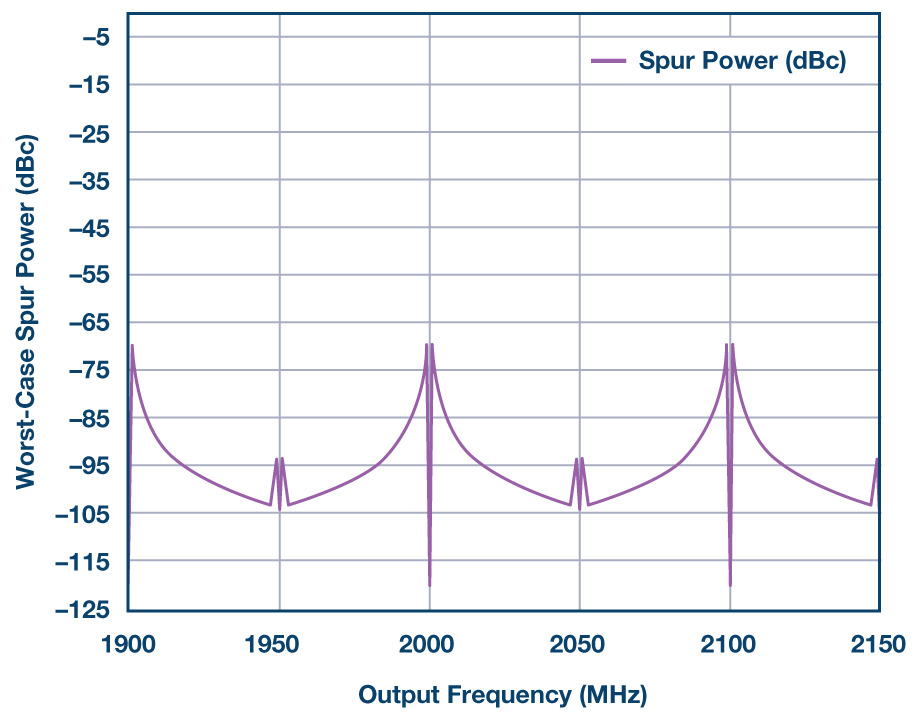

锁相环 (PLL) 和压控振荡器 (VCO) 输出特定频率的RF信号,理想情况下此信号应当是输出中的唯一信号。但事实上,输出中存在干扰杂散信号和相位噪声。本文讨论最麻烦的杂散信号之一——整数边界杂散——的仿真与消除。

2019-04-12 08:32:00 13125

13125

音箱分频器可以将声音信号分成若干个频段。如二分频器就是由一个高通滤波器和一个低通滤波器组成。三分频则又增加了一个带通滤波器。分频器是音箱中的“大脑”,对音质的好坏至关重要。

2019-10-08 10:11:32 9989

9989 本文主要阐述看音箱分频器的维修方法及音箱分频器接喇叭的方法。

2020-03-28 11:09:59 19022

19022

现在很多集成VCO的频率合成器的设计思想,都是利用输出端加分频器来扩展输出范围,如图1所示。比如ADI的HMC832,其VCO的频率为1500~3000MHz,利用其后的分频器(1/2/4/6/…60/62),最终获得25MHz~3000MHz的频率覆盖范围。

2020-10-30 10:40:00 3

3 锁相环 (PLL) 和压控振荡器 (VCO) 输出特定频率的RF信号,理想情况下此信号应当是输出中的唯一信号。但事实上,输出中存在干扰杂散信号和相位噪声。本文讨论最麻烦的杂散信号之一——整数边界杂散——的仿真与消除。

2020-09-09 10:09:56 4998

4998

AD9508:1.65 GHz时钟扇出缓冲器,集成输出分频器和延迟调整

2021-03-21 15:45:30 2

2 音响中分频器和功放有两种连接方式。一种是电子分频器(有源分频),既前级出来后进入分频器,然后单声道分双路或者三路分别送往各功放输出给音箱,对于立体声而言,单声道功放最少也是四台,甚至6台。

2021-05-01 17:55:00 30785

30785

图1所示电路使用带集成式VCO和外部PLL的ADF4350频率合成器,通过隔离PLL频率合成器电路与VCO电路将杂散输出降至最低。集成PLL和VCO的器件可从数字PLL电路馈通至VCO,由于PLL

2021-05-28 17:50:57 7

7 锁相环(PLL)和压控振荡器(VCO)以特定频率输出RF信号,理想情况下,该信号将是输出端存在的唯一信号。实际上,输出端存在不需要的杂散信号和相位噪声。本文讨论如何仿真和消除一种更麻烦的杂散信号——整数边界杂散。

2023-01-08 15:40:42 3309

3309

假设某个调制方案指出整数边界杂散功率高于–80 dBc的通道不可用;那么图10中大约1%的通道不再可用。为了克服这个问题,ADIsimFrequencyPlanner可以优化PLL/VCO配置,以减少并在大多数情况下消除整数边界杂散。

2023-02-01 11:54:50 3036

3036

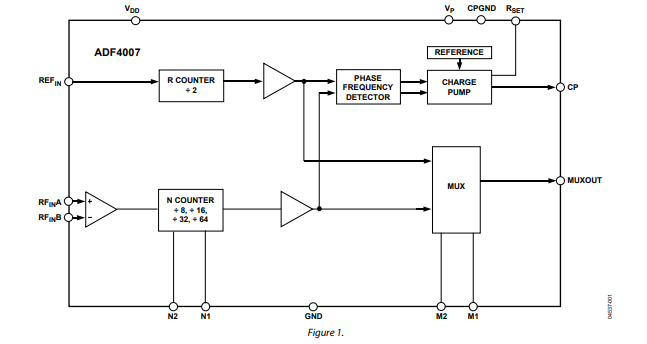

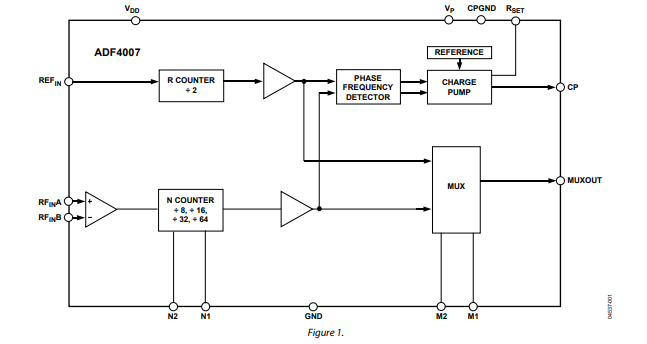

ADF4007是一款高频分频器/PLL频率合成器,可用于各种通信应用。RF端工作频率可达7.5 GHz,PFD端工作频率可达120 MHz。它由低噪声数字鉴频鉴相器(PFD)、精密电荷泵和分频器

2023-02-24 17:39:54 1921

1921 所谓“分频”,就是把输入信号的频率变成成倍数地低于输入频率的输出信号。数字电路中的分频器主要是分为两种:整数分频和小数分频。其中整数分频又分为偶分频和奇分频,首先从偶分频开始吧,入门先从简单的开始!

2023-03-23 15:06:22 3014

3014

电子发烧友网站提供《基于HMC830的低相噪低杂散频率源的设计.pdf》资料免费下载

2023-10-25 14:20:38 7

7 分频器设计 一:分频器概念 板载时钟往往 是 有限个( 50MHZ/100MHZ/24MHZ/60MHZ… ),如果在设计中需要其他时钟时,板载时钟不满足时,需要对板载时钟进行分频 / 倍频,目的

2023-11-03 15:55:02 3266

3266

分频器是一种电子设备,用于将输入信号分成不同频率的输出信号。其主要作用是将原始输入信号分离成多个频率范围内的信号,以供不同的电路进行处理。分频器广泛应用于通信、测量和音频系统中。 分频器的主要

2024-02-01 11:19:51 6197

6197 说到射频的难点不得不提杂散,杂散也是射频被称为“玄学”的来源。杂散也是学习射频必经的一个难点。本篇文章就来讲一下杂散。

2024-11-05 09:59:34 6929

6929

ADF4007是一款高频分频器/PLL频率合成器,可用于各种通信应用。RF端工作频率可达7.5 GHz,PFD端工作频率可达120 MHz。它由低噪声数字鉴频鉴相器(PFD)、精密电荷泵和分频器

2025-04-27 15:23:56 883

883

电子发烧友网为你提供()无杂散、50 MHz 至 2.1 GHz 单通道小数 N 分频频率合成器相关产品参数、数据手册,更有无杂散、50 MHz 至 2.1 GHz 单通道小数 N 分频频率合成器

2025-05-23 18:30:22

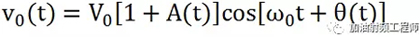

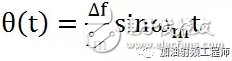

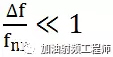

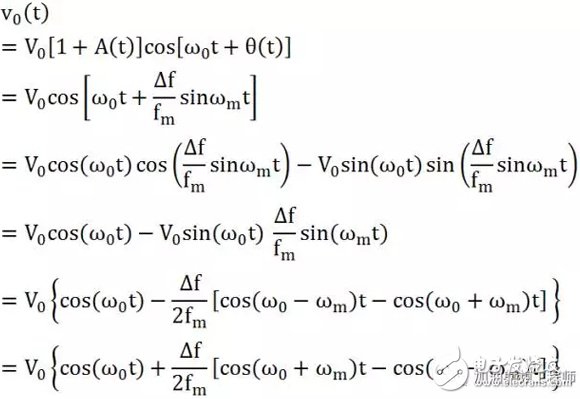

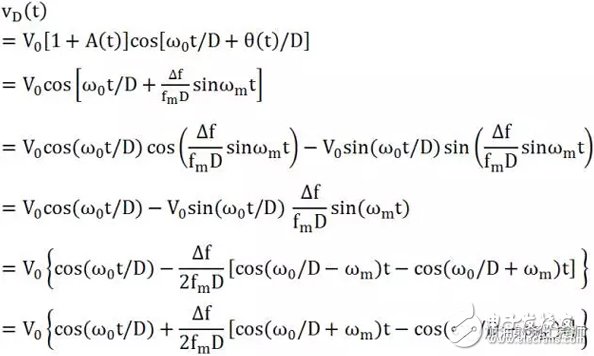

,则:

,则:

电子发烧友App

电子发烧友App

评论