摘要

相位噪声是时钟、射频频综最为关注的技术指标之一。影响锁相环相噪的因素有很多,比如电源、参考源相噪、VCO 自身的相噪、环路滤波器的设置等。其中,电源引入的低频噪声往往对锁相环的近端相噪有着很大的影响。对于高性能的时钟和射频频综产品,为了获得极低的相噪性能,往往采用低噪声的LDO 供电。然而,采用不同的LDO 给频综供电,取得的相噪性能往往会有很大差别,同时,LDO 外围电路设计也会影响到频综的相噪性能。

本文首先简要地介绍了LDO 的噪声来源及环路稳定性对输出噪声的影响;其次,根据调频理论推导出VCO 的相位噪声与LDO 的噪声频谱密度的理论计算关系。在此基础上,为了验证LDO 噪声对射频频综输出相噪的影响,分别采用TPS7A8101 和TPS74401 LDO 评估板给TRF3765 射频频综评估板供电,对比测试这两种情况下的TRF3765 相噪曲线;同时,为了验证LDO 环路稳定性对频综相噪的影响,针对TPS7A8101 评估板的参考电路做出部分修改,并对比测试了电路修改前后的TRF3765 输出相噪。

1、LDO 噪声来源及环路稳定性对输出噪声影响

1.1 LDO 噪声来源

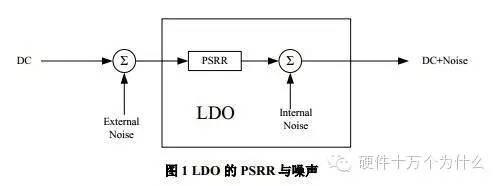

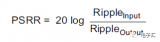

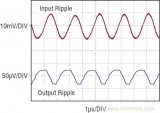

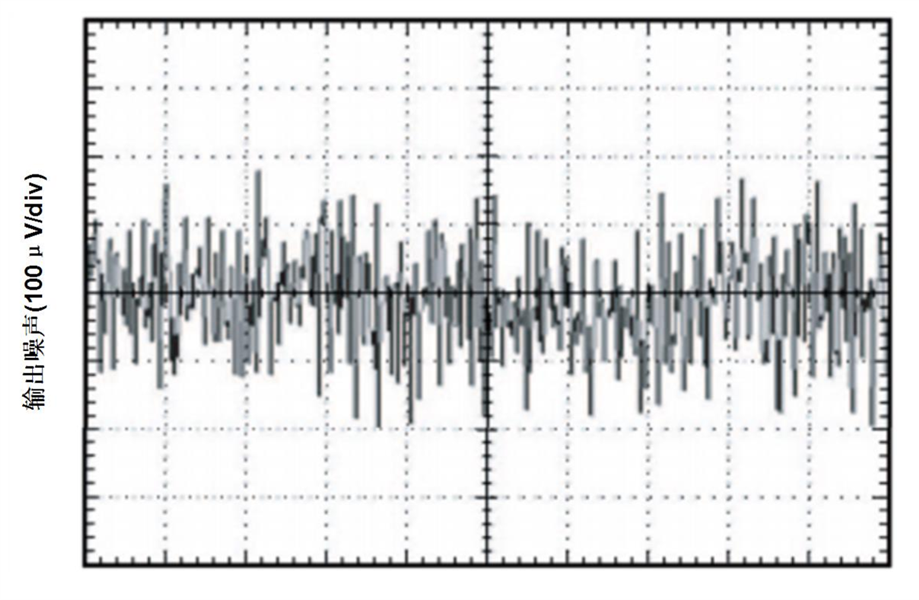

LDO 的噪声分为LDO 内部的噪声和LDO 外部的噪声。LDO 内部的噪声来自于内部电路的带隙基准源,放大器以及晶体管。LDO 外部的噪声来自于输入。在LDO 的手册中,PSRR 是表征LDO抑制外部噪声的能力,但PSRR 高并不代表LDO 内部噪声小。LDO 的总输出噪声才是表征LDO内部噪声抑制的参数,一般在电气特性表里用单位µVRMS 表示,或者在噪声频谱密度图上表示。

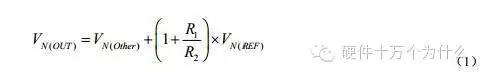

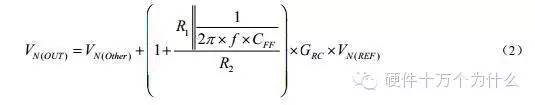

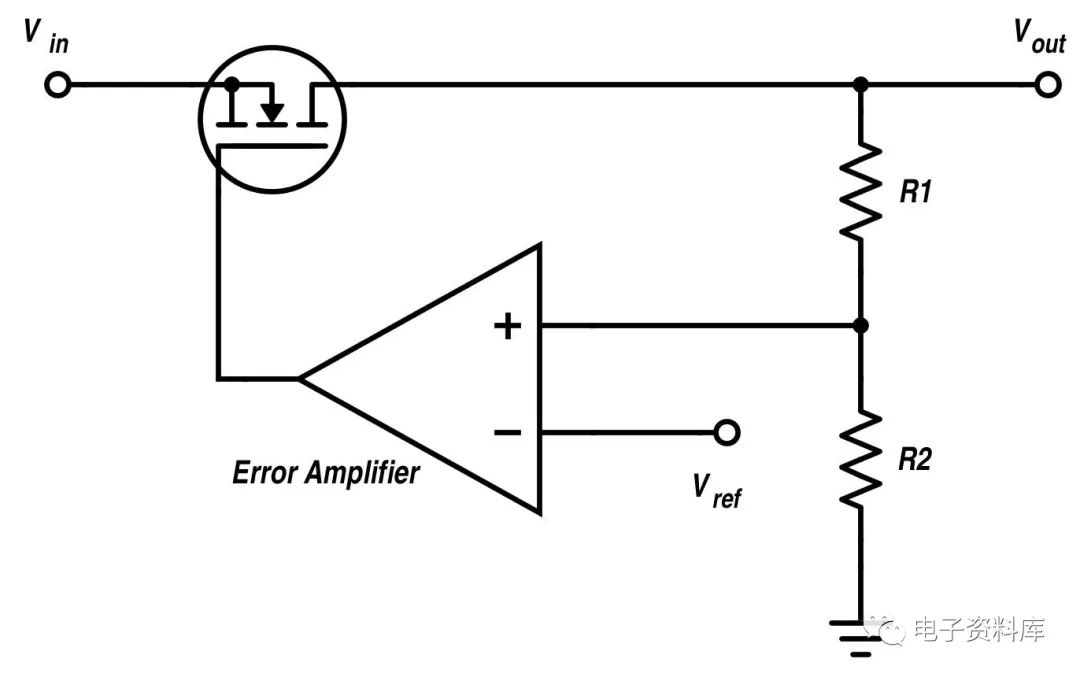

图2 是LDO 内部结构框图,VN 代表等效噪声源。噪声源包括带隙基准源产生的噪声VN (REF) ,误差放大器产生的噪声VN (AMP) ,FET 产生的噪声VN (FET) 以及反馈电阻产生的噪声VN ( R1) 和VN ( R2) 。在大多数情况下,由于带隙基准源电路是由很多不同的电阻、晶体管和电容组成,它所产生的噪声会远远大于反馈电阻产生的噪声。而且带隙基准源是误差放大器的输入,它所产生的噪声也会经由误差放大器放大来控制FET,所以误差放大器本身以及FET 所产生的噪声也会比带隙基准源的噪声要低。可以说,LDO 内部最大的噪声源就是带隙基准源。我们把LDO 输出噪声VN (OUT) 表示为

VN ( Other) 是VN ( AMP) 以及VN (FET) 的和。由公式1 可以得出,输出噪声最小值出现在R1 短接到FB,误差放大器的增益近似为1 的时候。

1.2 LDO 噪声抑制方法

为了抑制带隙基准源产生的噪声,有三种办法。

一是降低误差放大器的带宽,抑制了带隙基准源的高频噪声。但是降低带宽会使LDO 的动态性能降低。

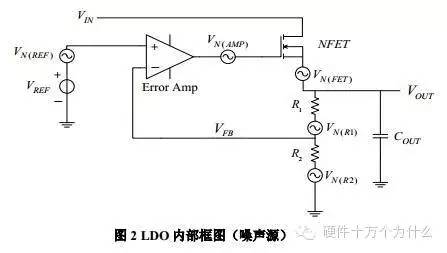

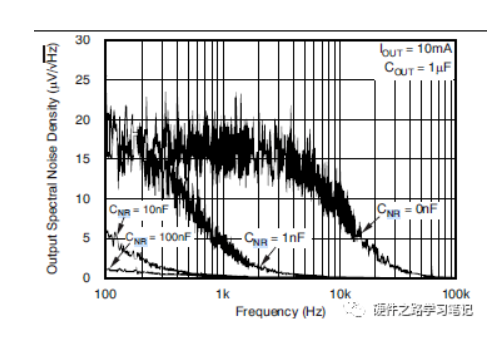

二是在带隙基准源和误差放大器之间加低通滤波。高性能的LDO 都会有一个噪声抑制NR 管脚,CNR 并联在带隙基准源和GND 之间,起到低通滤波的作用。如图3 所示。

三是在反馈电阻R1 上增加前馈电容CFF 。在增加了CFF 和CNR 后,输出噪声可以表示为

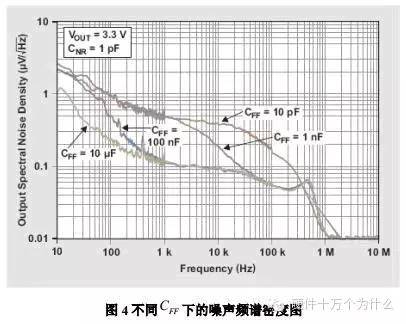

从式2 可以得出,CFF 越大,输出噪声就越小。频率越高,输出噪声越小。

图4 是不同CFF 下的噪声频谱密度图。可以看出,CFF 越大,噪声从低频开始都能被很好的抑制。CFF 太小的时候,抑制噪声的作用就不太明显。当频率很高的时候,不管用多大的CFF ,噪声频谱密度相差不会太大。所以,增加合适的前馈电容CFF ,对改善LDO 低频噪声有非常好的效果。

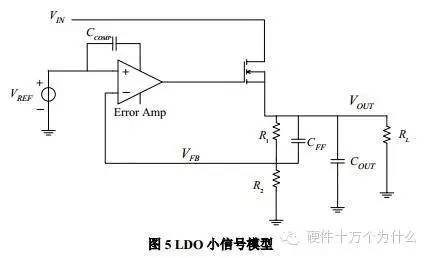

1.3 LDO 环路稳定性与输出噪声的关系

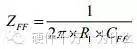

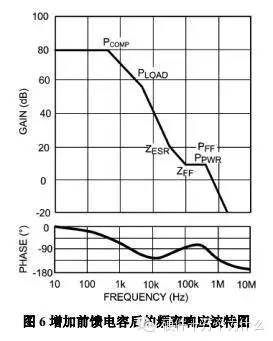

从LDO 的小信号分析可以看出,LDO 有两个低频极点,如果没有合适的零点补偿,LDO 的稳定裕度不够,就有可能产生震荡。稳定裕度不够的LDO 产生的内部噪声会更大。上节中提到第三种噪声抑制方法,即增加前馈电容CFF 是实际上为了改善系统稳定裕度。由CFF 与R1组成一个低频零点, 。

。

由下图的频率响应可以看出,零点是相位裕度有了很大的提升,增加了系统稳定性,从而减小了系统低频噪声。

2、LDO 噪声与VCO 输出相噪的关系

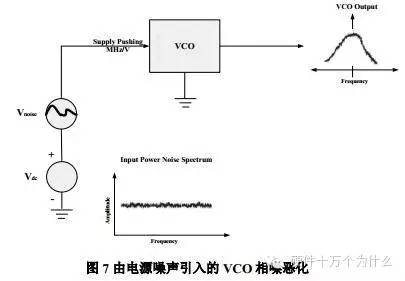

电源引入噪声对锁相环中各个有源器件都可能造成影响,其中最为敏感的部分是VCO,本文将着重讨论LDO 输出噪声对VCO 相噪的影响。

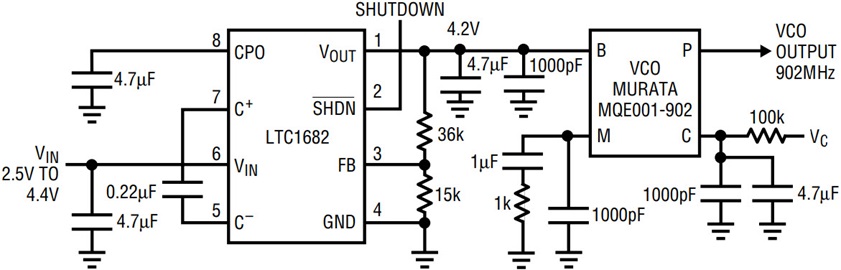

一个典型的LDO 供电的频综系统框图如图7 所示:加载在电源上的噪声信号通过频率调制过程调制到VCO 的输出,造成VCO 输出相噪恶化。

根据经典调频系统理论,调制指数β由式(3)来表示

对于电源噪声调制,式中的频率背离(Frequency Deviation)可由下式得到

式中,Kpush 是VCO 的电源推压指数,它表征的是VCO 对电源噪声波动的灵敏度,单位用MHz/V 来表示;A 是电源噪声信号幅度。

对于采用LDO 供电的射频频综来说,通常用LDO 的指定频率偏移的频谱噪声密度Sldo(f)(Noise Spectrum Density)来表征电源噪声,由于它是一个RMS 电压值,所以式(4)可以表示为

将式(5)带入式(3),可以得到

式中,f 是相应的频率偏移。

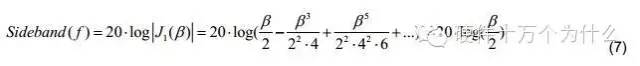

由不同频率成分噪声调制到载波输出引起的单边带噪声,由下式表示

将式(6)带入式(7)有

由式(8)可见,对于给定的VCO,由于Kpush 是一个确定的值,因此由LDO 噪声引起的VCO 输出相噪是由LDO 的噪声频谱密度(Noise Spectrum Density)决定的。

3、采用不同LDO 进行射频频综供电对比测试

3.1 TPS7A8101/TPS74401 频综供电对比测试

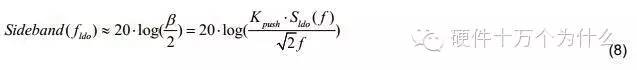

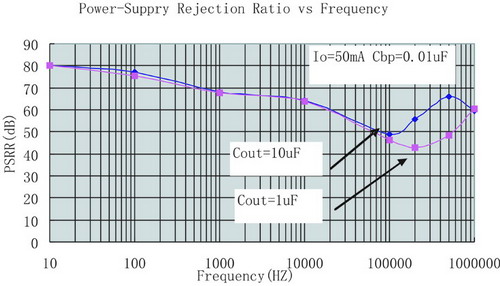

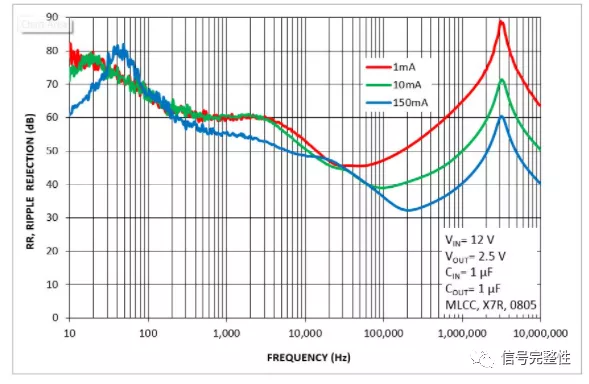

TPS7A8101 和TPS74401 是TI 推出的两款高性能LDO 芯片。与TPS74401 相比, 由于具有更高的环路增益和带宽,TPS7A8101 具有更高的电源噪声抑制比(PSRR);然而,由于具有更好的系统稳定性,TPS74401 拥有更低的噪声频谱密度(NSD),如下图8 所示。

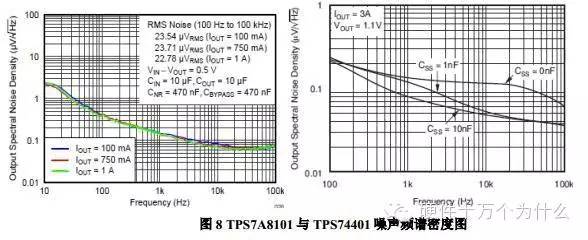

下面我们分别采用TPS7A78101 和TPS74401 评估板对TRF3765 评估板进行供电,比较两者的输出相噪。测试设置如下图9 所示,LDO 的输入5V 电源由Agilent E3634 提供,通过LDO 评估板后转变成3.3V 给TRF3765 供电。TRF3765 采用评估板上自带的61.44MHZ 晶振作为参考输入,输出频率为2.28GHz。TRF3765 的射频输出连到R&S FSQ8 相噪分析仪上测试相应的相噪曲线。

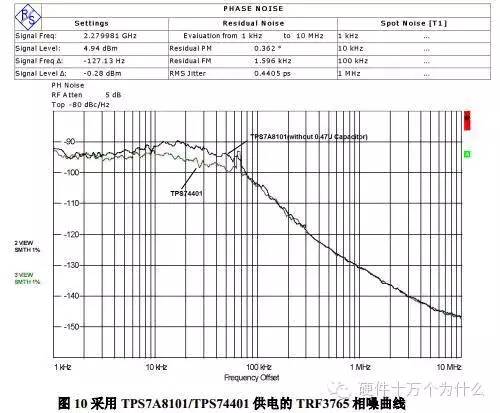

两者对比测试结果如下图10 所示,

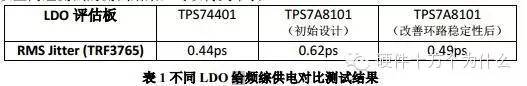

由上图看见,采用TPS7A8101 供电,TRF3765 在整个积分区间内(1KHz~10MHz)的RMS 抖动为0.62ps;而TPS74401 的RMS 抖动仅为0.44ps。

3.2 TPS7A8101 输出电路优化及其对频综相噪的影响

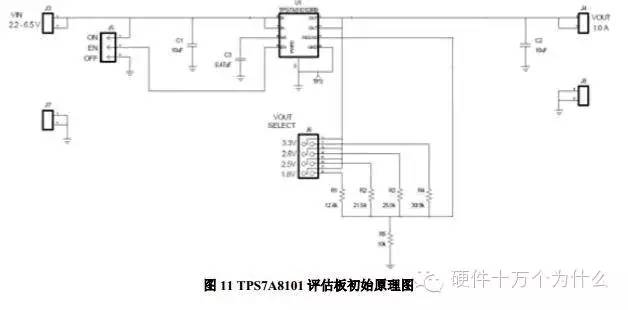

TPS7A8101 评估板初始原理图如图11 所示,由上节的测试结果可知,采用该电路给TRF3765供电,RMS 抖动为0.62ps。

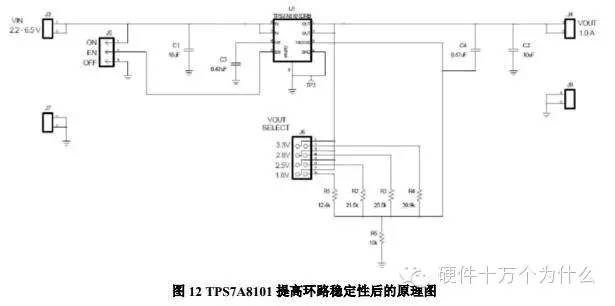

第一章中我们已经讨论了LDO 加一个前馈电容可以有效的提高电源的环路稳定性,从而降低LDO 的输出噪声频谱密度。基于此,我们在TPS7A8101 输出加一个0.47 µF 的前馈电容,修改后的原理图如下图12 所示。

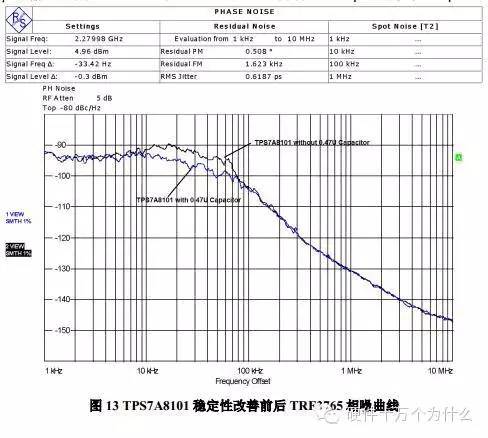

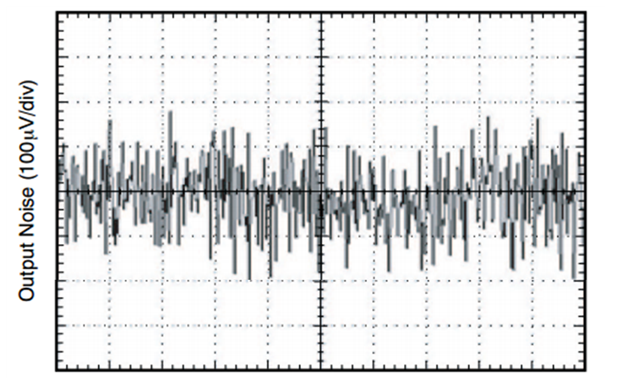

针对修改前后的设计,我们对比测试了相应的TRF3765 相噪曲线,如图13 所示,由图可见,增加0.47 µF 输出电容后,1KHz 到10MHz 的RMS 抖动由0.62ps 提高到0.49ps。

4 结论

综合以上两组测试的测试结果,可以得到下表

由表1 可以看到,由于TPS74401 的噪声频谱密度最小,在给频综供电的时候可以取得最好的相噪性能;TPS7A8101 噪声频谱密度相对较大,在给频综供电的时候取得的相噪性能相对较差;但是通过优化TPS7A8101 的输出电路设计,频综的相位噪声得到了明显的改善。

实测结果很好的验证了前文的理论分析,即:LDO 的噪声频谱密度参数(NSD)决定了由电源噪声引起的VCO 相噪恶化;通过提高LDO 的环路稳定性可以达到降低噪声频谱密度的目的,从而改善频综的输出相噪。

审核编辑:汤梓红

电子发烧友App

电子发烧友App

评论