事实上,它是由常用的电路结构所决定的,低电平时电路往往有较高电平时更低的环路阻抗,而低阻抗则意味着抗干扰能力更强。结合实际讲一个有用的例子来加深印象:

我们有的同学可能已经学习了这样的一条PCB布线规则-----在条件许可的情况下,高电平有效线要尽量缩短,低电平有效的线则尽量延长----这一条规则的存在基础就是基于低电平时环路阻抗比较低,抗干扰能力比较强才起来的。

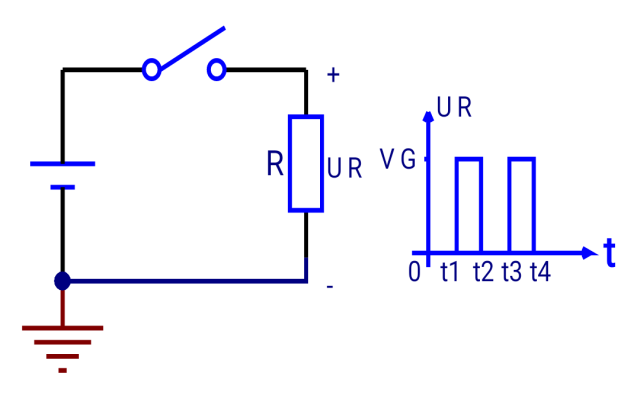

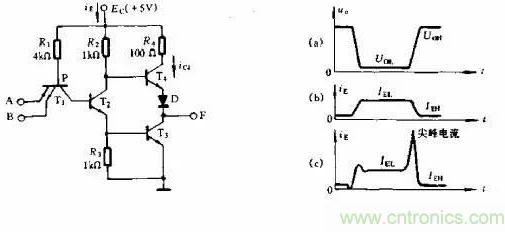

如OC或OD电路要控制一个电平就是通过它这个开关的通断来实现的。有在上拉电阻的情况下,开关接通,得低电平;开关切断,得高电平。这样,为了防止电路失控的情况下仍然是有效电平,那么当然是低电平有效才更“保险”了。结构上,象OC电路那样,由于集电极更难击穿,所以,也更不容易损坏。

对于其它图腾柱输出的电路,虽然0和1都有同样的风险,但应用中还是有人愿意加一个上拉电阻,以取得类似OC或OD输出的效果。至于为什么不采用下拉电阻而用上拉电阻,大家也可以分析一下。

另一个方面是OC或OD输出的电路,使用上拉电阻后具有节能的效果。因为关断后它是具有获得高电平时的电流几乎为0。

解密:数字电路为什么是低电平有效的多?

- 数字电路(83193)

相关推荐

热点推荐

数字电路之时序电路

在《数字电路之如雷贯耳的“逻辑电路”》、《数字电路之数字集成电路IC》之后,本文是数字电路入门3,将带来「时序电路」的讲解,及其核心部件触发器的工作原理。什么是时序电路?

2016-08-01 10:58:48 19579

19579

19579

19579

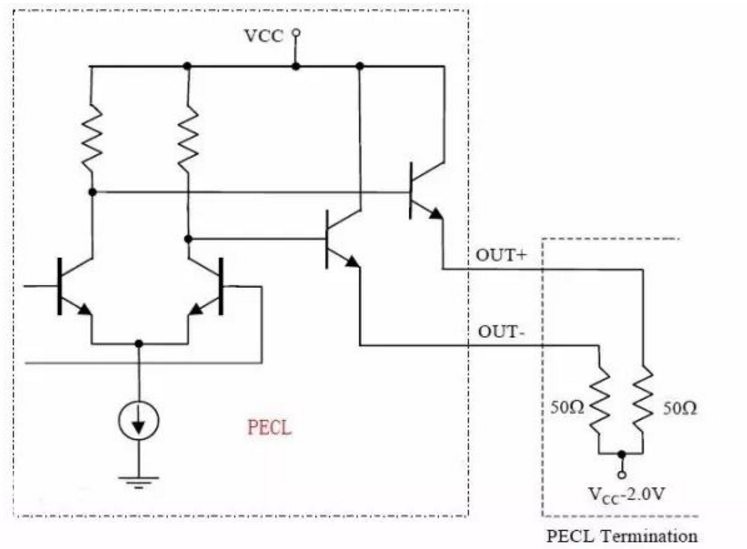

数字电路电平标准与接口设计解析

在高速电路中如何实现高速驱动输出呢?要么增大驱动电流,要么降低电平标准,或者提高晶体管工作速度。显然前者会带来非常大的功耗,因此改变电平标准和改进晶体管设计成为选择,虽然低电平更容易受到干扰,所以需要更严格的硬件设计。

2017-12-17 07:38:50 14138

14138

14138

14138

数字电路的基础知识

用数字信号完成对数字量进行逻辑运算和算术运算的电路称为数字电路。 由于它具有逻辑运算和逻辑处理功能,所以又称为数字逻辑电路。 现代的数字电路由半导体工艺制成的数字集成器件构造而成。 逻辑门是数字电路的基本单元电路,就如同在模拟电路中基本放大电路是模拟电路的基本单元电路。

2023-02-23 14:18:32 27671

27671

27671

27671

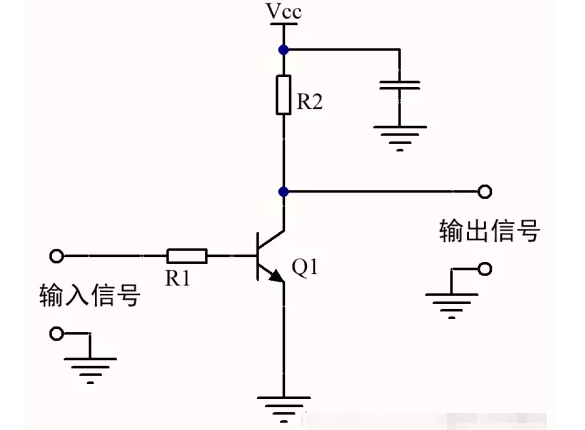

三极管电平转换电路设计

在数字电路的领域,常常把电压简化为电平,来描述逻辑状态。比如TTL电平信号规定,+5V等价于逻辑“1”,也称为高电平,0V等价于逻辑“0”,也就是低电平。数字电路里,只有0和1两个状态。其实从0V

2023-04-20 14:35:09 4848

4848

4848

4848

高电平和低电平是什么意思?区别是什么?

高电平和低电平是数字电路中经常会出现的专业名词,它们所表面的意思就是电路上有和无,两者之间没有中间值,在不同的电路上,电压的具体值也是各不相同的。如果用简单的语言表达它们的意思就是开和关,平时

2023-05-26 10:17:30 67552

67552

67552

67552

数字电路是什么

电源电压的高电平和低电平来分别表示0和1,从而实现信息的表达。 不同于生活中使用的数字0123456789,在电子硬件中最常使用的是2进制和16进制,而数字电路中采用的就是二进制。 二进制中一个字节(byte)通常由8个数据位(binary digit)组成,

2023-11-06 17:25:57 3543

3543

3543

3543

低电平和高电平的区分方法

高电平低电平主要应用于数字电路。体现在电路上就是只有‘有’和‘无’,没有中间值,这个有在不同电路上的电压值不相同。如果是5V供电的数字电路,高电平就是5V,或接近5V。低电平就是‘无’,就是0V或

2018-08-28 14:59:04

数字电路为什么是低电平有效的多

数字电路为什么是低电平有效的多设计时常常是低电平有效,本文讲解一下内因,大家有兴趣的看看。 事实上,它是由常用的电路结构所决定的,低电平时电路往往有较高电平时更低的环路阻抗,而低阻抗则意味着抗干扰

2016-10-03 09:45:27

数字电路及其应用

|CB样板贴片,麦1斯1艾1姆1科1技全国1首家P|CB样板打板 数字电路工作时通常只有两种状态:高电位(又称高电平)或低电位(又称低电平)。通常把高电位用代码“1”表示,称为逻辑“1”;低电位用

2013-09-05 11:12:39

数字电路及其应用

。 数字电路工作时通常只有两种状态:高电位(又称高电平)或低电位(又称低电平)。通常把高电位用代码“1”表示,称为逻辑“1”;低电位用代码“0”表示,称为逻辑“0”(按正逻辑定义的)。注意:有关产品手册中常

2012-12-03 21:37:43

数字电路及其应用

一连串的脉冲(电压),这就是数字信号。人们把用来传输、控制或变换数字信号的电子电路称为数字电路。 数字电路工作时通常只有两种状态:高电位(又称高电平)或低电位(又称低电平)。通常把高电位用代码“1

2009-04-07 09:39:18

数字电路和模拟电路的隔离探讨

话说,数字电路和模拟电路在同一个电路板上最好要隔离,防止相互干扰,为什么会有干扰呢?小弟不才,就此做一个简单的说明,希望有高手大牛来赐教!简单来说:数字电路是离散量,说白了就只有1和0,也就是高低电平

2013-04-19 19:28:25

数字电路的应用介绍

。 数字电路工作时通常只有两种状态:高电位(又称高电平)或低电位(又称低电平)。通常把高电位用代码“1”表示,称为逻辑“1”;低电位用代码“0”表示,称为逻辑“0”(按正逻辑定义的)。注意:有关

2018-08-28 15:36:27

电平特性数字电路中有哪几种电平

认识单片机在一片集成电路芯片上集成微处理器CPU、存储器、I/O接口电路,从而构成了单芯片微型计算机,即单片机。电平特性数字电路中只有两种电平:高电平和低电平高电平:5V或者3.3V,取决单片机

2021-07-21 07:45:56

NE555触摸电路中人体杂波信号是高电平还是低电平?

NE555电路中,触摸2脚低电平有效有动作,触摸6脚高电平有效有动作,触摸电路中人体杂波信号是高电平还是低电平?

2024-01-10 13:03:22

PWM的输入是高电平有效还是低电平有效的?

请问High-Voltage Motor Control + PFC Kit v2.0的IPM的输入极性,PWM的输入是高电平有效还是低电平有效的?

2020-06-10 11:04:26

为什么单片机有些管脚要设计成低电平有效?

规则-----在条件许可的情况下,高电平有效线要尽量缩短,低电平有效的线则尽量延长----这一条规则的存在基础就是基于低电平时环路阻抗比较低,抗干扰能力比较强才起来的。如OC或OD电路要控制一个电平就是通过它

2011-08-30 09:36:11

为什么单片机有些管脚要设计成低电平有效?

就是通过它这个开关的通断来实现的。有在上拉电阻的情况下,开关接通,得低电平;开关切断,得高电平。这样,为了防止电路失控的情况下仍然是有效电平,那么当然是低电平有效才更“保险”了。结构上,象OC电路那样

2011-11-07 10:21:06

为什么单片机管脚设计成低电平才有效

为什么单片机管脚设计成低电平才有效它是由常用的电路结构所决定的,低电平时电路往往有较高电平时更低的环路阻抗,而低阻抗则意味着抗干扰能力更强。结合实际讲一个有用的例子来加深印象:我们有的同学可能已经

2017-09-18 13:17:18

什么是数字电路

本帖最后由 gk320830 于 2015-3-7 06:25 编辑

数字电路 现代的数字电路由半导体工艺制成的若干数字集成器件构造而成。逻辑门是数字逻辑电路的基本单元。存储器是用来存储二值

2009-04-06 23:45:00

你都知道数字电路有哪几种状态吗

数字电路有三种状态:高电平、低电平、和高阻状态,有些应用场合不希望出现高阻状态,可以通过上拉电阻或下拉电阻的方式使处于稳定状态,具体视设计要求而定上拉就是将不确定的信号通过一个电阻嵌位在高电平

2021-11-03 06:11:45

单片机的管脚为什么要设计成低电平电路呢

规则-----在条件许可的情况下,高电平有效线要尽量缩短,低电平有效的线则尽量延长----这一条规则的存在基础就是基于低电平时环路阻抗比较低,抗干扰能力比较强才起来的。如OC或OD电路要控制一个电平就是通过...

2022-01-14 07:17:56

如何看懂数字电路图?

数字电路是实现一定逻辑功能的电路,称为逻辑电路,又称为开关电路。这种电路中的晶体管一般都工作在开关状态。数字电路可以由分立元件构成(如反相器、自激多谐振荡器等),但现在绝大多数是由集成电路构成(如与门电路

2021-02-25 07:58:41

模拟电路与数字电路的基础知识详解

电子电路是单片机硬件部分的基础知识,电子电路分为模拟电路和数字电路。单片机是使用数字电路,但ADC功能涉及模拟电路。1、模拟电路与数字电路2、欧姆定律3、电源正极和负极4、TTL电平和CMOS电平

2022-01-25 07:15:00

模拟电路和数字电路接地要点

机器毁损!!!主要因为数字电路、模拟电路的工作电平一般为 3.3-15.5V(15.5V一般用于232接口通讯的最高电平);而通常电源回路的电平一般在市电范围(AC220V±10%),远远大于数字电路

2017-08-29 09:45:39

直接输出模式, CMOS 输出低电平有效

看TTP224B手册的时候看到这样一句话。直接输出模式, CMOS 输出低电平有效到底是指低电平时才能有效输出,还是指输出端输出低电平?

2020-10-18 15:39:26

高速数字电路设计

高速数字电路设计

关于高速数字电路的电气特性,设计重点大略可分为三项 : Ø 正时 (Timing) :由于数字电路大多依据时脉信号来做信号间的同

2007-10-16 17:22:57 3406

3406

3406

3406光控报警器电路图解,光控报警电路原理

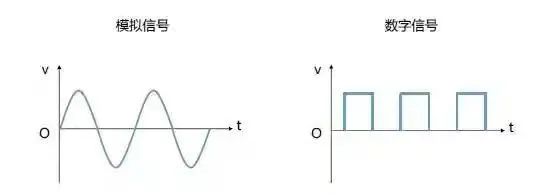

现实中的世界是电子技术的世界——模拟电路+数字电路。模拟电路中行走的是连续的信号,也就是说基于时间为参数的各种函数,而数字电路就干脆多了,就两种状态高电平或低电平(严格来说是三种,还有一种介于高低电平之间,状态未知)。

2017-04-24 09:22:47 18666

18666

18666

18666

低电平和高电平的区别

数字电路中,把电压的高低用逻辑电平来表示。逻辑电平包括高电平和低电平这两种。不同的元器件形成的数字电路,电压对应的逻辑电平也不同。在TTL门电路中,把大于3.5伏的电压规定为逻辑高电平,用数字1表示

2017-11-14 10:37:26 302062

302062

302062

302062

详解TTL和CMOS电平

TTL电平最常用于有关电专业,如:电路、数字电路、微机原理与接口技术、单片机等课程中都有所涉及。在数字电路中只有两种电平(高和低)高电平+5V、低电平0V.同样运用比较广泛的还有CMOS电平、232

2017-11-15 14:34:49 6

6

6

6数字电路该怎么学_数字电路的学习方法(要点、注意事项)

用数字信号完成对数字量进行算术运算和逻辑运算的电路称为数字电路,或数字系统。由于它具有逻辑运算和逻辑处理功能,所以又称数字逻辑电路。现代的数字电路由半导体工艺制成的若干数字集成器件构造而成。逻辑门

2018-03-23 17:27:39 36339

36339

36339

36339什么是模拟电路 什么是数字电路

模拟信号和数字信号的特点不同,处理这两种信号的方法和电路也不同。一般地, 电子电路可分为模拟电路和数字电路两大类。 1. 模拟电路 处理模拟信号的电子电路称为模拟电路。模拟电路研究

2018-10-16 10:25:09 103250

103250

103250

103250简析模拟电路与数字电路

模拟电路与数字电路的关系,有说所有电路都是模拟电路,数字电路只是模拟电路的一部分的;有说模拟电路和数字电路各成系统,井水不犯河水的;有说线性的就是模拟电路,非线性的就是数字电路,不一而足。

2019-07-03 17:35:50 10777

10777

10777

10777逻辑芯片输入的低电平有效和高电平有效

最近在看逻辑电路,刚刚看到编码器,发现二进制编码器是高电平输入有效,而优先编码器是低电平输入有效,于是就在想,同样都是编码器,为什么不去统一设置一个标准呢?上网搜了搜,有这么几条答案,汇集如下,也

2020-05-18 10:47:13 11830

11830

11830

11830数字电路和模拟电路怎么区分

数字电路就是开关电路;器件工作状态:不是导通就是截止,一般信号电平只管高、低。高为“1”,低电平为“0”;工作状态是脉冲电量。

2020-08-30 09:40:25 23057

23057

23057

23057

一文带你了解数字电路和模拟电路的区别

。逻辑门是数字逻辑电路的基本单元。存储器是用来存储二进值数据的数字电路。 数字电路的特点 电路结构简单,稳定可靠。数字电路只要能区分高电平和低电平即可, 对元件的精度要求不高,因此有利于实现数字电路集成化。 数字信号

2022-12-05 17:36:59 10372

10372

10372

10372如何区分数字电路和模拟电路的电路图

数字电路就是开关电路;器件工作状态:不是导通就是截止,一般信号电平只管高、低。高为“1”,低电平为“0”;工作状态是脉冲电量。而模拟电路是放大电路,丝毫变化都要计较、考虑;是连续变化的电量。仅从

2020-12-15 14:52:00 13

13

13

13嵌入式 TTL电平和CMOS电平

TTL,CMOS都属于数字电路。TTL电流控制器件输出高电平>2.4V输出低电平<0.4VCMOS电压控制器件输出高电平>2.4V输出低电平<0.4V

2021-11-26 18:51:08 10

10

10

10模电数电&TTL电平&上下拉电阻

电子电路是单片机硬件部分的基础知识,电子电路分为模拟电路和数字电路。单片机是使用数字电路,但ADC功能涉及模拟电路。1、模拟电路与数字电路2、欧姆定律3、电源正极和负极4、TTL电平和CMOS电平

2021-12-01 10:06:07 11

11

11

11通俗易懂讲解上、下拉电阻为何能拉高、低电平

一、什么是上下拉电阻?上拉、下拉电阻统一称为拉电阻,作用是将状态不确定的信号线通过一个电阻将其箝位至高电平(上拉)或低电平(下拉)这里有人可能会疑惑?什么叫状态不确定的信号?在数字电路中,通常有三种

2022-01-14 14:22:38 8

8

8

8为什么单片机管脚设计成低电平才有效

规则-----在条件许可的情况下,高电平有效线要尽量缩短,低电平有效的线则尽量延长----这一条规则的存在基础就是基于低电平时环路阻抗比较低,抗干扰能力比较强才起来的。如OC或OD电路要控制一个电平就是通过...

2022-01-14 14:44:43 2

2

2

2高电平、低电平复位电路

单片机最小系统,即单片机能正常工作的最简单的电路。复位电路是单片机最小系统的组成部分之一。对于不同单片机,复位方式有高电平复位和低电平复位,从而相对应地就有两种复位电路,高电平和低电平复位电路,本文

2022-01-17 12:38:52 15

15

15

15数字电路的上升沿、下降沿,你到底搞懂几分?

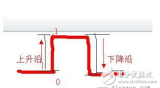

数字电路中,把电压的高低用逻辑电平来表示。逻辑电平包括高电平和低电平这两种。不同的元器件形成的数字电路,电压对应的逻辑电平也不同。

2022-02-09 09:50:54 1

1

1

1数字电路中最基本的门电路

门电路是数字电路中最基本的逻辑单元。它可以使输出信号与输入信号之间产生一定的逻辑关系。在数字电路中,信号大都是用电位(电平)高低两种状态表示,利用门电路的逻辑关系可以实现对信号的转换。

2022-09-16 15:04:44 4705

4705

4705

4705使用光耦给高低电平转化

在数字电子技术中我们会经常进行高低电平之间的转化,比如说一个模块在接收到信号的时候输出高电平,而另一个元件是低电平触发,如果这两个元器件能够很好配合使用的话,这就必须需要进行电平之间的转化,那应该怎么转化呢?我们今天使用光耦给大家提供一个高低电平之间的转化。

2022-12-12 09:12:12 13027

13027

13027

13027数字电路和模拟电路的区别

处理的信号不同 模拟电路处理的是时间和幅度连续变化的模拟信号,而数字电路处理的是用“0”和“1”两个基本数字符号表示的离散信号。在数字电路中,通常低电平用数字“0”来表示,高电平用数字“1”来表示。

2023-02-13 09:54:10 15181

15181

15181

15181为什么说数字电路无法取代模拟电路

,具有高精度和高保真度的特点。在很多领域中,数字电路的应用已经越来越广泛,然而数字电路无法取代模拟电路。 数字电路都是由数字信号构成,采用的是二进制数码的形式来表示电信号,有效抵御了电路噪声、干扰和衰减等因素

2023-08-27 15:37:05 3295

3295

3295

3295建立/保持时间对数字电路的影响

建立/保持时间对数字电路的影响 数字电路是指使用数字信号进行连接和处理信息的电路。数字电路是由一系列数字逻辑门和触发器构成的,这些组件可以在特定的输入下产生特定的输出。时间是数字电路中不可忽略的因素

2023-10-29 14:21:46 1380

1380

1380

1380什么是逻辑电平?如何实现电平转换?(原理讲解+电路图)

逻辑电平是数字电子系统中的关键概念之一。它决定了信号被认定为高电平还是低电平,并进一步影响着数字电路的正确操作。逻辑电平是用来表示数字信号状态的电压水平。在数字电子系统中,常用的逻辑电平有高电平

2023-11-24 08:20:20 13297

13297

13297

13297

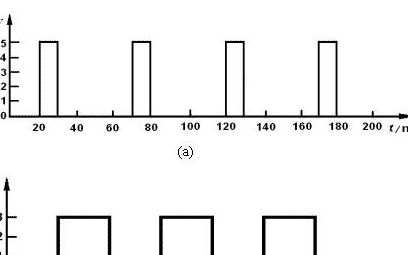

什么是时钟信号?数字电路的时钟信号是怎么产生呢?

什么是时钟信号?数字电路的时钟信号是怎么产生呢? 时钟信号,也称为时钟脉冲,是用于同步数字电路中所有操作的基本信号。它提供了一个参考频率,使得所有电路元件都能按照同样的节奏进行工作。时钟信号是一个

2024-01-25 15:40:52 15223

15223

15223

15223数字电路中的逻辑门电路分类

数字电路中的逻辑门电路分类 数字电路是计算机系统中的重要组成部分,它们由逻辑门电路构成。逻辑门电路是一种基本的数字电路,用于根据输入的逻辑状态生成输出。逻辑门电路可分为多个类别,包括与门、或门、非门

2024-02-04 09:14:16 6329

6329

6329

6329cmos电平与ttl电平如何转换 怎么判断ttl电路高低电平

)是常用的数字电路家族,两者都有自己的特点和应用范围。在介绍如何转换CMOS电平和TTL电平之前,我们先来了解一下它们的定义和特点。 CMOS电平: CMOS电平是一种用于数字电路传输的电压标准。常见

2024-02-22 11:10:52 5619

5619

5619

5619模拟电路和数字电路到底有什么区别?

的电路系统,通过操纵连续的电压或电流来表示输入信号,并产生相应的输出。数字电路是处理离散状态的电路系统,通过操作数字信号(高电平和低电平)来表示输入信号,并产生相应的输

2024-03-05 08:20:54 3281

3281

3281

3281

数字电路仿真元件符号是什么

数字电路仿真元件通常用符号来表示。这些符号是通过简洁和易于理解的图形来表示元件的特性和功能。符号是数字电路设计和仿真过程中非常重要的一部分,帮助工程师和设计者有效地沟通和理解电路的功能。在本文

2024-04-21 09:20:34 4593

4593

4593

4593数字电路中晶体管大多处于什么状态

在数字电路中,晶体管大多处于饱和或截止状态。这是因为数字电路的信号只有两种状态:高电平和低电平,分别对应晶体管的导通和截止状态。本文将介绍数字电路中晶体管的工作原理和状态。 数字电路的基本概念

2024-07-18 15:25:24 2317

2317

2317

2317clk是高电平有效还是低电平有效

在数字电路中,"clk"通常指的是时钟信号(clock signal),它是一种周期性的信号,用于同步数字电路中的各种操作。时钟信号的高低电平有效性取决于具体的电路设计和应用场景。 1. 时钟信号

2024-07-23 11:24:30 6213

6213

6213

6213高电平和低电平输入有什么区别

在数字电子学中,高电平和低电平是两种基本的信号状态,它们分别代表二进制数字1和0。这两种电平状态在数字电路设计、通信和计算机系统中扮演着至关重要的角色。 高电平和低电平的定义 高电平(High

2024-07-23 11:25:49 14441

14441

14441

14441数字电路是对什么信号进行传输的

的逻辑电平。 在现代电子技术中,数字电路扮演着至关重要的角色。从计算机、智能手机到家用电器,数字电路无处不在。 数字电路的基本原理 1. 数字信号与模拟信号 数字信号是一种离散的信号,它由一系列离散的电压或电流水平

2024-08-11 11:00:26 2015

2015

2015

2015芯片引脚悬空是高电平还是低电平

芯片引脚悬空时的电平状态(高电平或低电平)并不是一个固定答案,它取决于多个因素,包括芯片类型、生产厂家、引脚特性以及周围电路环境等。 首先,从逻辑门电路的角度来看,当引脚悬空时,其电平状态可能会

2024-08-28 09:55:16 6261

6261

6261

6261高电平输入和低电平输入是什么意思

在现代电子系统中,数字电路扮演着至关重要的角色。这些电路处理的是二进制信号,即由逻辑“1”和逻辑“0”组成的信号。这些逻辑状态通常通过电压水平来表示,其中高电平代表逻辑“1”,低电平代表逻辑“0

2024-10-17 14:56:42 11417

11417

11417

11417TTL电平标准的介绍与解析

在数字电子领域,TTL电平标准是一种非常重要的逻辑电平标准,它定义了数字信号的高低电平电压范围,确保了不同数字电路之间的兼容性和可靠性。TTL电平标准起源于20世纪50年代,随着晶体管技术的发展而

2025-01-16 09:46:44 3507

3507

3507

3507TTL电平在数字电路中的作用

在数字电子学中,TTL电平是一种广泛使用的逻辑电平标准,它为数字电路的设计和实现提供了一种标准化的电压级别。TTL电平的定义和应用对于理解数字电路的工作原理至关重要。 1. TTL电平的定义 TTL

2025-01-16 09:56:25 3457

3457

3457

3457TTL电平与低电平信号的区别

在数字电子学中,信号的传输和处理依赖于电压水平来表示逻辑状态。TTL电平和低电平信号是两种常见的电压水平,它们在数字电路中扮演着重要的角色。 TTL电平 TTL电平是一种广泛使用的数字逻辑标准,由

2025-01-16 10:21:08 2016

2016

2016

2016数字电路中常见组件

数字电路是由一系列电子组件组成的,它们处理的是二进制信号,即电压水平的高低,通常对应于逻辑“0”和“1”。以下是数字电路中常见的一些组件,以及它们的基本功能和特点: 逻辑门(Logic Gates

2025-01-24 09:40:33 1648

1648

1648

1648数字电路在嵌入式系统中的应用

和可靠性。 数字电路的基本概念 数字电路是由逻辑门、触发器、计数器等基本数字元件构成的电路,它们处理的是离散的数字信号,即二进制信号。这些信号通常由0和1表示,对应于低电平和高电平。数字电路的主要优点包括高速度、

2025-01-24 09:41:55 1241

1241

1241

1241 电子发烧友App

电子发烧友App

评论