什么是低电平有效

首先这是一个输入引脚才存在有效这个温暖体。低电平有效表示这个当这个引脚上电压为低(0-2V)时,这个脚的功能触发(当然要把引脚功能选择为对应的功能)。

为什么要低电平有效

在数字系统中,比较容易出现在低电平上叠加一个噪声正脉冲。如果采用高电平有效的方式,就可能在无效的低电平上,出现高电平噪声,从而使某个信号在不应当有效的时候,出现有效的高电平。而在高电平上,出现一个负噪声脉冲,从而导致某个信号在不应当有效的时候,出现有效的低电平的几率,要小得多。所以在数字系统中,大多数信号的有效电平为低电平。

且低电平时电路的阻抗低,噪声造成的电平变化小,也就是说,抗干扰能力更强。

本文综合整理自nereus78e904、fml003、xiaofeng06、盲文

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

脉冲

+关注

关注

19文章

853浏览量

94766 -

引脚

+关注

关注

16文章

1044浏览量

48959 -

低电平

+关注

关注

1文章

76浏览量

13089

发布评论请先 登录

相关推荐

具有低电平有效的开漏复位功能的3引脚电压监控器TLV8x3数据表

电子发烧友网站提供《具有低电平有效的开漏复位功能的3引脚电压监控器TLV8x3数据表.pdf》资料免费下载

发表于 03-29 10:28

•0次下载

cmos电平与ttl电平如何转换 怎么判断ttl电路高低电平

的CMOS电平一般分为逻辑高电平(High Level)和逻辑低电平(Low Level)。CMOS电平的取值一般在0V到Vcc之间,Vcc是CMOS电路供电电压。逻辑高

什么是推挽电路 推挽输出高低电平介绍

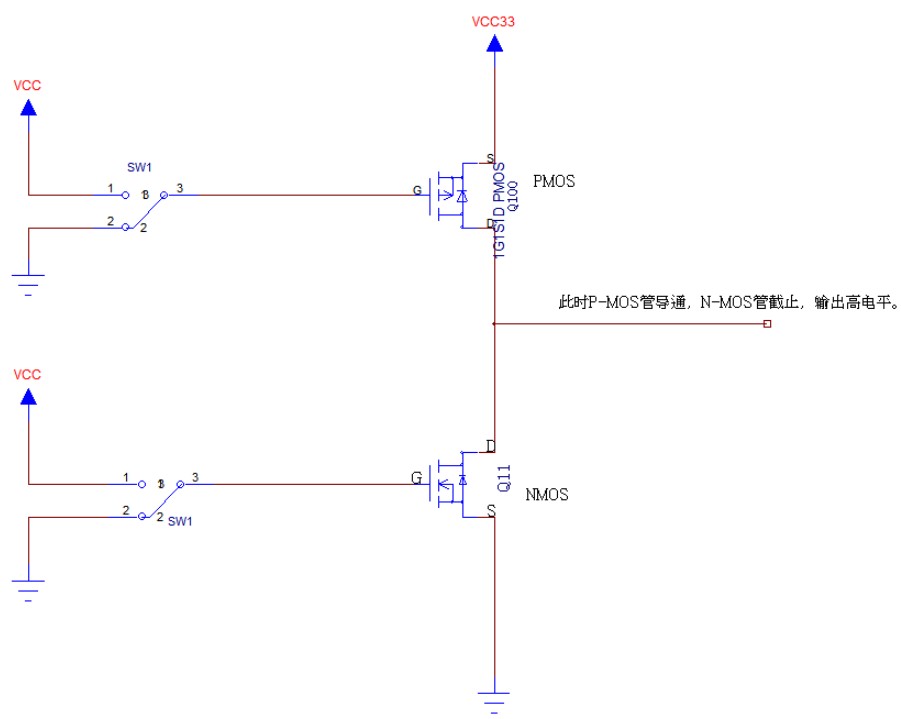

在推挽输出模式下,一个晶体管用于提供高电平输出,而另一个晶体管则用于提供低电平输出。当内部输出为1电平时,上边的晶体管(如MOS管)导通,同时下边的晶体管截止,这时输出高电平。

单片机中的外部中断低电平触发和下降沿触发有什么区别

单片机中的外部中断低电平触发和下降沿触发有什么区别 外部中断是单片机中的一种功能,在特定条件下,外部信号的变化可以引发中断,从而改变程序的执行流程。外部中断可以通过不同的触发方式来激活,包括低电平

jk触发器悬空是高电平还是低电平

触发器会触发并改变输出状态,这取决于JK触发器的触发方式。 在真实的电路中,JK触发器的触发方式是由实际的电压电平决定的,通常有两种模式,分别是悬空状态为低电平和悬空状态为高电平。在本文中,将详细介绍这两种触发方式,并探讨它

cmos输入端接电阻后接地是低电平吗

CMOS是一种常见的逻辑门电路,它使用CMOS技术来实现数字逻辑功能。在CMOS电路中,输入端接电阻后接地的情况下,一般情况下是低电平。 首先,让我们先了解一下CMOS电路的基本原理。CMOS(互补

无论怎么设置ADXL345_DATA_FORMAT 0x31寄存器的INT_INVERT中断有效位,2个中断脚都一直是低电平的原因?

无论怎么设置ADXL345_DATA_FORMAT 0x31寄存器的INT_INVERT中断有效位,2个中断脚都一直是低电平。

按datasheet上

INT_INVERT位值为0,设置中断至高电平

发表于 01-01 06:06

推挽输出是低电平还是高电平?

推挽输出是低电平还是高电平 推挽输出器是一种常见的输出方式。它由负和正三项组成,其中,负电平被连接到PNP晶体管,而正电平被连接到NPN晶体管。当给定输入信号时,晶体管被开启或关闭,

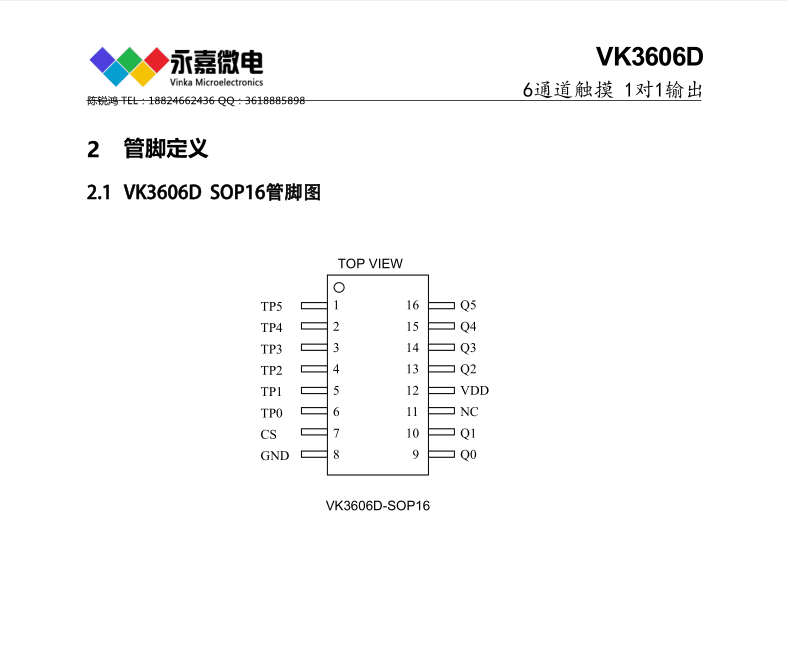

VK3606D高抗干扰6通道6键触摸检测芯片防呆功能,1对1直接输出低电平有效

,仅需极少的外部组件便可实现触摸按键的检测。 提供了6路1对1直接输出低电平有效。最长输出时间10S。芯片内部采用特殊的集成电路, 具有高电源电压抑制比,可减少按键检测错误的发生,此特性保证在不利环境条件的应用中芯 片仍具有很高的可靠性。 此触摸芯片具有自动校准功能,

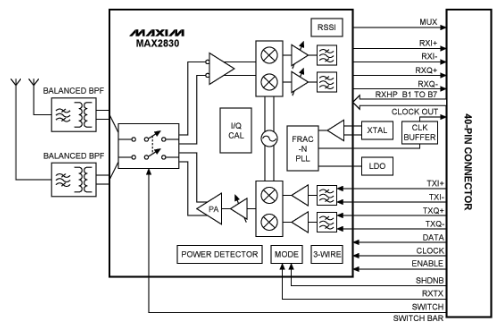

MAX2830 WLAN参考设计

工作条件为:Vcc= 2.85V;V。.BAT = 3.3V; fRF = 2.437GHz; 根据工作模式设置RXTX和低电平有效SHDN; 低电平有效CS = 高

高电平和低电平是什么意思?区别是什么?

高电平和低电平是数字电路中经常会出现的专业名词,它们所表面的意思就是电路上有和无,两者之间没有中间值,在不同的电路上,电压的具体值也是各不相同的。如果用简单的语言表达它们的意思就是开和关,平时

发表于 05-26 10:17

•2.9w次阅读

什么是低电平有效?为什么要低电平有效呢

什么是低电平有效?为什么要低电平有效呢

评论