完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网技术文库为您提供最新技术文章,最实用的电子技术文章,是您了解电子技术动态的最佳平台。

首先说一下xapp1052模块的组成结构:顶层模块是xilinx_pci_exp_ep,在顶层模块中包含pci_exp_64b_app和bmd_design两个模块,其中pci_exp_64b_app就是我们要介绍的重点,而bmd_design则是实现PCIE协议的底层模块。...

频谱分析仪是一种测试测量设备,主要用于射频和微波信号的频域分析,包括测量信号的功率,频率,失真等。它的性能主要是从实时带宽,动态范围,灵敏度和功率测量准确度等四个方面来评价。那么这么高的性能需要什么样的电路才能完成呢?我们已经迫不及待的想要拆开一台频谱分析仪来一探究竟啦! ...

在现实生活中或许有很多硬件爱好者会对支持高速金融服务器这种高端大气上档次的服务器十分好奇,也好奇实现这样的一个金融交互池除了是只需要强大的软件架构以及软件实现吗?我们FPGA这样的硬件是否可以为搭建这样的服务器作出一些贡献呢?SmartNIC fb4CGg3@VU PCIe 开发板告诉我们可以的,并...

FPGA 有一个响亮的别名——“万能芯片”,它是一种能够通过软件更改、配置器件内部连接结构和逻辑单元,完成既定设计功能的数字集成电路。虽然FPGA问世的时间不长,但发展非常迅猛,远超出了业界的预想。...

代码设计完成后,最好先使用开发工具进行语法检测,之后进行功能仿真,此处仿真不涉及时序上的延时。仿真工具首推ModelTech公司的ModelSim,也可以用ISE的Quartus 2进行简单仿真。...

proc文件系统是用来提供内核和进程信息的虚拟文件系统,使用内核自动生成的文件,加载完成一定要能查到很多信息才对。...

对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和异步复位没有区别,当然由于器件内部信号均为高有效,因此推荐使用高有效的控制信号,最好使用高有效的同步复位。输入复位信号的低有效在顶层放置反相器可以被吸收到IOB中。...

FPGA具有丰富的硬件计算单元以及分布式并行内存,其他芯片只有非常有限的计算资源,比如CPU只有几个高性能ALU,另外其他芯片一般使用一个共享内存,在任何是有只能进行一次的读或者写操作。...

物联网(IoT)的规模和复杂性不断上升,对主动的强化安全措施的需求日益增加。仅利用软件安全功能已经不足以应对已知的网络威胁,更有效的方法是采用分层技术战略,这种战略以采用能够提供IC级硬件可信根的新一代系统级芯片(SoC) FPGA开始。在此坚实的基础之上,应采用可扩展的解决方案,包括根据风险合适的...

该系统的监控端采用了基于CortexA8系列的ARM处理器,该处理器同时兼顾了成本与性能的要求,可设计美观的图形化操作界面。该系统工作于BD2-B1和GPS-L1两个频点,便携性好,界面直观,可通过按键或触摸屏两种方式操作,同时可随时采集户外复杂环境下的导航卫星信号,极大地提高了导航接收机的开发效率...

Xilinx 7系列FPGA的HP bank都支持DCI,目的是在高速单板信号传输中保持信号完整性,减少反射等因素影响,那么DCI是什么?digitally controlled impedance是DCI的缩写,应该也算上xilinx 在IO feature上的一项技术(这不是7系列才有的新技术)...

项目设计初期会选型,工程师根据资源、IO、硬核、IP等选择对应型号的FPGA。功耗部分xilinx提供了XPE表格(Xilinx PowerEstimator),这个XPE支持zynq、目前也有各个系列的器件列表,包括最新的ultrascale + 。...

UFDM建议正确的HDL coding风格来满足目标器件,讨论时序约束和时序收敛。正确的IO约束,IO管脚分配和布局,物理约束,并提供了满足时序收敛的技巧和让FPGA工作快速稳定的方法。...

在FPGA系统中,如果数据传输中不满足触发器的Tsu和Th不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足,就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端在0和1之间处于振荡状态,而不是等于数据...

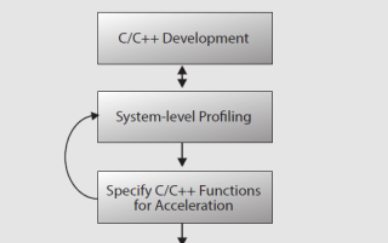

开发机器视觉系统通常需要大量的时间来设计能执行所有重要图像采集及处理功能的电子产品。通常需要两年多的时间,这会给摄像机及系统制造商的上市进程与产品规划带来不利影响。...

有限状态机(Finite State Machine, FSM),根据状态机的输出是否与输入有关,可分为Moore型状态机和Mealy型状态机。Moore型状态机输出仅仅与现态有关和Mealy型状态机不仅与现态有关,也与输入有关,所以会受到输入的干扰,可能会产生毛刺(Glith)的现象,所以我们通常...

介绍FPGA约束原理,理解约束的目的为设计服务,是为了保证设计满足时序要求,指导FPGA工具进行综合和实现,约束是Vivado等工具努力实现的目标。所以首先要设计合理,才可能满足约束,约束反过来检查设计能否满足时序。主要涉及到xilinx vivado xdc约束语法,给出对应的ISE ucf 语法...

随着HEVC、AV1等更复杂算法的Codec份额逐步增长,实现高质量视频编解码需要硬件支持,软件的方式无论在服务器端和移动端都非最佳的方案。FPGA专用芯片能够降低延迟和成本。在NAB 2018大会上,资深多媒体技术咨询师Jan Ozer对Ngcodec的CEO Oliver Gunasekara进...