完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网技术文库为您提供最新技术文章,最实用的电子技术文章,是您了解电子技术动态的最佳平台。

Spartan-6系列具有低成本、省空间的封装形式,能使用户引脚密度最大化。所有Spartan-6 LX器件之间的引脚分配是兼容的,所有Spartan-6 LXT器件之间的引脚分配是兼容的,但是Spartan-6 LX和Spartan-6 LXT器件之间的引脚分配是不兼容的。...

Xilinx以制造 可编程门阵列(FPGA)而闻名,它是基于一个通过可编程接点连接的可配置逻辑块(CLBs)矩阵。根据Control Engineering Europe中的 “FPGA的优点(Advantages of FPGA)”这篇文章,多种控制回路能够以不同但是十分快的速度在FPGA设备上运...

本文是基于FPGA实现Cordic算法的设计与验证,使用Verilog HDL设计,初步可实现正弦、余弦、反正切函数的实现。将复杂的运算转化成FPGA擅长的加减法和乘法,而乘法运算可以用移位运算代替。Cordic算法有两种模式,旋转模式和向量模式。可以在圆坐标系、线性坐标系、双曲线坐标系使用。本文线...

因为Zynq-7000 PS(Processing System)端嵌入了Cortex-A9 ARM 处理核以及PL(Programmable Logic)端为基于Kintex-7或者Artix-7的FPGA架构使得Xilinx Zynq-7000更加强悍,应用领域更加广泛。下面将从以下方面介绍Zy...

JESD204B协议是目前高速AD,DA通用的协议。对于基带使用FPGA用户来说,Xilinx品牌的FPGA使用更为常见。Xilinx提供了JESD204的IP core,设计起来比较方便。...

工业机器视觉是一项综合技术,其中包括数字图像处理技术、机械工程技术、控制技术、电光源照 明技术,光学成像技术、传感器技术、模拟与数字视频技术、计算机软硬件技术、人机接口技术等。这些技术在机器视觉中是并列关系,相互协调应用才能构成一个成功的工业机器视觉应用系统。...

因此,要想学好FPGA,你得用硬件的思维方式来编写代码,注重FPGA的系统结构设计,好的系统结构设计会带来质的飞跃,这就告诉我们RTL Coding其实是硬件结构设计,而非基于处理器架构的C语言程序开发,好的RTL Coding就是好的硬件结构。 ...

在生成滤波器IP核之前需要产生抽头系数,这个抽头系数的阶数是自己设定的,阶数越高代表滤波器乘累加运算越多,但是阶数大小的选择要看是否满足自己的设计要求(例如衰减db是否满足要求)。同时,生成的滤波器抽头系数的值是与自己设计滤波器的各种参数确定的,如数据采样速率,通带截止频率、阻带起始频率(低通)、滤...

这个参数确定的是移位寄存器的移位时钟个数。这个时钟个数取决于后面的Depth参数。其中第一个参数Fixed Length 指的是移位周期数是固定的(后面的Depth指定)。第二个参数指的是可变长度的,也就是说移位寄存器的移位长度是可变的,至于长度究竟是多少,那就得看下面的参数Depth了,这个Dep...

同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。改变后的状态将一直保持到下一个时 钟脉冲的到来,此时无论外部输入 x有无变化,状态表中的每个状态都是稳定的。 异步时序逻辑电路的特点:电路中除可以使用带时钟的触发器外,还可以使用不带时...

使用git工具下载源码,如果没有安装git工具,可以使用sudo apt-get install git进行安装...

为了让初学 Python 的程序员避免犯同样的错误,以下列出了我学习 Python 时犯的三种错误。这些错误要么是我长期以来经常犯的,要么是造成了需要几个小时解决的麻烦。...

xilinx-arm-linux交叉编译链最后一个版本就是2011版本,之后的xilinx不再单独提供交叉编译链了,如果需要最新的,请安装SDK开发软件,之后再安装目录中查找,或者source setting.sh激活即可使用。 ...

由于Quartus ii软件ROM用的是mif格式的文件,且可以用软件Guagle_wave生成正弦波、三角波、锯齿波。我们可以利用这个软件先生成数据,然后再将其转化为符合COE格式的文件。...

xilinx官方实例代码如下,其实大概意思就是一个高电平之后,变成低电平。然后再高电平,等待tlast信号再拉低。这样做的为了时序紧凑型,xilinx为了方便在第一个valid和ready信号得到头部信号,这个有个短暂的停留时间去分析头部数据。...

随着人工智能(AI)的不断发展,它已经从早期的人工特征工程进化到现在可以从海量数据中学习,机器视觉、语音识别以及自然语言处理等领域都取得了重大突破。CNN(Convolutional Neural Network,卷积神经网络)在人工智能领域受到越来越多的青睐,它是深度学习技术中极具代表性的网络结构...

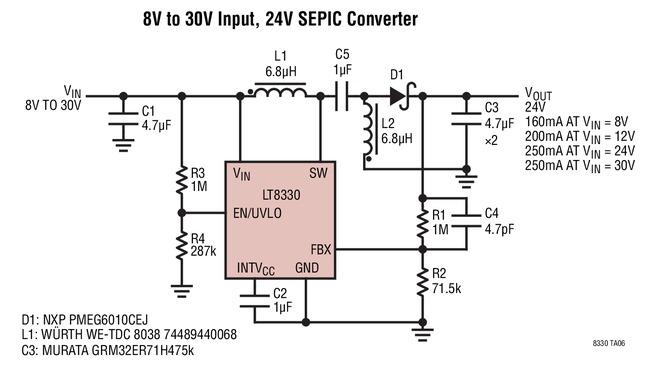

LT8330 是一款电流模式 DC/DC 转换器,其能够采用单个反馈引脚产生正或负输出电压。该器件可配置为一个升压、SEPIC 或负输出转换器,消耗的静态电流低至 6μA。低纹波突发模式操作能在非常低输出电流条件下维持高效率,并在典型应用中保持输出纹波低于 15mV。...