完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

标签 > mpsoc

文章:106个 浏览:25077次 帖子:15个

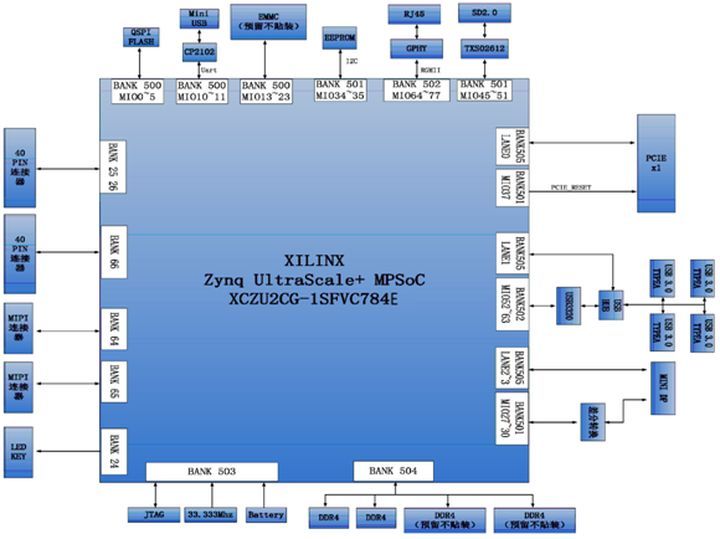

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二章硬件原理图介绍

XCZU2CG-1SFVC784E芯片的PS系统PS系统集成了2个ARMCortex™-A53处理器,速度高达1.2Ghz,支持2级Cache;另外还包...

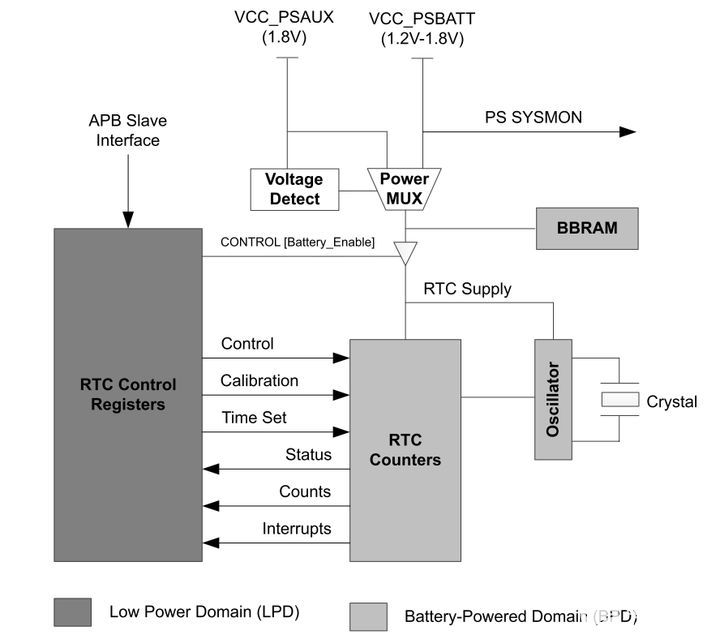

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十章PS端RTC中断实验

实验中通过简单的修改Vitis的例程,就完成了RTC,中断的应用,看似简单的操作,但蕴含了丰富的知识,我们需要非常了解RTC的原理、中断的原理,这些基本...

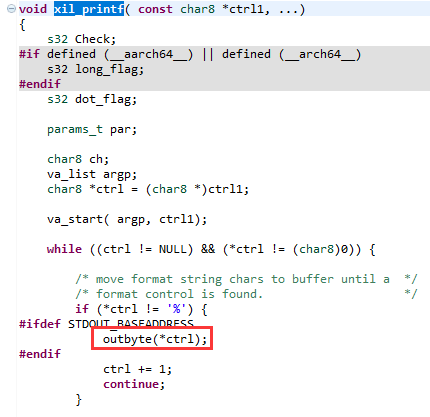

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十一章PS端UART读写控制

除了打印信息之外,如果我们想用UART进行数据传输呢?本章便来介绍PS端UART的读写控制,实验中,每隔1S向外发送一串字符,如果收到数据,产生中断,并...

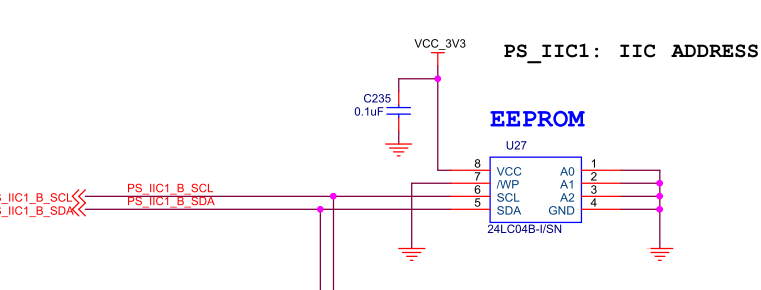

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十二章PS端I2C的使用

ReadBuffer清0,WriteBuffer赋FF写16个字节到EEPROM读EEPROM的16个字节到ReadBuffer检验是否正确Readbu...

Ultra96 是一款基于 Arm 技术的赛灵思 Zynq UltraScale+ MPSoC 开发板,符合 Linaro 96Boards 规范。96...

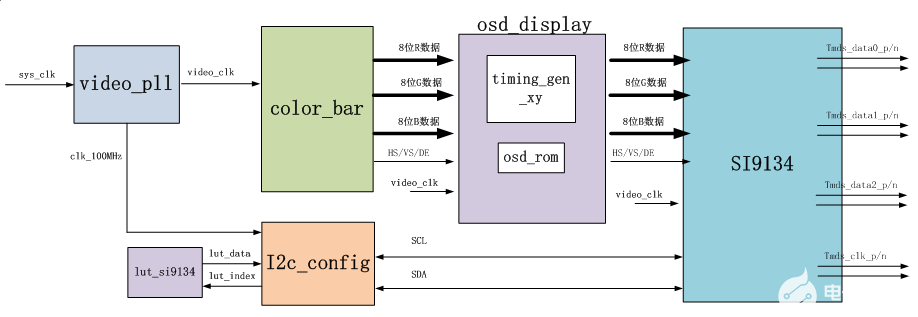

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十四章HDMI输出实验

由于开发板上只有DP可以显示,但却是PS端的,PL端没有HDMI的接口,因此我们采用AN9134的HDMI扩展模块实现HDMI显示。将24位RGB编码输...

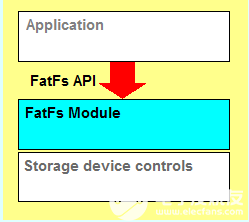

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十四章PS端SD卡读写

FatFs是一个通用的文件系统模块,用于在小型嵌入式系统中实现FAT文件系统。FatFs的编写遵循 ANSI C,因此不依赖于硬件平台。它可以嵌入到便宜...

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十五章HDMI字符显示实验

在HDMI输出实验中讲解了HDMI显示原理和显示方式,本实验介绍如何使用FPGA实现字符显示,通过这个实验更加深入的了解HDMI的显示方式。

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十七章System Monitor

本章介绍system monitors的使用,用于监测芯片的电压、温度值等,也可以通过PL端的ADC引脚作为外部信号的采集。PL端可以做17路ADC的采...

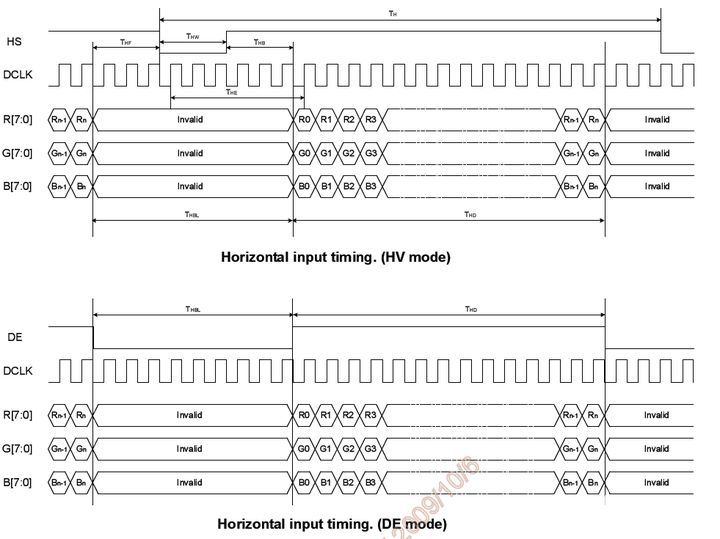

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十六章7寸液晶屏显示实验

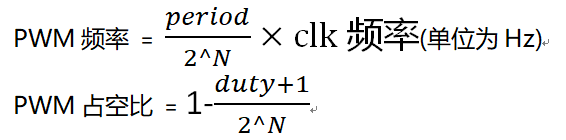

LCD屏显示方式从屏幕左上角一点开始,从左向右逐点显示,每显示完一行,再回到屏幕的左边下一行的起始位置,在这期间,需要对行进行消隐,每行结束时,用行同步...

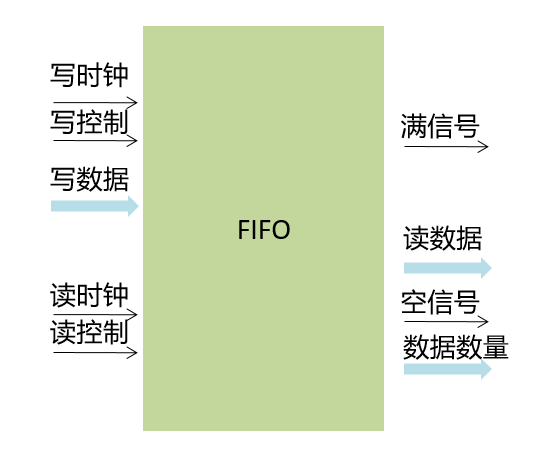

【ZYNQ Ultrascale+ MPSOC FPGA教程】第八章FPGA片内FIFO读写测试实验

FIFO: First in, First out代表先进的数据先出,后进的数据后出。Xilinx在VIVADO里为我们已经提供了FIFO的IP核, 我...

【ZYNQ Ultrascale+ MPSOC FPGA教程】第三十章自定义IP实验

创建自己的IP核有很多好处,例如系统设计定制化;设计复用,可以在在IP核中加入license, 有偿提供给别人使用;简化系统设计和缩短设计时间。用ZYN...

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十三章RS485实验

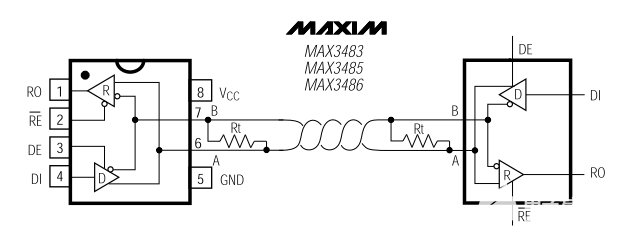

RS485与RS422类似,也是采用差分信号传输,但RS485是半双工传输,也就是说,同一时刻只能有一个方向的数据传输。而且接口也比RS422少,只有差...

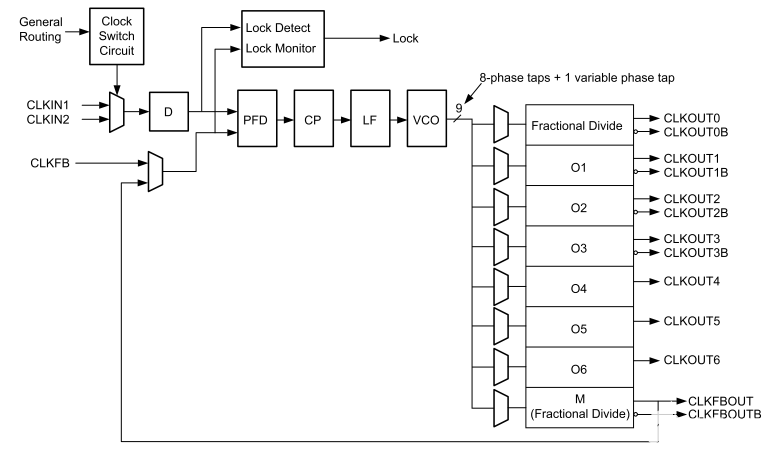

【ZYNQ Ultrascale+ MPSOC FPGA教程】第五章Vivado下PLL实验

PLL(phase-locked loop),即锁相环。是FPGA中的重要资源。由于一个复杂的FPGA系统往往需要多个不同频率,相位的时钟信号。所以,一...

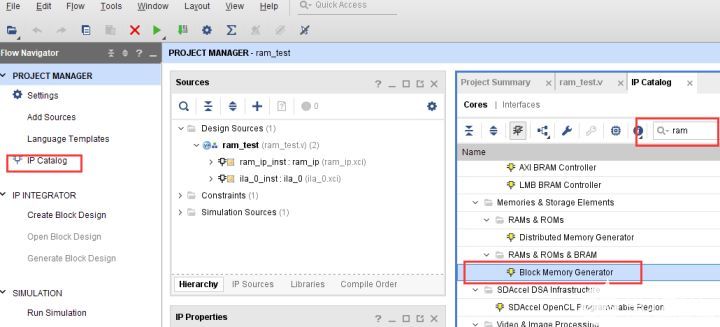

【ZYNQ Ultrascale+ MPSOC FPGA教程】第六章FPGA片内RAM读写测试实验

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该...

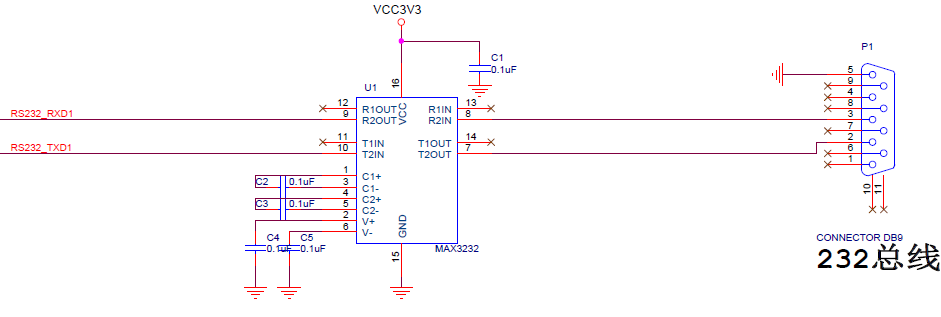

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十一章RS232实验

AN3485模块的RS232接口采用MAX3232芯片实现RS232和+3.3V TTL电平的转换。TTL电平的串口接收和发送信号(RXD, TXD)连...

Zynq UltraScale+ MPSoC的ZCU102开发套件的开发流程

使用Zynq UltraScale + MPSoC的ZCU102开发套件,该视频展示了使用SDSoC开发环境的开发流程。

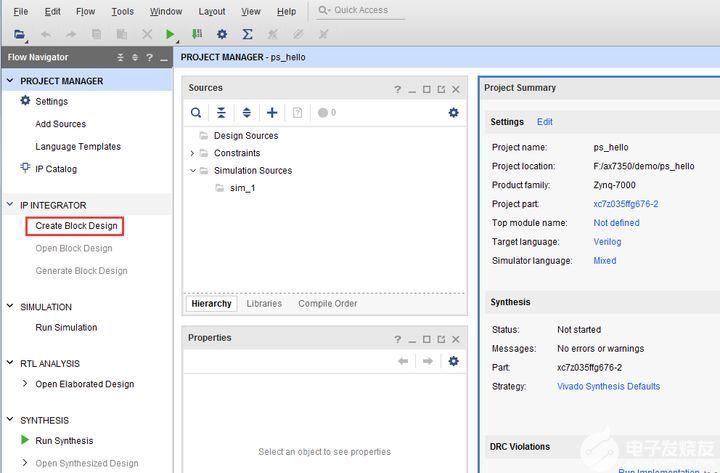

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十八章 Hello World(上)

我们从原理图中可以看到ZYNQ芯片分为PL和PS,PS端的IO分配相对是固定的,不能任意分配,而且不需要在Vivado软件里分配管脚,虽然本实验仅仅使用...

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |