原创声明:

本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处。

适用于板卡型号:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

vivado工程目录为“ps_hello/vivado”

软件工程师工作内容

以下为软件工程师负责内容。

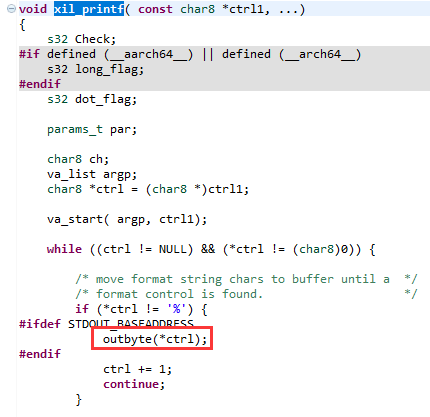

在前面的实验中,大家或多或少会发现有打印信息的情况,主要是调用”xil_printf”或”printf”,但是通过什么打印信息呢?我们还记得打印信息之前设置了串口,是的,确实是串口,但这些函数是如何调用串口呢?其实我们可以在”xil_printf”函数定义中看到,注意outbyte函数就是调用UART打印的。

再进入outbye的函数,即可看到调用了PS端UART的函数,得以在串口中显示。

除了打印信息之外,如果我们想用UART进行数据传输呢?本章便来介绍PS端UART的读写控制,实验中,每隔1S向外发送一串字符,如果收到数据,产生中断,并将收到的数据再发送出去。

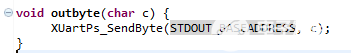

1.UART模块介绍

以下是UART模块的结构图,TxFIFO和RxFIFO都为64字节。

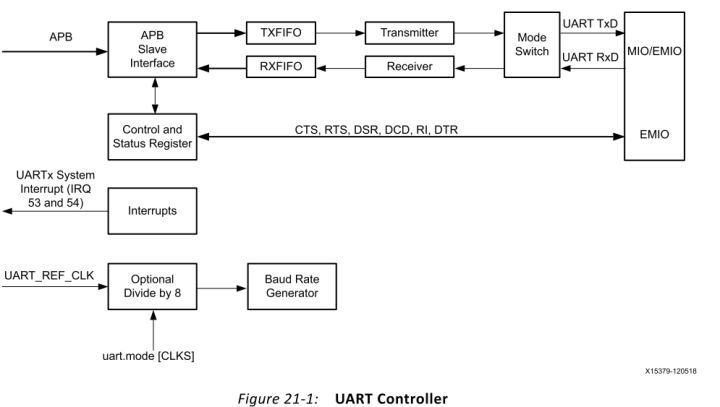

下图为UART的四种模式

可以用remote loopback mode测试物理电路是否正常,使用API函数XUartPs_SetOperMode

2. Vitis程序开发

1) 本实验流程如下:

主程序流程:

UART初始化设置UART模式设置数据格式设置中断发送UART数据检查是否收到数据如果收到,发送收到的数据,如果没有,等待1秒钟,继续发数据

中断程序流程:

中断初始化设置接收FIFO trigger中断寄存器,设置为1,即收到一个数据就中断打开接收trigger中断REMPTY及接收FIFO空中断RTRIG

中断服务程序:

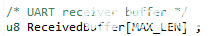

判断状态寄存器是trigger还是empty清除相应中断trigger状态读取RxFIFO数据,empty状态将接收标志ReceivedFlag置1

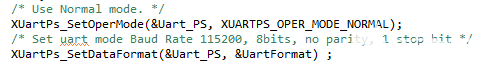

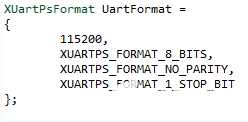

2) 在main函数中进行模式的设置,可以直接调用函数,设置为正常模式,数据格式设置为波特率115200,数据8bit,无校验位,1bit停止位。UartFormat定义在uart_parameter.h中。

3) 中断控制器程序初始化可参考按键中断方式,用法类似。

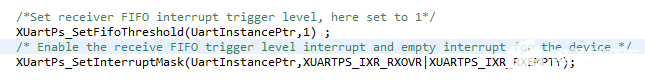

4) 在main函数中将trigger level设置为1,打开trigger和empty中断。

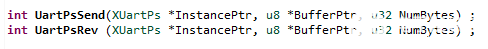

5) 数据的发送和接收函数参考了UARTPS的XUartPs_Send和XUartPs_Rev函数,但它们会打开某些中断,不符合预期,因此做了修改。

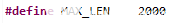

在接收缓存中设置了最大2000字节的缓冲,可以根据需要修改。

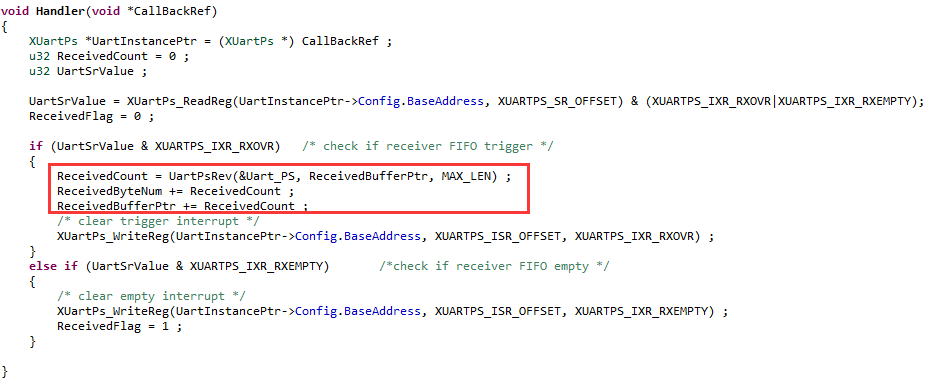

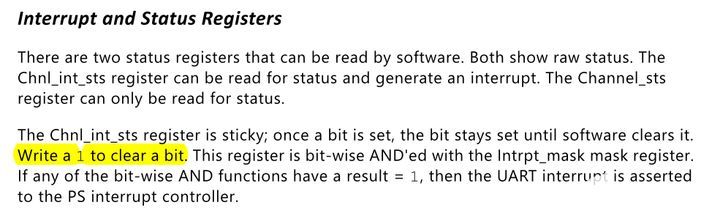

6) 在中断服务程序中,将ReceivedBufferPtr指针地址和ReceivedByteNum加上接收到的个数,如果FIFO空了,将ReceivedFlag置为1。同时向中断状态寄存器写数据,清除中断。

Ug1085 UART清除中断

Ug1085 UART清除中断

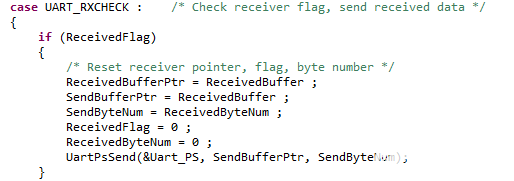

7) 在main函数中,将ReceivedFlag和ReceivedByteNum清零,ReceivedBufferPtr指针复位。

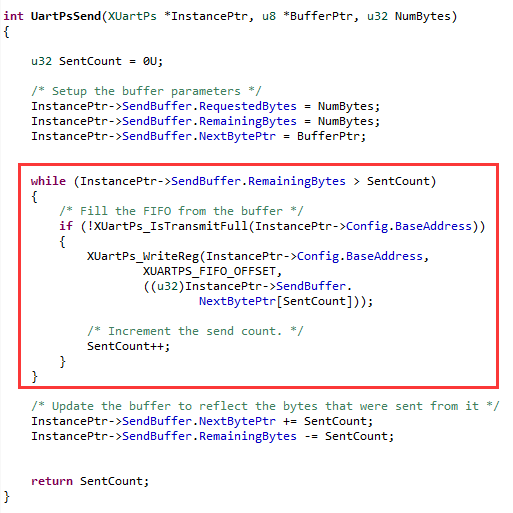

8) Uart发送函数中,判断TxFIFO是否满,否则继续发送,直到计数达到NumBytes

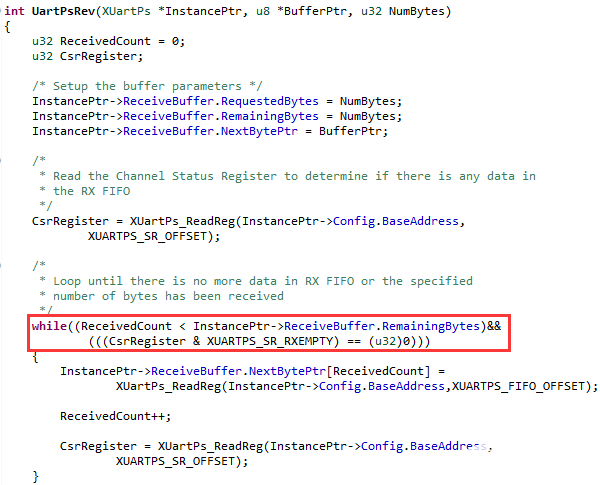

9) Uart接收函数中,判断接收RxFIFO是否为空,否则继续读数据,NumBytes为需要读取的数据个数,但如果接收的FIFO空了,计数没有达到这个值,也会结束此函数。

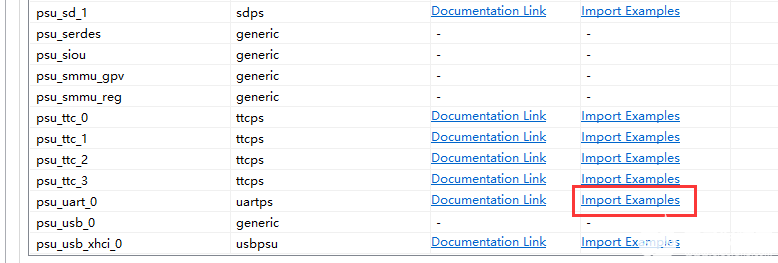

10) 除了自己写程序外,还可以从system.mss中导入模块的例子,参考Xilinx提供的程序,方便学习。

3. 板上验证

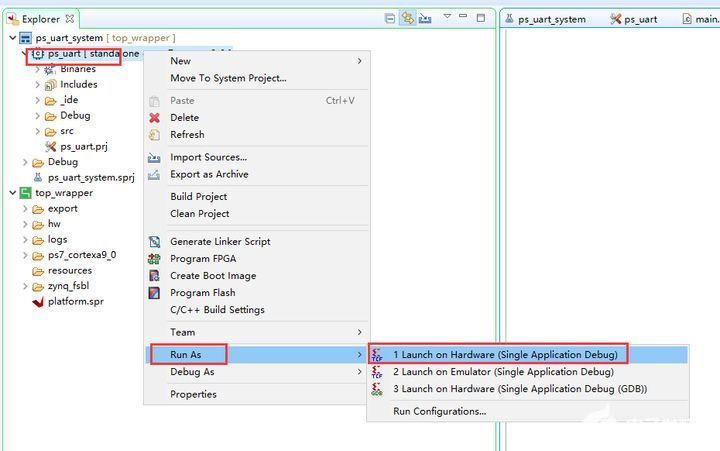

1) 接下来下载程序

2) 打开工程目录下的串口调试工具

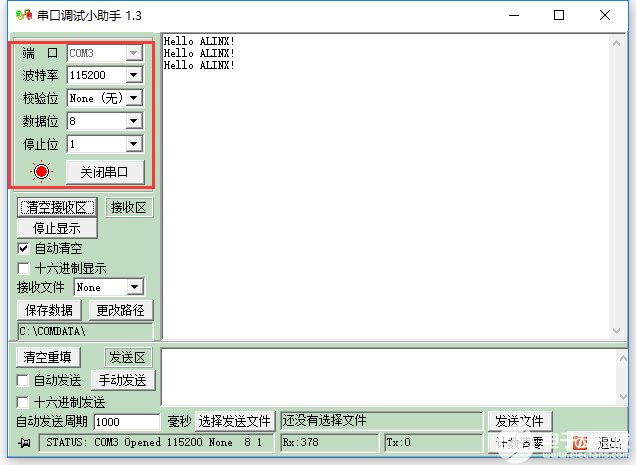

3) 设置好参数如下,打开串口,即可看到打印信息。

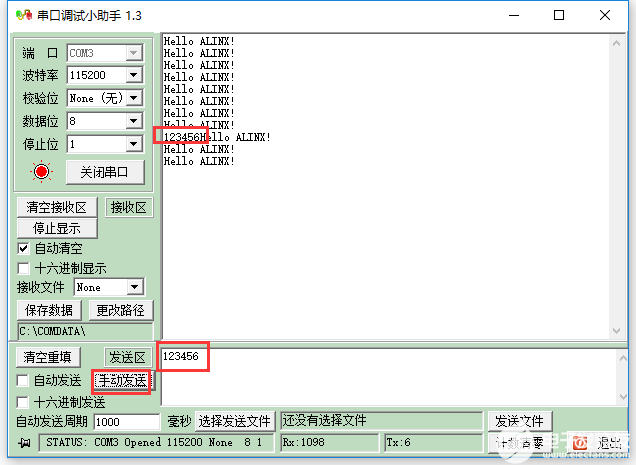

4) 在发送区填入数据,点击手动发送,即可看到接收区的数据。

4. 总结

本章学习了UART的发送与接收,以及中断的使用,希望大家能养成良好的习惯,多看文档,理解原理,能对系统的认识有很大提高。

-

FPGA

+关注

关注

1664文章

22508浏览量

639450 -

串口

+关注

关注

15文章

1627浏览量

83383 -

uart

+关注

关注

22文章

1322浏览量

107017 -

Zynq

+关注

关注

10文章

633浏览量

49584 -

MPSoC

+关注

关注

0文章

203浏览量

25231

发布评论请先 登录

明德扬视频分享点拨FPGA课程--第二十一章 矩阵键盘工程

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器

第二十一讲 组合逻辑电路中的竞争冒险

模拟电路网络课件 第二十一节:场效应管与BJT放大电路的比较

闲话Zynq UltraScale+ MPSoC(连载1)

闲话Zynq UltraScale+ MPSoC(连载5)

Zynq UltraScale+ MPSoC的发售消息

米尔科技Zynq UltraScale+ MPSoC技术参考手册介绍

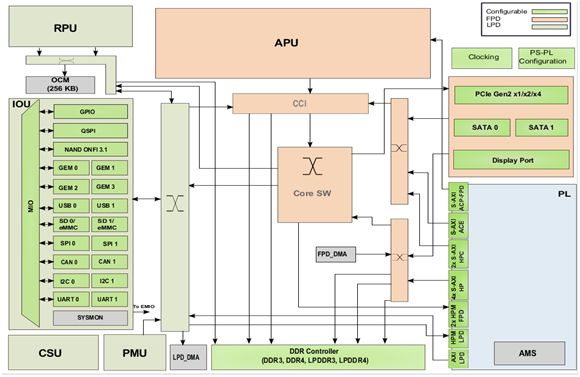

【ZYNQ Ultrascale+ MPSOC FPGA教程】第一章 MPSoC芯片介绍

如何调试 Zynq UltraScale+ MPSoC VCU DDR 控制器?

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十一章PS端UART读写控制

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十一章PS端UART读写控制

评论