CompactRIO是美国国家仪器(NI)公司生产的一款可重新配置的嵌入式测控系统。CompactRIO系统拥有坚固的硬件架构,其中包含:I/O 模块、带有可重新配置的现场可编程门阵列(FPGA)的机箱

2012-08-28 09:32:45 1873

1873 一个I/O中断,initP3的中断使能,能用P3.2/P3.3两个中断吗?

2025-01-26 09:35:30

计算机的并行打印口上,另一端接在PCB板上的一个十芯插头,PLD芯片有四个管脚(编程脚)与插头相连。(如图) 它向系统板上的器件提供配置或编程数据,这就是所谓的在线可编程(ISP,如下

2012-02-27 10:42:53

)放置flash 偏移地址0x50000处,关闭看门狗,重新配置后,发现fpga只更新了硬核,软核没有运行。通过测试,发现更新完硬核后,软核还是找到的第一个程序软核入口。没有找到要更新程序软核入口地址。不知道如何设置,使重新配置后,能够找到更新程序软核地址?希望大神帮助。。感激

2017-07-30 10:21:09

CC2530的I/O外部中断CC2530有18个中断源,这些中断源在手册中如图,我们一般说的I/O外部中断,一般是指序号 6、13、15外部输入中断,Port x inputs。通用I/O 引脚设置

2016-04-15 16:03:27

主要区别有二点:1、FPGA基本有可编程I/O单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等6部分组成。CPLD的结构相对比较简单,主要由可编程I/O单元

2018-08-28 09:15:53

请问一下,GPIO引脚配置成QSPI或者USART以后,怎么重新配置成,默认状态啊?

就像没有使用该引脚的时候的状态一样

2024-03-28 09:15:13

我有一个系统接收配置文件并将其写入闪存。之后,所有需要的是重置或电源循环,因此它将加载'升级'并保持'黄金'以防万一它失败。我想过使用HWICAP IP,但在我看来,更适合部分重新配置和重新配置而

2020-06-10 13:18:41

如何用PLL对时钟进行配置呢?PLL配置时钟唤醒后还需要重新配置RCC吗?

2021-11-22 06:30:33

(void)改写。 我希望在主循环里面重新配置RTC唤醒时间。 因为我发现在RTC中断中更改这个RTC时间,有的时候会让我的数据采集出问题,感觉有些时候这部分耗时可能会长一些,会倒是我数据采集的时候丢数据。

我是在系统唤醒后第一时间就调用了rtc重新配置的函数。 希望能够帮忙解决一下此问题。 感谢!

2024-02-21 06:53:16

你好,我怀疑重新配置PSoC的财产。我已经知道,这个系统的硬件有能力根据PSoC Creator的软件进行配置。我不知道,一旦你配置了系统,并且你正在运行这个项目,会发生什么,你可以重新配置它,例如

2019-03-28 14:07:42

。但是,当我再次打开电源时,它不会重新配置。关于在哪里寻找问题的任何建议?现在,FPGA的电源和IO bank的电源来自独立的电源。这可能是问题吗?

2020-06-04 16:30:14

我正在使用 STM32L475RC 开发一个项目。根据运行状态,STM32 在运行模式、低功耗运行模式和关机模式等不同运行模式之间切换。当从运行模式切换到低功耗运行模式时,时钟也会重新配置。我面临

2023-01-16 08:50:25

TAS5721使用过程中因为音源不同,所有对采样率进行重新配置,配置后需要重新启动才能生效配置吗?还是必须重新初始化一下,谢谢!

2024-11-06 07:29:03

你好我有一个任务是在VC709板上进行部分重新配置的演示。完成所有配置的实现后,生成比特流的准备就可以了。我发出了打开检查点的命令,然后发出了“write_bitstream”命令。但是,他们就是

2020-06-04 11:10:48

; 通过使用LabVIEW FPGA 模块和可重新配置I/O(RIO)硬件,NI 为您提供了一种直观可用的解决方案,它可以将FPGA技术的灵活性整合到测量和控制系统

2009-05-30 17:32:27

用vhdl实现cpld配置fpga,配置成功后在usermode下设置一个重新配置信号,当信号有效时对fpga进行重新配置;fpga配置程序放在flash内;现在遇到的问题是,上电cpld能够正常配置fpga并且进入usermode ,但是加上重新配置语句过后就不能成功配置fpga,求高人指点~

2013-01-17 22:35:39

嗨,我是学生我研究了如何在SPARTAN6中设计部分重新配置好几个月,但仍然不知道如何使用它。有我的知识: - 通过planAhead实施设计PlanAhead的部分重新配置设计。 (我

2019-02-22 08:22:33

我每次用vscode打开工程时都需要重新配置esp-idf插件的配置,设置esp-idf与工具链的路径。这是为什么?这是正常的吗?而且我如果没打开某个文件夹就进行配置还会出现报错。如下图所示。

2023-02-21 07:44:38

喜我使用ICAP原语实现了部分重配置。 (VCU1525板,xcvu9p)我的问题是,IO引脚在重新配置期间是否会出现高阻抗?例如,在我的设计中,部分重配置区域内有DDR4 MIG IP内核。如果

2020-06-10 07:18:05

能否告诉我在 CapSense 按钮触发时是否有可能重新配置 I/O 的操作?

我想使用一个 CapSense 按钮并启用/禁用电路上的另一个 IC。

这意味着,如果按下 CapSense 按钮,输出将永久保持高电平,而如果再次按下,输出将变为低电平。

我正在使用CYUSBS236开发工具包。

2024-02-23 06:20:57

复用器被送至最终的视频解码器播放。u*** 2.0 phy芯片可被轻松连接至pld的任意i/o引脚。大多数pld的i/o引脚都可被编程实现3.3、2.5、1.8或1.5v lvttl/lvcmos

2018-12-28 07:00:06

大家好!我正在使用Spartan6 FPGA为高速DAC提供数据。必要的高速I / O时钟由PLL实例完成。在我的申请中,我有两种不同的情况:case1:我需要从80MHz参考(M = 12)产生

2019-07-31 10:59:14

你好Xilinx收发器使用CML IOSTANDARD。在xilinx 7系列示例设计中,有固定的GTREFCLK位置,但其他引脚未配置(txdata / rxdata)在下面的I / O表中,txdata和rxdata引脚未配置CML I / O标准。我如何配置CML I / O标准?

2020-08-13 10:10:53

,我们最初使用.bit文件对FPGA进行编程。当用户信号触发重新配置时,我们希望程序从WBSTAR寄存器中提到的地址再次启动。你能帮忙了解一下设置地址出了什么问题吗?谢谢你。拉格米PS:我们的目标是最终

2020-06-04 15:10:44

经常重新配置FPGA,并希望在主机系统运行时这样做。为了澄清,ML555板插入到与我的开发环境不同的系统中。我有一个独立的平台电缆USB从我的开发机器到ML555板,它是一个单独的测试机器。我想在

2019-08-22 09:58:51

新比特流的FPGA。任何人都可以告诉我这是否可能?我只能找到有关使用ICAP进行部分重新配置或从外部Flash进行完整配置的文档。我想从RAM重新配置,所以我给MicroBlaze一个解压缩比特流的机会。如果之前有人问过这个问题,我会道歉,但我自己搜索了几天,却找不到关于这个主题的任何内容。谢谢!

2020-05-29 17:12:21

是否有任何教程显示如何使用PowerPC或microblaze作为重配置控制器?我目前使用Impact工具使用部分比特流(ISE和Planahead 12.1)重新配置FPGA,但我想要一个重配置

2019-01-22 11:05:28

尊敬的先生/女士,我没有在新项目设计源中指定合成(edif或ngc)网表选项下设置PR项目,使用planahead进行部分重新配置..我在设置分区阶段面临问题..当我在网表视图中选择分区时..i没有设置用于可重新配置分区的分区向导..请告诉如何启用PR..please帮助

2019-11-05 07:14:38

我们如何在xilinx FPGA中执行运行时重新配置?

2020-07-16 10:24:37

嗨,我想知道是否可以动态地将ISERDES2重新配置为不同的序列化比率。我检查了SelectIO用户指南,但找不到这样的选项。任何想法都表示赞赏。谢谢汤姆以上来自于谷歌翻译以下为原文Hi, I am

2019-07-08 08:02:51

嗨,我可以使用内部配置访问端口(ICAPE2 Primitive)来重新配置FPGA。我的意思是说我有一个加载了一些设计的位文件,我想加载一个全新的位文件/设计,例如存储在DDR3或一些NAND闪存

2019-03-26 15:37:47

嗨,我有设计工具的浮动许可证,我获得了另一个节点锁定许可证,用于部分重新配置。我使用Ubuntu,我无法安装部分重新配置的许可证。我试过这个:export LM_LICENSE_FILE

2019-01-23 06:45:50

嗨,是否可以完全重新配置具有不同硬件门的FPGA?目前,我没有PR功能。我想用不同的设计完全重新配置我的Zynq板。假设,我有和门和xor门,两者都在PL中单独工作,但可以完全重新配置zynq,以便

2019-04-11 11:55:05

0x00000000

0x81600081 0x00000000 0x000000E7

此重新配置数据在我们的电路板上不起作用。这导致在上电后从 bootROM 进行一些 QSPI 传输,然后进行

2023-05-22 09:35:01

嗨,我是学生 我尝试使用virtex5与部分重新配置教程UG702,但本教程设计为virtex6(ML605)所以我需要修复它 为virtex5创建新的综合和网表(从源代码复制.v文件并运行合成

2020-06-16 07:28:38

你好我可以测量将.bit重新配置到PR区域所需的时间吗?我在论坛中搜索,我得到了使用.bit文件大小和处理器频率测量时间的近似计算。我正在寻找更准确的近似值。就像盯着计时器并在重新配置后结束它。谢谢阿努普。

2020-04-02 09:21:18

能否告诉我在 CapSense 按钮触发时是否有可能重新配置 I/O 的操作?

我想使用一个 CapSense 按钮并启用/禁用电路上的另一个 IC。

这意味着,如果按下 CapSense 按钮,输出将永久保持高电平,而如果再次按下,输出将变为低电平。

我正在使用CYUSBS236开发工具包。

2025-05-29 07:58:04

如题,ESP8266每次启动都要重新配置热点名称、加密方式、密钥、IP、端口号等这些信息吗?哪位大侠来给讲解一下!

2019-04-10 06:35:50

Virtex-5 - 通过DRP动态重新配置DCM的地址和值是什么?我有PLL的电子表格,但没有DCM的电子表格。

2020-06-16 16:25:11

目前,我的程序实现了RTC的配置,但是因为担心实时时钟的精度无法满足要求,想再程序中加入一些功能,能够通过上位机重新设置RTC,或者进行校准,刚刚尝试过第一种方法,可惜没有实现,直接调用了设置函数,但是调试过程中发现RTC_TimeSet()返回的是错误,请问在程序中重新配置RTC应如何实现?

2018-10-10 08:44:08

想通过EDMA来访问EMIFA,请问此时的EMIFA的时序是否要重新配置,以适应EDMA和CPU的速度?期待ing……

2018-08-07 07:12:02

需要上拉、下拉或漏极开路。

上图是 GIO 的方框图,所有通用的 IO口都可以根据需要配置成输入 / 输出 或中断方式,当然也可以根据需要选择内部上拉或下拉,如果使能I/O口中断, 则一旦有设定的边沿

2018-05-25 01:18:28

嗨,我正在进行部分重新配置,我测试了一个不规则形状的分区(例如L形),在映射步骤中,实现失败并出现此错误:PhysDesignRules:0- 组件:microblaze_0

2019-01-25 10:36:59

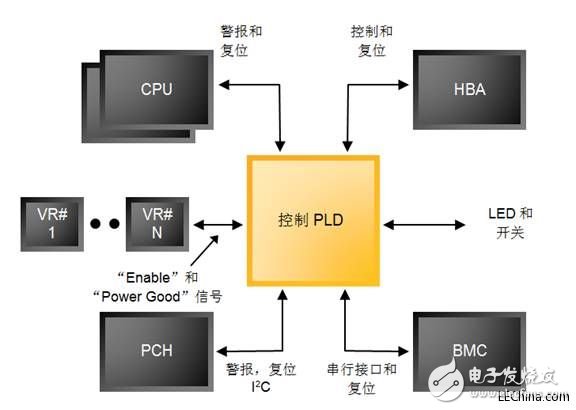

功能。这些是当今面向大逻辑单元、DSP块和闪存的PLD的完美应用。 大多数消费电子产品都提供了用于控制和配置的I2C接口。有很多参考设计可以下载和重用。为Altera的PLD产品系列优化的VHDL语言

2019-05-14 07:00:12

使用LabVIEW FPGA 模块和可重新配置I/O 设备开发测量与控制应用通过使用LabVIEW FPGA 模块和可重新配置I/O(RIO)硬件,NI 为您提供了一种直观可用的解决方案,它可以将

2009-07-23 08:15:57

用单片机配置FPGA—PLD设计技巧

Configuration/Program Method for Altera Device

Configure the FLEX Device

You

2008-09-11 09:36:56 23

23 使用 LabVIEW FPGA 模块和可重新配置I/O 设备开发测量与控制应用通过使用LabVIEW FPGA 模块和可重新配置I/O(RIO)硬件,NI 为您提供了一种直观可用的解决方案,它可以将FPGA技术的灵活性

2009-07-23 08:09:28 68

68 本文主要介绍了51单片机的内部中断以及I/O键盘的应用。

2016-03-25 13:49:45 7

7 uClinux下中断驱动的I_O设备驱动开发

2017-01-24 17:21:04 9

9 机器和模块的快速安装以及不中断运行情况下的任意重新配置和操作能力是生产灵活性的核心要求之一。Han® ES Press HMC系列让浩亭打造出能够无需工具即可进行快速安装并且极为可靠耐用的接口,其至少可承受10000次插拔操作。

2018-12-06 15:51:09 1601

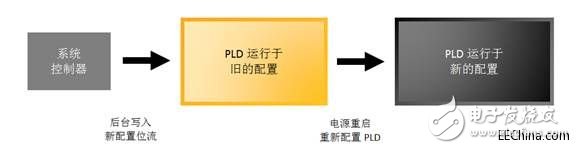

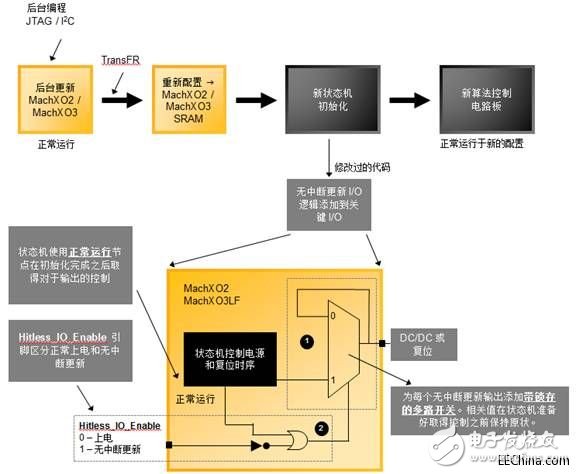

1601 关键词:PLD , SRAM , 可重配置电路 由于SRAM的可重配置PLD(可编程逻辑器件)的出现,为系统设计者动态改变运行电路中PLD的逻辑功能创造了条件。PLD使用SRAM单元来保存字的配置

2019-02-23 14:30:01 1388

1388

CompactRIO是美国国家仪器(NI)公司生产的一款可重新配置的嵌入式测控系统。CompactRIO系统拥有坚固的硬件架构,其中包含:I/O模块、带有可重新配置的现场可编程门阵列(FPGA

2020-07-01 08:20:00 3785

3785 瑞士洛桑联邦理工学院光子系统实验室的研究人员发明了一种无需外部设备就能重新配置微波光子的滤波器。这为更紧凑、更环保的滤波器铺平了道路,这些滤波器将更实用、更便宜。潜在的应用包括检测和通信系统。

2020-09-08 15:44:42 1608

1608

以色列一所大学的仿生和医疗机器人实验室的研究人员设计了一种可重新配置的机器人RTCR,这种机器人能够利用最小数量的驱动器在空中跟踪爬台阶和克服障碍。RTCR(可重构连续跟踪机器人)可以通过一系列链接和一个单驱动器改变其整个身体的形状,并利用它在前进过程中建立自己的轨道。

2020-11-05 14:23:28 2563

2563 导言:这篇为PCIe要提及的时钟类型作个小铺垫,可以大致作一个了解,想深入了解可以参考更加细致的文献。 三种基本的I/O架构 1• 通用时钟(Common Clock) 2• 前向时钟

2021-04-04 11:53:00 7151

7151

第一:STM32 I/O 口的配置1-.1:I/O可以配置成8中不同的模式,输入四种:模拟输入,输入上拉,输入下拉,输入浮空; 输出四种:推挽输出,开漏输出,推挽式复用输出,开漏复用输出。具体的配置

2021-11-15 12:51:04 17

17 单片机I/O设备的控制方式主要有三种:程序循环检测、中断驱动和直接内存访问。

2021-11-23 17:51:42 3

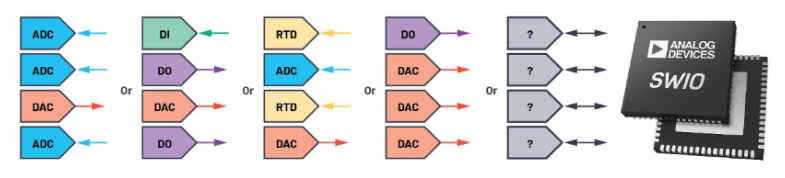

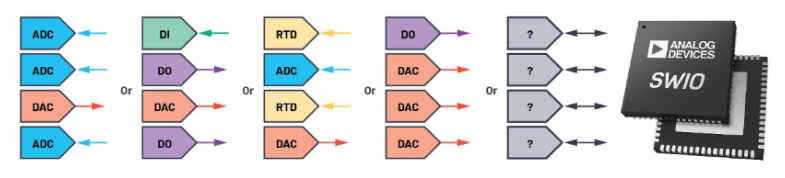

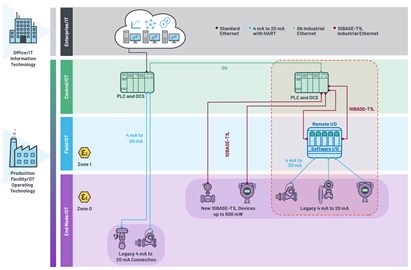

3 借助软件可配置 I/O,制造商可以开发一个平台来替换多个老化的固定功能 I/O 模块。此外,他们可以在多个终端应用程序中使用这项技术,其中 I/O 会随着每次安装而动态变化。

2022-06-02 10:08:08 2139

2139

了解DSQC652输入输出模块结构和接口连接说明;掌握在RobotStudio的虚拟示教器中进行I/O配置方法;掌握在RobotStudio的I/0系统中进行I/0配置方法。

2022-08-24 09:33:38 9

9 真是一段漫长的旅程:从阿基米德到可重新配置仪表板

2022-11-03 08:04:40 0

0 具有中断输出和配置寄存器的低压 16 位 I²C 和 SMBus I/O 扩展器-NCA9555

2023-02-07 20:12:46 3

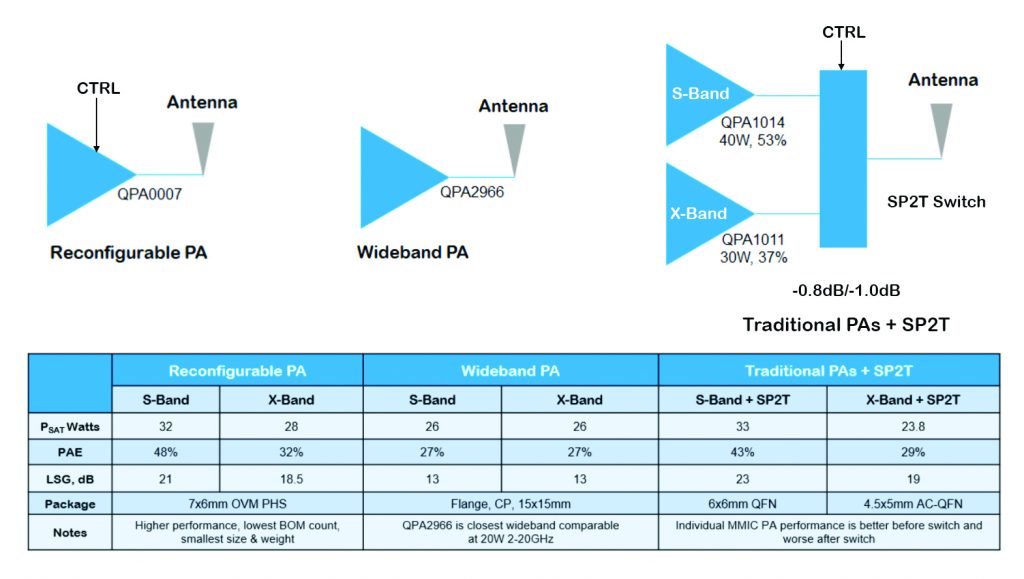

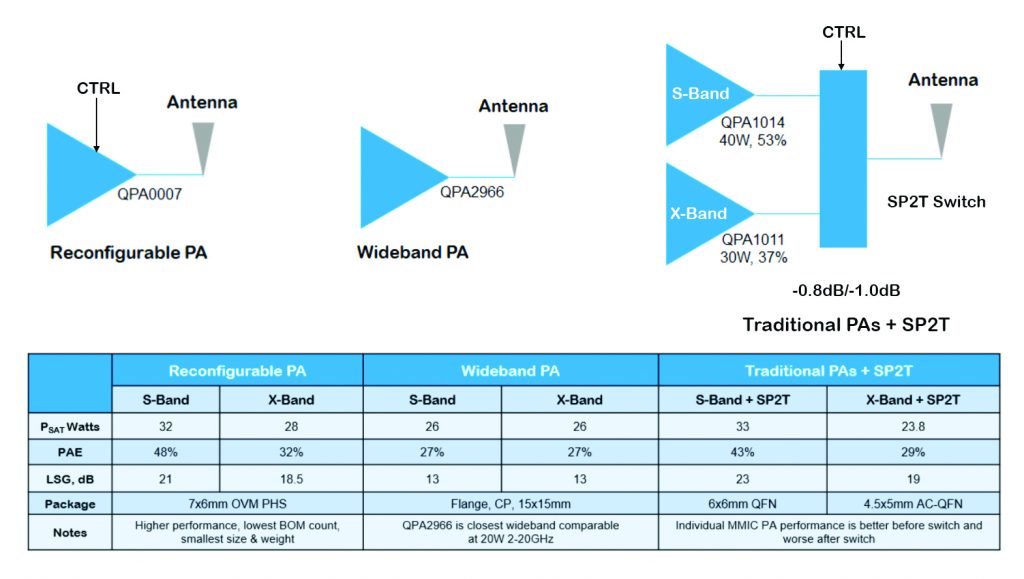

3 本文首次展示了一种基于多频段发射器设计的可靠商用大功率放大器,该放大器采用了 Charles Campbell 演示的可重新配置的 PA 专利技术 [2,3,4]。可重新配置的 PA 采用可根据每个相关频段的控制位设置重新配置的单输入和单输出匹配网络。

2023-02-22 11:50:27 1235

1235

来覆盖不同的传感器和执行器。然而,固定功能模块中的某些通道可能未被使用,成为多余通道。软件可配置I/O模块支持有效使用I/O系统中的所有通道。拥挤的布线可能导致传感器和执行器与这些固定功能I/O的连接不正确。调试和排除这些故障非常耗时,并且需要手动将负载重新连接到I/O通道。

2023-06-13 18:00:11 1312

1312

作者: Kenton Williston 曾几何时,模拟 I/O 就是最专业、功能最固定的硬件。例如,电流驱动器和电压传感器是完全不同的零件,试图颠倒其角色可谓是荒谬至极。 软件可配置模拟 I/O

2024-05-05 11:10:00 1715

1715

电子发烧友网站提供《TCA9535具有中断输出和配置寄存器的低电压16位I2C和SMBus低功耗I/O扩展器数据表 .pdf》资料免费下载

2024-06-21 09:41:07 0

0 电子发烧友网站提供《具有中断输出和配置寄存器的 PCA9535 远程 16位I2C和SMBus I/O扩展器数据表.pdf》资料免费下载

2024-06-25 11:20:35 0

0 电子发烧友网站提供《具有中断输出、复位和配置寄存器的PCA9539远程16位I2C 和SMBus 低功耗 I/O 扩展器数据表.pdf》资料免费下载

2024-06-25 11:21:48 0

0 电子发烧友网站提供《具有中断输出和配置寄存器的 PCA9534A远程8位I2C和SMBus 低功耗 I/O 扩展器数据表.pdf》资料免费下载

2024-06-25 11:22:45 0

0 电子发烧友网站提供《具有中断输出和配置寄存器的PCA9555远程16位I2C和 SMBus I/O扩展器数据表.pdf》资料免费下载

2024-06-25 09:31:04 0

0 电子发烧友网站提供《PCA9554A具有中断输出和配置寄存器的远程8位I2C和SMBus I/O扩展器数据表.pdf》资料免费下载

2024-06-28 11:03:43 0

0 电子发烧友网站提供《具有中断输出和配置寄存器的PCA9554远程8位I2C和SMBus I/O扩展器数据表.pdf》资料免费下载

2024-06-28 11:04:35 1

1 电子发烧友网站提供《TCA9554A具有中断输出和配置寄存器的低压8位I2C和SMBus低功耗I/O扩展器数据表.pdf》资料免费下载

2024-07-02 10:24:03 0

0 电子发烧友网站提供《TCA6424A低电压24位I2C和SMBus I/O扩展器具有中断输出、复位和配置寄存器数据表.pdf》资料免费下载

2024-07-03 12:46:41 1

1 电子发烧友网站提供《TCA6408A-Q1具有中断输出的低电压8位I2C和SMBus I/O扩展器数据表.pdf》资料免费下载

2024-07-03 11:47:36 0

0 电子发烧友网站提供《NCA9555带中断的16位I2C总线I/O端口英文手册.pdf》资料免费下载

2024-07-03 17:26:44 2

2 电子发烧友网站提供《区域架构和 MCU I/O 扩展.pdf》资料免费下载

2024-09-09 10:51:20 0

0 FPGA可以反复的重新配置,这就意味着设计者可以不断的反复的下载设计的逻辑做验证。如果出现错误或者需要升级,只需要修改设计,重新下载设计逻辑电路即可。FPGA虽然有重新配置的优势,带来的不利就是它

2024-10-24 18:13:41 1988

1988

电子发烧友App

电子发烧友App

评论