广义的来说,FPGA的配置包括直接使用下载电缆对FPGA器件进行编程、对外部EEPROM和FLASH进行编程、使用MPU对FPGA器件进行编程、外部EEPROM和FLASH对器件进行编程等。

2016-10-26 10:58:27 12458

12458 在需要多个FPGA芯片的应用中,如果JTAG链上所有FPGA采用相同配置,可以通过“成组”加载方式同时加载;

2023-02-20 10:18:27 8049

8049

从制造的角度来讲,FPGA测试是指对FPGA器件内部的逻辑块、可编程互联线、输入输出块等资源的检测。完整的FPGA测试包括两步,一是配置FPGA、然后是测试FPGA,配置FPGA是指将FPGA通过将配

2011-10-12 15:16:25 1928

1928

通过FPGA的多重配置可以有效地精简控制结构的设计,同时可以用逻辑资源较少的FPGA器件实现需要很大资源才能实现的程序。以Virtex5系列开发板和配置存储器SPI FLASH为基础,从硬件电路

2014-01-24 14:17:22 16046

16046

FPGA配置方式灵活多样,根据芯片是否能够自己主动加载配置数据分为主模式、从模式以及JTAG模式。典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为

2022-09-22 09:13:59 4864

4864 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 2392

2392 我们所说的FPGA配置电路,一方面要完成从PC上把bit文件下载到FPGA或存储器的任务,另一方面则要完成FPGA上电启动时加载配置数据的任务。

2023-06-10 10:09:52 1107

1107

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 4234

4234 使用raspi-config可以十分方便的配置一些树莓派系统常用配置,下文介绍其中一些常用的配置

2023-09-08 17:12:22 2461

2461

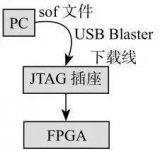

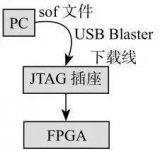

FPGA器件有哪些配置下载方式?下载电缆ByteBlaster原理及配置方式

2021-04-15 06:26:33

RPD。 5.HEX文件HEX文件不能直接对FPGA进行配置,只能通过第三方编程器对HEX进行解析后把数据区烧写到EPCS中。 6.JAM文件JAM文件时用来存储器件变成信息的ASCII文本文件

2012-04-25 15:48:52

设计和制造技术的快速发展,JTAG越来越多的被用于电路的边界扫描测试和可编程芯片的在线系统编程。(特权同学,版权所有)FPGA器件都支持JTAG进行在线配置,JTAG边界扫描的基本原理如图3.7所示

2019-01-30 02:34:52

jtag调试时,fpga能识别到器件,但是下载程序失败,针对这种情况,想问下各位:1、能识别到器件,说明fpga配置电路的哪些部分是正常的2、我描述的这种情况可能是由于什么原因导致的?

2014-05-04 10:50:29

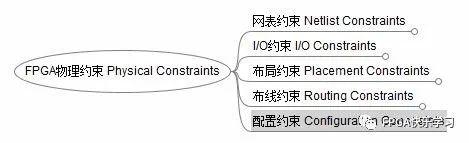

的文件qxp中,配和qsf文件中的粗略配置信息一起完成增量编译。 4. 核心频率约束+时序例外约束+I/O约束+LogicLock LogicLock是在FPGA器件底层进行的布局约束

2016-06-02 15:54:04

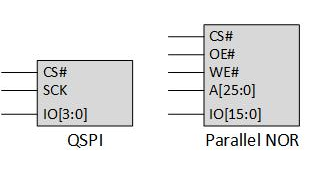

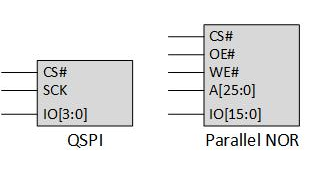

NOR闪存已作为FPGA(现场可编程门列阵)的配置器件被广泛部署。其为FPGA带来的低延迟和高数据吞吐量特性使得FPGA在工业、通信和汽车ADAS(高级驾驶辅助系统)等应用中得到广泛采用。汽车场景中

2021-09-03 07:00:00

的配置已经满足了大部分的使用场景,本文分享总结了几个比较重要的配置参数,主要是针对producer端的配置,希望对你有所帮助。

2020-11-04 08:10:24

今天给大侠带来Xilinx FPGA编程技巧之常用时序约束详解,话不多说,上货。

基本的约束方法为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为

2024-04-12 17:39:04

今天给大侠带来Xilinx FPGA编程技巧之常用时序约束详解,话不多说,上货。

基本的约束方法

为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为

2024-05-06 15:51:23

本篇主要说一下FPGA的配置方式,让我们来了解一下除了JTAG,还有其他哪几种方式。FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式

2023-04-24 15:34:27

FPGA器件都是基于RAM结构的,当然了,也有基于Flash结构的,但RAM结构的是主流,也是我们讨论的重点。而RAM是易失存储器,在掉电后保存在上面的数据就丢失了,重新上电后需要再次加载配置数据。因此

2016-08-10 17:03:57

/s/1i5LMUUD AS配置方式由FPGA器件引导配置操作过程,它控制着外部存储器及其初始化过程,EPCS系列配置芯片如EPCS1、EPCS4配置器件专供AS模式。使用Altera串行配置器件来完成

2018-03-05 16:30:35

NOR闪存已作为FPGA(现场可编程门列阵)的配置器件被广泛部署。其为FPGA带来的低延迟和高数据吞吐量特性使得FPGA在工业、通信和汽车ADAS(高级驾驶辅助系统)等应用中得到广泛采用。汽车场景中

2021-05-26 07:00:00

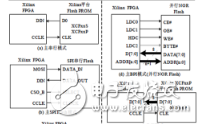

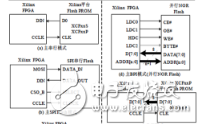

不管Xilinx还是Altera,FPGA的配置模式或者方法多样,尤其是Altera器件,什么AS模式、PS模式、FPP模式、AP模式等等。一般逻辑设计者可能不会关心到硬件的设计,但是FPGA的硬件

2015-01-28 10:27:03

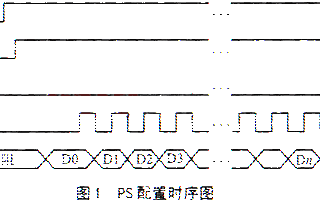

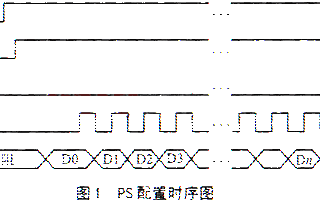

介绍一种在嵌入式系统中使用微处理器被动串行配置方式实现对FPGA配置的方案,将系统程序及配置文件存在系统Flash 中,利用微处理器的I/O 口产生配置时序,省去配置器件;讨论FPG

2009-04-15 11:02:53 13

13 介绍如何用PowerPC860(MPC860)进行FPGA(Xilinx 的Virtex-II 系列)的配置;给出进行FPGA 配置所需的详细时序图和原理图。本配置基本原理对其它FPGA 的配置也适用。

2009-04-16 14:11:36 18

18 通过说明FPGA 的各种配置方式及各种配置文件的使用,重点探讨了在嵌入式系统中使用FPGA 的软硬件设计。使用微处理器在线配置FPGA 时,需要将存储在Flash 中的配置文件,通过微处

2009-09-16 10:52:02 10

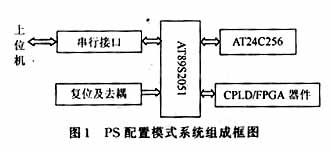

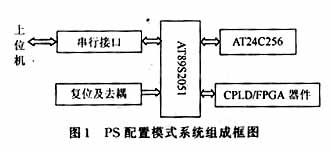

10 基于单片机的CPLD/FPGA被动串行下载配置的实现:介绍采用AT89S2051单片机配合串行E2PROM存储器,实现CPLD/FPGA器件的被动串行模式的下载配置,阐述了其原理及软硬件设计。 &nb

2009-10-29 21:57:22 19

19 摘要:本文讨论了Cyclone系列器件的不同配置方法,提出一种单片机结合FLASH存储器的被动串行配置方案。关键词:FPGA;FLASH;PS;Cyclone

2010-08-13 12:04:09 67

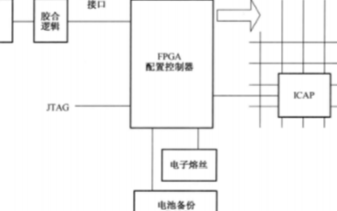

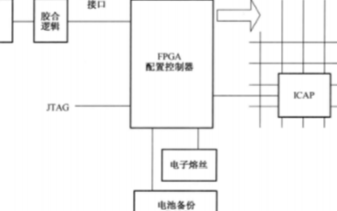

67 FPGA的全局动态可重配置技术主要是指对运行中的FPGA器件的全部逻辑资源实现在系统的功能变换,从而实现硬件的时分复用。提出了一种基于System ACE的全局动态可重配置设计方法,

2011-01-04 17:06:01 54

54 摘要:介绍基于SRAM LUT结构的FPGA器件的上电配置方式;着重介绍采用计算机串口下载配置数据的方法和AT89C2051单片机、串行EEPROM组成的串行配置系统的设计方法及实现

2006-03-13 19:36:49 658

658 实验三、交换机的常用配置命令

一. 实验原理1.1 交换机的用户界面交换机有以下几个常见命令视图:(1

2008-09-24 13:35:20 3501

3501

摘要: 介绍基于SRAM LUT结构的FPGA器件的上电配置方式;着重介绍采用计算机串口下载配置数据的方法和AT89C2051单片机、串行EEPROM组成的串行配置系统的设计方法及

2009-06-20 10:57:26 1326

1326

一、 配置方式

ALTERA CPLD器件的配置方式主要分为两大类:主动配置方式和被动方式。主动配置方式由CPLD器件引导配置操作过程,它控制着外部存储器和

2009-06-20 10:58:14 2674

2674 摘要:介绍如何用PowerPC860(MPC860)进行FPGA(Xilinx的Virtex-II系列)的配置;给出进行FPGA配置所需的详细时序图和原理图。本配置基本原理对其它FPGA的配置也适用。

2009-06-20 11:02:38 1182

1182

FPGA 重复配置和测试的实现

从制造的角度来讲,FPGA测试是指对FPGA器件内部的逻辑块、可编程互联线、输入输出块等资源的检测。完整的FPGA测试包括

2009-09-03 11:17:08 725

725

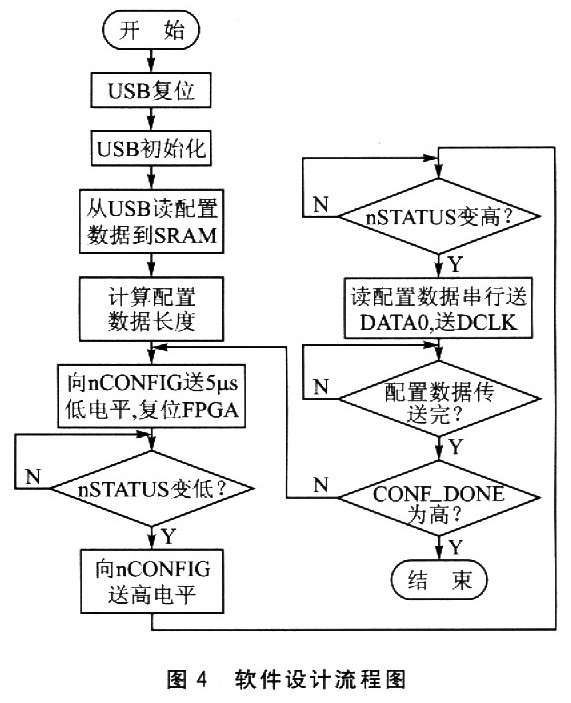

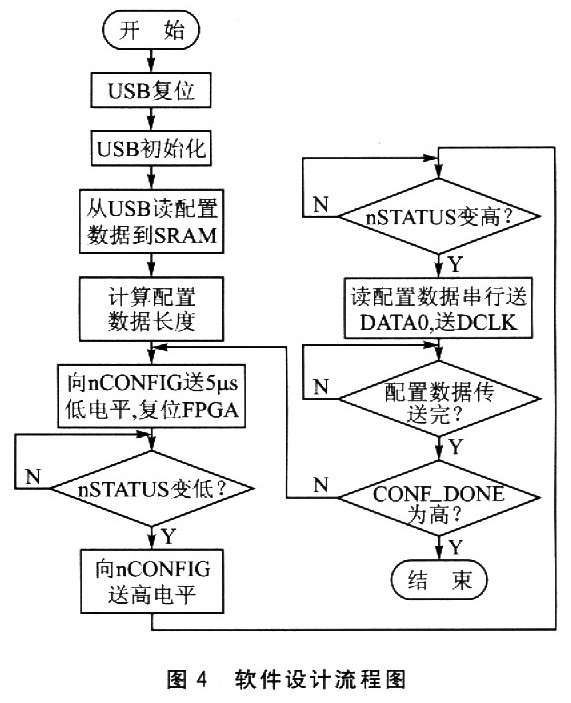

基于U盘和单片机的FPGA配置

引 言FPGA广泛应用在电子通信领域,其安全性引起了注意,本文针对安全配置提出了解决方案。

现场可编程门阵列FPGA(F

2010-01-14 09:27:24 1870

1870

FPGA重复配置和测试的实现

从制造的角度来讲,FPGA测试是指对FPGA器件内部的逻辑块、可编程互联线、输入输出块等资源的检测。完整的FPGA测试包括两步,一是配置FPGA

2010-01-26 09:39:56 690

690

采用VC++程序的FPGA重配置设计方案利用现场可编程逻辑器件FPGA的多次可编程配置特点,通过重新下载存储于存储器的不同系统数据

2010-04-14 15:14:57 767

767

摘要:文中详述了FPGA被动串行配置方式的时序,给出配置流程图及实现的程序代码,并通过实例验证了该方法的优越

2010-07-21 14:48:48 1692

1692

本文介绍了通过处理机用CPLD和Flash实现FPGA配置文件下载更新的方法。与传统的JTAG或PROM串行下载配置方法相比,此方法具有更新配置文件灵活方便、易于操作、适用于大容量FPGA下载的特点

2018-10-25 05:51:00 10535

10535

本章将首先介绍FPGA配置方式和配置过程,然后简单介绍了配置芯片、配置文件的种类以及配置电路设计要点,本章最后讲述了配置文件下载、Flash编程等方面的内容,其中Flash编程包括

2011-03-22 10:53:46 805

805 SPI方式FPGA配置和SPI flash编程

2011-05-16 18:01:02 166

166 本文结合具体应用需求,介绍了利用嵌入式CPU Leon3软核处理器对Virtex系列FPGA的配置进行控制的方法。此系统能够实现FPGA配置数据的重构,并且减少了外围CPU和CPLD器件的使用,具有很好

2011-07-04 10:13:41 3895

3895

FPGA有多种配置模式:并行主模式为一片FPGA加一片EPROM的方式;主从模式可以支持一片PROM编程多片FPGA;串行模式可以采用串行PROM编程FPGA;外设模式可以将FPGA作为微处理器的外设,由微处理

2011-09-08 17:50:27 2183

2183 基于SD卡的FPGA配置,本文给出了对Virtex FPGA 进行配置的情 况,该方案也可以适用于Spartan 系列FPGA。

2011-12-13 10:02:42 6675

6675

本文着重介绍了 Xilinx Platform Flash PROM 如何帮助系统和电路板设计人员简化 FPGA 配置设计。用于配置 FPGA 的可选解决方案有很多,但它们通常都需要大量的前期设计工作和时间。Platform

2012-01-17 17:33:20 36

36 CycloneII系列器件配置手册.

2012-04-01 15:08:36 8

8 本文着重介绍了 Xilinx Platform Flash PROM 如何帮助系统和电路板设计人员简化 FPGA 配置设计。用于配置 FPGA 的可选解决方案有很多,但它们通常都需要大量的前期设计工作和时间。Platform

2013-03-14 15:18:22 64

64 FPGA Cyclone器件中PLL的配置方法

2016-02-23 11:04:13 5

5 Xilinx FPGA编程技巧常用时序约束介绍,具体的跟随小编一起来了解一下。

2018-07-14 07:18:00 5223

5223

常用的有如下三种 配置文件:

Sof: SRAM Object File ; JTAG模式下,直接下载到FPGA中,

jic: JTAG Indirect Configuration

2017-09-19 16:49:06 12

12 基于DSP的FPGA配置方法研究与实现

2017-10-19 16:15:19 36

36 摘要: ALTERA公司SRAM工艺可编程器件应用广泛,专用配置器件比较昂贵。在具有微处理器的系统中,使用微处理器系统的存储器来存储配置数据,并通过微处理器配置FPGA,这种方法几乎不增加

2017-11-06 11:10:48 1

1 通过SELECTMAP32接口配置和回读XILINX公司生产的V5系列SRAM型FPGA,被配置的FPGA以下简称DUT,产生配置时序的FPGA简称配置FPGA。首先硬件上应将M[2:0]接成110

2017-11-17 10:16:01 10667

10667 FPGA配置方式灵活多样,根据芯片是否能够自己主动加载配置数据分为主模式、从模式以及JTAG模式。典型的主模式都是加载片外非易失(断电不丢数据)性存储器中的配置比特流,配置所需的时钟信号(称为

2017-11-22 09:24:02 7490

7490 从制造的角度来讲,FPGA测试是指对FPGA器件内部的逻辑块、可编程互联线、输入输出块等资源的检测。完整的FPGA测试包括两步,一是配置FPGA、然后是测试FPGA,配置FPGA是指将FPGA通过将

2017-11-24 20:55:53 8774

8774

FPGA配置方式灵活多样,根据芯片是否能够自己主动加载配置数据分为主模式、从模式以及JTAG模式。典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为

2017-11-26 08:12:51 8993

8993

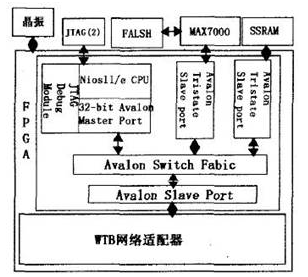

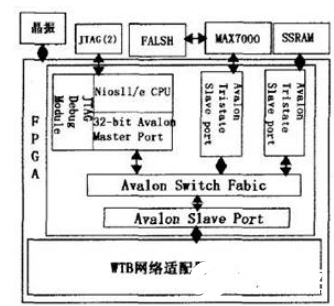

外电路编程FPGA或是编程Flash器件(包括EPCS和Flash),然后控制FPGA的配置复位引脚来复位整个FPGA,最后FPGA采用主串方式进行自我配置。另一种是,通过FPGA中的Nios CPU或是

2017-12-13 13:58:10 26639

26639

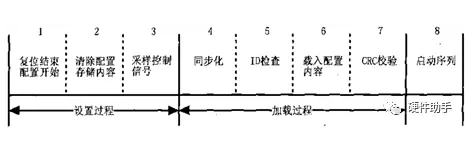

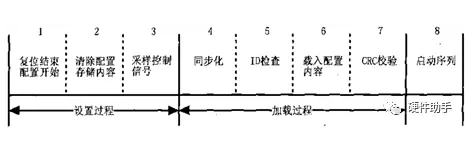

尽管FPGA的配置模式各不相同,但整个配置过程中FPGA的工作流程是一致的,分为三个部分:设置、加载、启动。

2018-08-01 15:32:54 5330

5330

本系统可用于配置所有ALTERA公司生产的基于SRAM架构的CPLD器件和XILINX公司生产的基于SRAM架构的FPGA器件以及其他主流器件制造公司生产的基于SRAM架构的器件,具有很强的通用性。由于该电路使用的元器件非常少,也可以将其制作成面积很小、便于携带的通用下载配置板使用。

2018-10-08 09:21:00 3628

3628

FPGA有多种配置/加载方式。粗略可以分为主动和被动两种。主动加载是指由FPGA控制配置流程,被动加载是指FPGA仅仅被动接收配置数据。

2018-10-05 10:12:00 19146

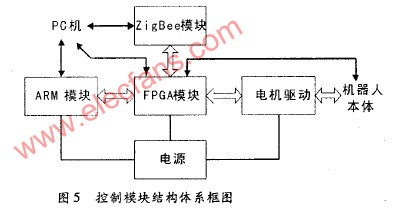

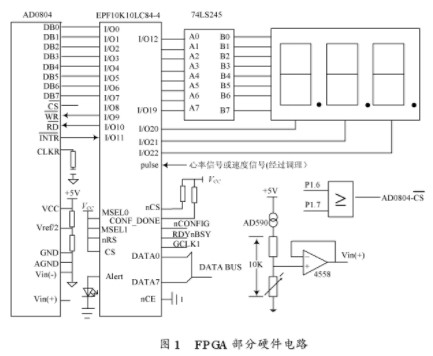

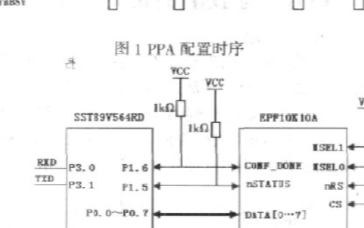

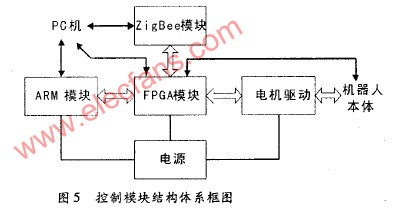

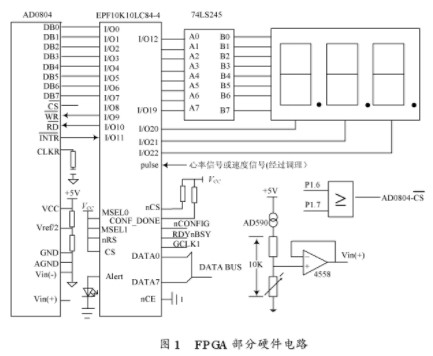

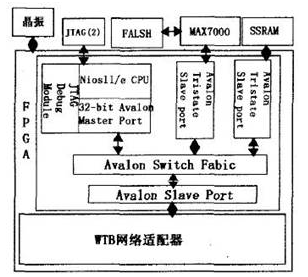

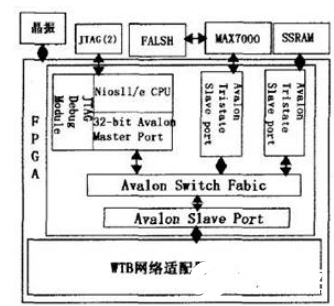

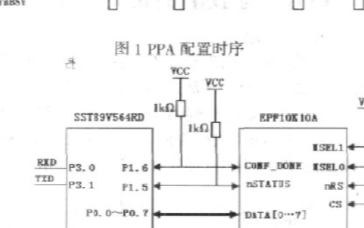

19146 根据课题要求,设计FPGA部分硬件电路如图1所示。FPGA芯片选用Altera公司的中档器件FLEX-EPF10K10LC84-4,他是基于SRAM LUT结构的FPGA器件。根据传送数据的方式

2019-08-21 08:01:00 6288

6288

本文档的主要内容详细介绍的是Linux教程之网络配置文件与配置方法及常用网络操作命令详细资料免费下载主要目标是1.掌握网络配置文件的配置方法2.学会使用常用网络操作命令

2018-11-07 11:49:53 9

9 Altera FPGA支持AS,PS,JTAG等几种较常见的配置方法。 当为AS配置模式时,FPGA为主设备,加载外部FLASH中的数据至内部RAM中运行。当为PS配置模式时,FPGA为从设备,外部

2018-11-18 18:05:01 831

831 现场可编程门阵列(FPGA,Field Programmable Gate Array)是一种高密度可编程逻辑器件,其逻辑功能是通过把设计生成的数据文件配置进芯片内部的静态配置数据存储器(SRAM

2019-01-04 14:15:02 1147

1147

NOR闪存已作为FPGA(现场可编程门列阵)的配置器件被广泛部署。其为FPGA带来的低延迟和高数据吞吐量特性使得FPGA在工业、通信和汽车ADAS(高级驾驶辅助系统)等应用中得到广泛采用。汽车场景中

2019-02-21 17:01:30 5339

5339

NOR闪存已作为FPGA(现场可编程门列阵)的配置器件被广泛部署。其为FPGA带来的低延迟和高数据吞吐量特性使得FPGA在工业、通信和汽车ADAS(高级驾驶辅助系统)等应用中得到广泛采用。汽车场景中

2019-02-23 10:43:59 3790

3790

本文档详细介绍的是FPGA教程之CPLD和FPGA的配置与下载的详细资料说明主要内容包括了:一、CPLD/FPGA器件的配置,二、MAX系列非易失性器件的下载配置,三、FLEX/ACEX系列FPGA的下载配置,四、ALTERA的编程文件

2019-02-28 09:56:18 20

20 FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。

2019-03-07 16:07:01 4224

4224 现场可编程门阵列(FPGA,Field Programmable Gate Array)是一种高密度可编程逻辑器件,其逻辑功能是通过把设计生成的数据文件配置进芯片内部的静态配置数据存储器(SRAM

2020-01-21 17:10:00 1187

1187

Spartan-6 FPGA 利用CCL 支持布线线路与逻辑单元之间的可配置互联功能。Spartan-6 FPGA 是易失性器件- 电源移除时,不能保留原有配置。为了配置Spartan-6

2020-01-10 15:28:51 28

28 FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列:如

2020-07-09 10:53:09 8920

8920 目前很多产品都广泛用了FPGA ,虽然品种不同, 但编程方式几乎都一样: 利用专用的EPROM 对FPGA 进行配置。专用的EPROM 价格不便宜,且大不跟上都是一次性OPT 方式编程。一旦更改

2020-08-13 17:43:23 2

2 在当今变化的市场环境中,产品是否便于现场升级、便于灵活使用,已成为产品进入市场的关键因素。而基于 SRAM结构的 FPGA器件的出现,为系统设计者动态改变运行电路中的逻辑功能创造了条件,也为现场升级

2020-08-19 16:26:14 2478

2478

介绍一种在嵌放式系统中使用微处理器被动串行配置方式实现对FPGA配置的方案,将系统程序及配置文件存在系统Flash中,利用微处理器的I/O口产生配置时序,省去配置器件;讨论FPGA的各种配置方式

2020-09-29 17:05:59 1490

1490

赛灵思公司的FPGA芯片具有IEEE 1149.1/1532协议所规定的JTAG接口,只要FPGA上电,不论模式选择管脚M[1:0] 的电平,都可用采用该配置模式。JTAG模式不需要额外的掉电非易失

2020-12-31 17:30:55 13

13 说到FPGA时序约束的流程,不同的公司可能有些不一样。反正条条大路通罗马,找到一种适合自己的就行了。从系统上来看,同步时序约束可以分为系统同步与源同步两大类。简单点来说,系统同步是指FPGA与外部

2021-01-11 17:46:32 14

14 方式 1、主动配置方式(AS) 2、被动配置方式(PS) 3、JTAG方式 1、AS模式(active serial configuration mode):FPGA器件每次上电时作为控制器,由

2021-03-12 16:26:58 14350

14350

FPGA 主动方式:由 FPGA来主动输出控制和同步信号给 FPGA的串行配置芯片(EPCS系列) ,配置芯片收到命令后,把配置数据发给 FPGA,完成配 置过程;在 AS模式下,FPGA必须

2021-04-06 15:33:02 8

8 在需要进行大量数据并行计算的算法(如云计算、机器学习算法、人工智能算法等)中,FPGA作为一种提升性能的重要技术手段,得到了广泛的应用。FPGA配置方式中,需要在存储器中读取配置数据,然后将其写入

2021-05-31 15:51:42 10

10 所有现代FPGA的配置分为两类:基于SRAM的和基于非易失性的。其中,前者使用外部存储器来配置FPGA内的SRAM后者只配置一次。 Lattice和Actel的FPGA使用称为反熔丝的非易失性配置

2021-07-02 16:01:40 4459

4459

FPGA_ASIC-DSP和FPGA共用FLASH进行配置的方法(哪些专业适合嵌入式开发)-该文档为FPGA_ASIC-DSP和FPGA共用FLASH进行配置的方法讲解文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 11:16:55 22

22 广义的来说,FPGA的配置包括直接使用下载电缆对FPGA器件进行编程、对外部EEPROM和FLASH进行编程、使用MPU对FPGA器件进行编程、外部EEPROM和FLASH对器件进行编程等

2021-09-06 09:41:56 7483

7483 FPGA CPLD可编程逻辑器件的在系统配置方法(深圳市村田电源技术有限公司)-FPGA CPLD可编程逻辑器件的在系统配置方法

2021-09-18 10:51:20 13

13 本文章探讨一下FPGA的时序约束步骤,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-03-16 09:17:19 4001

4001

本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-05-11 10:07:56 4989

4989

尽管FPGA的配置模式各不相同,但整个配置过程中FPGA的工作流程是一致的,分为三个部分:设置、加载、启动。

2022-10-10 14:37:57 2187

2187 的数据送入FPGA器件内,配置完成之后将对器件I/O和 寄存器 进行初始化。初始化完成后,进入用户模式,开始正常工作。 一旦设计者选定了FPGA系统的配置方式,需要将器件上的MSEL引脚设定为固定值,以指示当前所采用的配置方式。 常用的配置方式有: PS配

2022-11-17 12:15:10 2928

2928 芯片设计工程师根据功能,完成RTL设计,添加各种约束,完成综合、Place Route等一系列工作之后,还需要一些配置数据,完成寄存器初始化等内容,才能开始工作。 今天我们一起来聊一聊FPGA的配置

2022-11-21 21:45:10 1998

1998 Lattice和Actel的FPGA使用称为反熔丝的非易失性配置技术,其主要优点是系统设计更加简单、不需要外部存储器和配置控制器、功耗低、成本低和FPGA配置时间更快。最大的缺点在于配置是固定的。

2022-12-01 11:08:45 2130

2130 ForgeFPGA 配置指南

2023-01-09 19:16:34 0

0 Slave(即由外部器件提供配置所需要的时钟信号);另外还可由板上稳定晶振提供时钟信号,经由FPGA的EMCCLK接口,再从CCLK端口送出。

2023-02-16 14:57:59 3170

3170 ForgeFPGA 配置指南

2023-06-30 19:10:57 0

0 点击上方 蓝字 关注我们 NOR闪存已作为FPGA(现场可编程门列阵)的配置器件被广泛部署。其为FPGA带来的低延迟和高数据吞吐量特性使得FPGA在工业、通信和汽车ADAS(高级驾驶辅助系统)等

2023-08-15 13:55:02 1338

1338

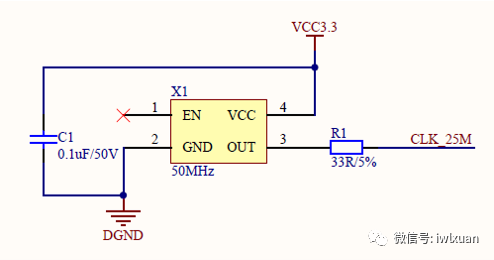

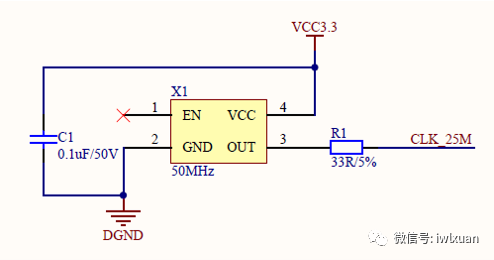

小编在本节介绍FPGA芯片外围电路设计规范和配置过程,篇幅比较大,时钟的设计原则就有17条,伙伴们耐心读一读。

2023-08-15 16:18:11 10883

10883

LOC约束是FPGA设计中最基本的布局约束和综合约束,能够定义基本设计单元在FPGA芯片中的位置,可实现绝对定位、范围定位以及区域定位。

2024-04-26 17:05:05 2426

2426

FPGA可以反复的重新配置,这就意味着设计者可以不断的反复的下载设计的逻辑做验证。如果出现错误或者需要升级,只需要修改设计,重新下载设计逻辑电路即可。FPGA虽然有重新配置的优势,带来的不利就是它

2024-10-24 18:13:41 1988

1988

电子发烧友App

电子发烧友App

评论