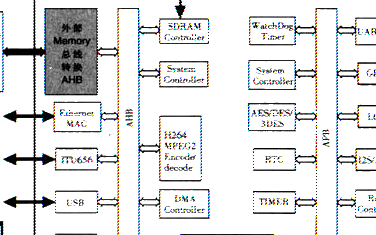

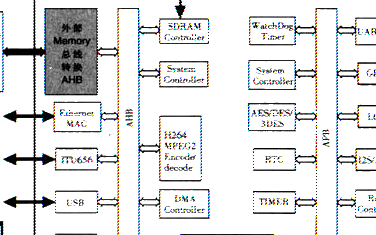

本文介绍了FPGA在实现高清低码流视频编码中的作用以及如何具体实现。目前现状是高清视频720p的码流一般在2Mbps以上,1080p的码流在4Mbps以上,要大幅度降低码流,需要从几个方面考虑。

2013-09-23 13:41:15 2588

2588 ,是近年信道编码领域的研究热点,目前已广泛应用于深空通信、光纤通信、卫星数字视频和音频广播等领域。LDPC码已成为第四代通信系统(4G)强有力的竞争者,而基于LDPC码的编码方案已经被下一代卫星数字视频广播标准DVB-S2采纳。

2020-03-03 10:30:27 2309

2309

的灵活性和较低的差错误码特性,可实现并行操作,译码复杂度低,适合硬件实现,吞吐量大,极具高速译码的潜力,在码长较长的情况下,仍然可以有效译码。 目前常用的信道编码体制有BCH码、RS码、卷积码、Turbo码和LDPC码等。其中BCH码和RS码都属于线性分组码的范畴

2020-11-02 13:56:16 51171

51171

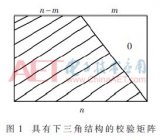

800Mbps准循环LDPC码编码器的FPGA实现引言低密度校验码肠 ,码 由于其接近香农限的纠错性能,使得其成为当前信道编码的研究热点。 码面临的一个关键问题是其较高的编码复杂度和编码时延。 形耐

2012-08-11 11:44:45

,用FPGA实现VGA接口协议可在显示器上显示文字、图型等;★PS/2鼠标,键盘接口:标准鼠标,键盘接口,提供的例程用VHDL实现在数码管上同时显示键盘扫描码和ASCII码,也可结合SOPC编程使其显示

2009-10-23 15:15:24

:配备:★RS-232串口:用于与计算机的数据通信;★VGA接口:直接VGA与显示器对接,用FPGA实现VGA接口协议可在显示器上显示文字、图型等;★PS/2鼠标,键盘接口:标准鼠标,键盘接口,提供

2009-11-02 18:55:54

EP2S60F484I4N特价 EP2S60F484I4N货期EP2S60F484I4N 价格EP2S60F484I4N国宇航芯特价订货EP2S60F484C4N国宇航芯特价订货

2020-01-06 09:07:44

论坛里面的大神们,有没有已经完成LDPC码编译码算法的FPGA实现,本人目前在做这方面的项目,时间比较紧,紧急求购IP核。。

2012-04-16 23:43:28

LDPC码入门资料!

2013-09-21 13:20:43

请教各位大仙,sof和jic文件烧录均正常,pof烧录失败,sof烧录后可正常工作,但jic烧录后无法正常工作,好像没有任何数据输出,这是为什么啊?fpga为EP2S60,配置芯片为epcs64,配置芯片也更换了,问题依旧。

2017-10-14 15:43:00

.基于该结构,本文实现了符合中国数字电视地面传输标准DTMB中LDPC译码器,在SMIC0.18um标准COMS工艺下,芯片面积约为8mm2;在时钟频率50MHz,迭代次数15次,8比特量化的条件下,吞吐率

2010-04-24 09:26:56

型。在高次脉冲编码调制终端设备中广泛使用CMI码作为接口码型,在速率低于8448kb/s的光纤数字传输系统中也被建议作为线路传输码型。

2019-08-29 06:41:21

帧率提升、彩色空间转换等处理。FPGA器件具有可重复编程的灵活性以及并行处理能力,并且随着微处理器、专用硬件单元、DSP算法以及IP核的嵌入使其功能越来越强大。本系统的设计是基于Altera公司的EP2S60系列的开发板,板上集成两片SDRAM存储芯片、视频输入接口和VGA输出接口。

2019-09-29 08:46:06

编码器实现指标分析LDPC码编码器实现编码器方案验证与优缺点分析

2021-04-30 06:08:10

本设计方案采用了一种改进的快速中值滤波算法,成功地在Altera公司的高性能Stratix II EP2S60上实现整个数字红外图像滤波,在保证实时性的同时,使得硬件体积大为缩减,大大降低了成本

2021-04-23 06:00:55

ALTERA的高端FPGA芯片Stratix II EP2S系列EP2S60,板卡使用FPGA用于获取双通道数据采集,实现1路的Base CameraLink输入,一路Base CameraLink

2012-06-13 11:39:49

ALTERA的高端FPGA芯片Stratix II EP2S系列EP2S60,板卡使用FPGA用于获取双通道数据采集,实现1路的Base CameraLink输入,一路Base CameraLink

2012-06-13 12:01:23

LDPC码是近年来发展较快且日趋成熟的一种信道编码方案,因其具有的优越性能和实用价值而被人们认知,但由于随机结构的LDPC码编译码器硬件实现较为复杂,具有的准循环特性QC_LDPC码已成为IEEE802.11n(WiFi)、IEEE802.16e(WiMAX)、(DVB—S2)等众多标准的信道编码方案。

2019-09-30 07:19:45

到了较多应用。中国移动多媒体广播(CMMB)中使用的就是LDPC纠错编码。在CMMB标准中,LDPC码长为9216,可支持1/2和3/4两种码率。作者通过深入分析CMMB中LDPC码校验矩阵的特点,采用

2019-08-23 07:22:50

无线遥控器 常用的编码方式有两种类型,即固定码与滚动码两种,滚动码是固定码的升级换代产品,目前凡有保密性要求的场合,都使用滚动编码方式。下面简单介绍无线遥控器采用滚动码编码方式的优点: 1、保密型

2015-04-04 09:45:10

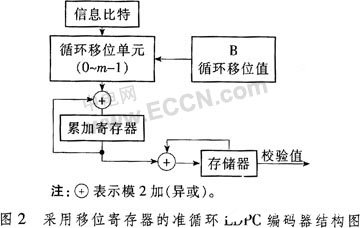

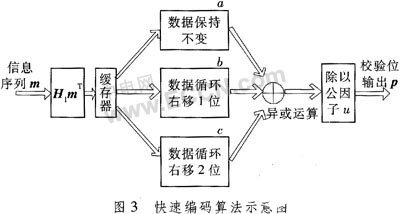

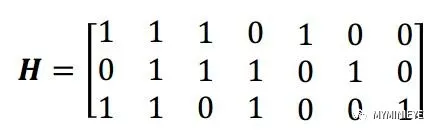

LDPC码的通用编码方法有哪些?准循环LDPC码的快速编码方法是什么?

2021-04-25 07:16:26

Turbo码编码器的FPGA实现Turbo码译码器的FPGA实现Turbo码编译码器的性能有哪些?

2021-05-07 06:06:23

本文在SvstemGenerator中对LDPC码整个编译码系统进行了参数化的硬件实现,并构建了超宽带通信系统LDPC码硬件仿真平台,验证了LDPC码在UWB通信中的优异性能。

2021-06-03 07:01:58

800Mbps准循环LDPC码编码器的FPGA实现CCSDS星载图像压缩模块的FPGA设计与实现FPGA和Nios_软核的语音识别系统的研究RC4加密算法的FPGA设计与实现多FPGA系统中自定义

2012-02-02 17:26:14

最近想用音频编码解码芯片实现快速傅里叶变换的功能,选了一款芯片AD1701用mini开发板。但是FFT功能能不能实现这个问题?现在一直没有找到,也没有看到更多的其它算法,有没有大神给解答一下?

2018-12-20 09:19:48

基FPGA Cyclone II_EP2C5 EP2C8的频率计

基FPGA_Cyclone_II_EP2C5/EP2C8的频率计

功能描述:按4*4键盘上的1,2,3...号按键可依次测出 25000000Hz ,12500000Hz ....的分

2008-11-30 12:17:01 87

87 针对LDPC码与RS码的串行级联结构,提出了一种基于Chase的联合迭代译码方法。软入软出的RS译码器与LDPC译码器之间经过多次信息传递,性能可以逼近最大似然译码。模拟结果显示:

2009-05-12 21:47:25 22

22 本文基于Altera的FPGA(StatixⅡ-EP2S30F484C3)架构,实现了码率为1/2,帧长为1008bits的规则(3,6)LDPC码译码器。所采用的最小-和算法相对于传统的和-积算法在不损失译码性能的前提下,

2009-06-06 14:12:20 31

31 LDPC原理与应用的主要内容:

第一章 绪论第二章 信道编码基础第三章 LDPC码概述第四章 LDPC码译码第五章 结构LDPC码的编码构造第六章 各种编码方法设计的LDPC码

2009-07-24 15:07:06 0

0 An Introduction to LDPC Codeslow_power VLSI Decoder architectures for ldpc codesLow-Density

2009-07-24 15:45:40 0

0 VSPC-LDPC串行级联码的结构与性能分析:提出了一种基于LDPC码和纵向单奇偶校验(VSPC)乘积码的级联编码方法。该方法利用LDPC码能否成功地译码的判定信息以取代常规乘积码中的横向校

2009-10-20 18:01:32 15

15 该文提出了一种可分解的码率兼容LDPC 码的构造方法, 该方法构造所得到的一个高码率LDPC 码的校验矩阵中包含有若干低码率LDPC 码的校验矩阵,而且一个高码率的LDPC 码又可以分解成

2009-11-19 16:47:41 14

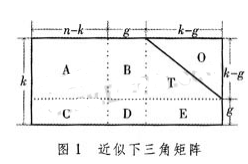

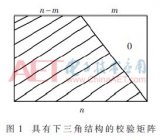

14 本文以CCSDS 推荐的7/8 码率LDPC 码为例,提出了一种适于高码率LDPC 码译码器的硬件结构优化方法。高码率的LDPC 码通常也伴随着行重与列重的比例较高的问题。本方法是在拆分校验矩

2009-11-25 15:21:25 26

26 该文从译码速率、硬件实现的复杂度和误码率3 个方面对比研究了两种典型的高速译码算法:Turbo 型和积算法与并行加权比特翻转算法。以准循环LDPC 码为对象,给出了Turbo 型和积算

2009-11-25 15:26:58 9

9 简述了LDPC码的研究现状及编码方法。在此基础上分析了目前常用的编码实现方式,并针对一类准循环LDPC码的特点,提出一种更简洁的快速编码算法及设计实现思路。

2009-12-02 16:25:14 22

22 规则LDPC码的密度进化方法及其高斯近似:密度进化方法是分析现代高效纠错编译码渐进性能的新方法。在简要阐述LDPC码及其和积算法的基础上,较系统的论述了密度进化方法的基本

2010-01-12 18:55:09 18

18 本文提出了基于FPGA 正码速调整的设计方案,采用格雷码对地址编码的异步FIFO设计,并利用MAXPLUSⅡ进行编译和仿真。结果表明,设计方法切实可行。

2010-01-13 15:16:07 25

25 该文用一种级联码模型描述了LDPC 编码高阶调制系统。该级联码模型以LDPC 码为外码,二-十进制转换码为内码,再加一个删余模块构成。基于这种级联码模型,该文给出了其联合校验

2010-02-08 16:06:44 11

11 Stratix II EP2S60 DSP Development Board

The Stratix® II EP2S60 DSP development board

2010-04-07 10:54:27 53

53 提出了一种基于IEEE802.16e的具有线性编码复杂度的LDPC码的硬件编码器结构,并且在TSMC的0.18?滋m工艺库的最恶劣情况下,通过Design Compiler工具综合可以达到385MHz的速度。

2010-07-06 16:59:28 23

23 基于TMS320C6416高性能通用DSP,实现了对AWGN信道的信噪比(SNR)估计,并以此估计值设计了一种低密度奇偶校验(LDPC)码的译码系统;详尽介绍了集成SNR估计的译码系统的实现方案和流程;仿真

2010-07-27 16:28:32 11

11 低密度奇偶校验码(Low-Density-Parity-Checkcodes,简称LDPC码)是第四代通信系统强有力的竞争者,它是一种逼近香农限的线性分组码,译码的复杂度较低;但它的直接编码运算量较大,

2010-08-09 15:06:22 0

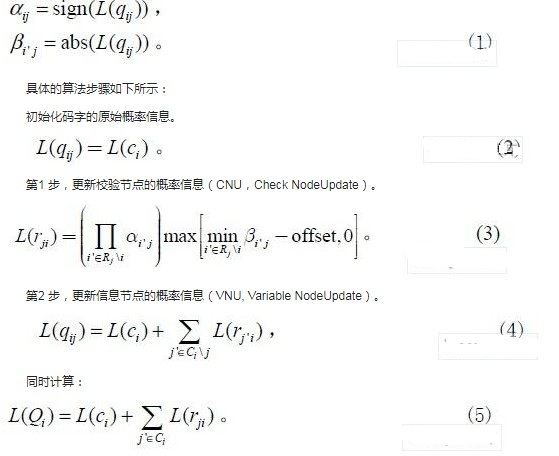

0 引言

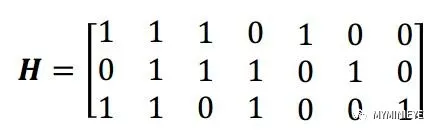

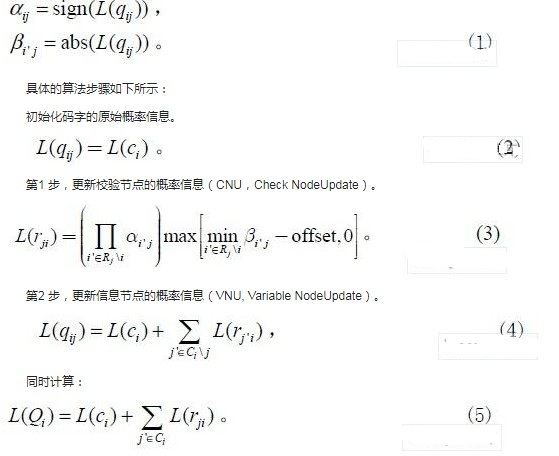

低密度奇偶校验(Low Density Parity Check Code,LDPC)码是一类具有稀疏校验矩阵的线性分组码,不仅有逼近Shannon限的良好性能,而且译码复杂度较低, 结

2007-08-15 17:20:18 2135

2135

LDPC编译码LDPC码是一种线性分组奇偶校验码,它采用基于因子图的置信传播(Belief Propagation,BP)迭代译码算法进行译码。其性能接近Turbo码,不规则LDPC码甚至超过Tur

2009-03-01 17:36:05 2334

2334

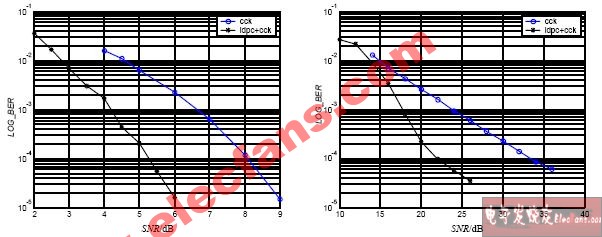

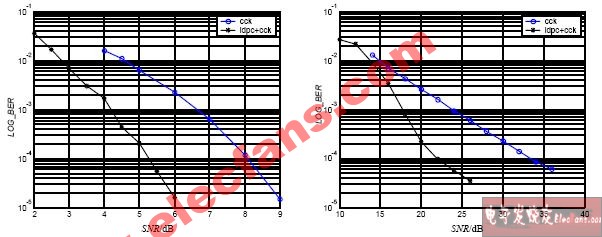

级联LDPC和CCK码的性能

从图3可知,CCK在衰落信道下的性能很差,当SNR=32 dB时,BER才近似为10-4。原因是因为CCK码集合中各码字间互相关特

2009-03-01 17:45:05 1865

1865

一种输出格式可控的多码率LDPC编码器实现

0 引 言

目前,LDPC码已广泛应用于深空通信、光纤通信、数字音视频广播等领域。由于有着较Turbo码更优秀的性能,

2009-11-25 09:56:43 1793

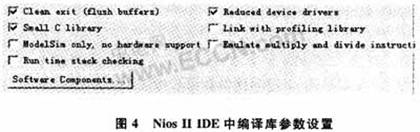

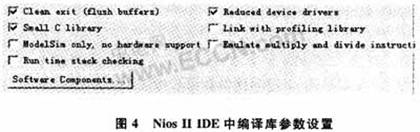

1793 为了提高设计性能(有时甚至只是为了达到设计要求),对所设计的SOPC系统进行综合优化是非常必要的。论文结合具体工程,以Altera公司的FPGA EP2S60为例,探讨了SOPC系统设计的综合优

2010-06-01 08:10:23 885

885

提出了一种基于FPGA并利用Verilog HDL实现的CMI编码设计方法。研究了CMI码型的编码特点,提出了利用Altera公司CycloneⅡ系列EP2C5Q型号FPGA完成CMI编码功能的方案。在系统程序设计中,首先产生m序列,然后程序再对m序列进行CMI码型变换。在CMI码型变换过程中

2011-01-15 15:44:04 67

67 一、实验目的 1、了解几种常用的数字基带信号。 2、掌握常用数字基带传输码型的编码规则。 3、掌握常用CPLD实现码型变换的方法。 二、实验内容 1、观察NRZ码、RZ码、AMI码、HDB3码、

2011-03-24 15:28:15 0

0 LDPC(Low Density Parity Check)码是Gallager最早于1962年提出的一种具有稀疏校验矩阵的分组纠错码,亦称Gallager码。之后,在Turbo码研究的巨大成功的带动下,Mackay等人重新研究了LDPC码,并发现

2011-03-31 16:15:53 32

32 本文设计实现了一种支持WIMAX标准的码长、码率可配置LDPC码译码器,通过设计一种基于串行工作模式的运算单元,实现了对该标准中所有码率的支持

2011-06-08 09:52:17 2537

2537

本文研究高速 数据传输 中的低密度校验(LDPC)码编码的原理、有效编解码算法以及基于低密度校验编码的编码调制系统的分析和设计方法。LDPC 码是一类能够达到Shannon 极限性能的线性分

2011-06-14 16:33:36 0

0 本文首先介绍了信道编码的发展历程,以及LDPC码的基本原理和摹本概念,然后从校验矩阵的构造方法、迭代译码算法以及性能分析等几个方面对LDPC码进行了讨论, 介绍了相关技术的主

2011-08-26 11:44:01 0

0 本文提出了一种用FPGA实现纠错编码的设计思想,并以Altera MAX+PluslI为硬件开发平台。利用FPGA编程的特点,用软件编程方法,很好的解决了纠错编码中存在的码速变换和实时性问题,实现

2011-11-10 17:10:59 61

61 根据IEEE802.16e标准中对LDPC码的定义,利用FPGA对编码器进行了实现。所采用的算法使用了线性复杂度编码,降低了逻辑资源占用量,并提高了编码速度。

2011-12-07 14:06:14 33

33 建了一个基于Altera 的EP2S60硬件处理平台,利用Altera提供的FFT IP核,在100 MHz系统时钟下,数据吞吐率可达100 Ms/s。

2012-02-27 11:21:13 30

30 以Altera公司的FPGA EP2S60为例,探讨了SOPC系统设计的综合优化方法。

2012-03-12 11:49:28 1720

1720

为实现某专用接口装置的接口功能检测,文中详细地介绍了一种34位串行码的编码方式,并基于FPGA芯片设计了该类型编码的接收、发送电路。重点分析了电路各模块的设计思路。电路采

2012-06-18 12:37:09 41

41 在LDPC译码时,使用LLR BP算法其校验节点的计算复杂度十分高,而且当LDPC码中有许多的短环时,译码性能也会降低。基于以上的这些问题提出了一个新的混合校验变量过程,通过调整校

2012-07-06 16:44:03 42

42 上世纪60年代初,香农的学生Gallager在他的博士毕业论文中首次提出了LDPC码的概念和完整的译码方法,但是直到上世纪末期,随着LDPC码译码理论的进步和计算机技术的发展,LDPC码才以其

2012-11-07 15:05:11 0

0 本系统的设计是基于Altera公司的EP2S60系列的开发板,板上集成两片 SDRAM存储芯片、视频输入接口和VGA输出接口

2012-12-16 10:07:31 1553

1553 香农的学生Gallager首次提出了LDPC码的概念和完整的译码方法,目前LDPC码正向着高速高增益的方向发展。文中针对目前对高速LDPC码译码技术的迫切需求,以CCSDS标准近地通信(8176,7154)

2013-07-26 11:17:00 0

0 这是verilog写的可以实现卷积编码1/2码率的代码,附带测试文件0

2016-01-20 18:23:39 1

1 800Mbps准循环LDPC码编码器的FPGA实现

2016-05-09 10:59:26 37

37 GA_高斯近似_LDPC_POLAR(极化码)_构造

2016-06-08 16:34:58 22

22 基于FPGA的经济型MPEG2运动图像编码器IP核设计

2016-08-30 15:10:14 9

9 主要应用于精密加工机械,纺织机械,机械手,自动化车库等,EP50S系列外径50mm轴型绝对值旋转编码器特点: 1、外径50mm紧凑尺寸设计 2、多种输出码制:BCD码,二进制码,格雷码 3、多种高分辨率(720,1024) 4、IP64防护等级(防尘,防油污)

2017-09-28 14:33:07 9

9 的低运算复杂度、低误码平台译码的改进算法。 该算法校验节点的运算采用修正最小和算法,外信息的更新采用串行方式,既保持了串行和积算法在有限迭代次数下译码门限低的优点,又降低了节点运算复杂度和误码平台。用定点DSP芯片实现的非规则LDPC码译码器的实测结果表明,该算法能以较低的实现复杂度获

2017-10-20 10:41:11 0

0 咨询委员会(CCSDS) 也将其推荐为应用于深空通信的信道编码方式。香农指出,对于任何信道,只要采用随机性编、译码方式,编码长度接近无限大,在其信息传输速率不超过信道容量时,采用最佳的似然译码方案,必然存在一种编码方式的误码率可以任意小。LDPC 码之

2017-10-31 14:07:53 3

3 该文通过对低密度校验(LDPC)码的编译码过程进行分析,提出了一种基于FPGA 的LDPC 码编译码器联合设计方法,该方法使编码器和译码器共用同一校验计算电路和复用相同的RAM 存储块,有效减少

2017-11-22 07:34:01 5141

5141

本文采用Altera公司Stratix II系列的EP2S90F1508C3芯片,以Quartus II 8.1为开发环境[4],采用硬件描述语言VHDL进行SM3算法的FPGA实现。SM3算法实现

2017-11-24 15:33:59 3108

3108

信息协调是量子密钥分发中的关键步骤,基于LDPC实现量子信息协调是当前国内外研究的焦点。目前QKD系统LDPC译码器普遍采用单码字顺序译码机制设计,且采用的是性能较差的准循环LDPC码,LDPC

2017-11-25 10:10:46 2

2 信道编译码技术可以检测并且纠正信号在传输过程中引入的错误,能够保证数据进行可靠的传输[1]. LDPC码的校验矩阵具有稀疏的特性,因此存在高效的译码算法,其纠错能力非常强。1981年,Tanner

2017-11-30 10:21:27 5864

5864

回路长度和回路数目的影响,回路的存在使译码信息重复迭代,性能下降。本论文通过计算机仿真,采用Matlab元胞数组,将二元校验矩阵转换为树矩阵,实现了求解LDPC码回路的算法。

2017-12-26 11:09:14 0

0 在卫星通信中,如何提高抗干扰能力是需要重点关注的问题之一。多元域LDPC码是通信界研究的热点课题,较二进制LDPC码有更优的纠错性能。本文从卫星通信的应用角度出发,对利用LU分解进行编码的通用编码

2017-12-29 14:04:59 0

0 为设计出可近容量限传输且能普适应用于慢、快衰落信道下的编码协作方案,研究了基于卷积LDPC码的编码协作。基于卷积LDPC码的凿孔算法构造出可2路传输的分码字,实现编码协作,并在第二帧分码字传输阶段引入了空时传输进一步提升编码协作的性能。仿真验证了所提方案的有效性。

2018-01-16 14:38:02 0

0 准循环结构;在此基础上,使其与准双对角结构相结合,构造出的QC-LDPC码围长不会减小,且具有低复杂度可快速编码的双重特性。仿真结果显示在加性高斯白噪声( AWGN)和置信传播(BP)译码算法下,所提方法构造的QC-LDPC码在误码率为10-5时,信

2018-01-16 18:48:05 0

0 出了一种基于FPGA并利用Verilog HDL实现的CMI编码设计方法。研究了CMI码型的编码特点,提出了利用Altera公司CycloneⅡ系列EP2C5Q型号FPGA完成CMI编码功能的方案

2018-05-31 04:38:00 3020

3020

的重视。基于准循环LDPC(QC-LDPC)码结构特点,提出了一种支持多种码率QC-LDPC 译码器的设计方法,并设计实现了一个能够实时自适应支持三个不同H 阵的通用QC-LDPC 译码器。

2019-01-08 09:22:00 3913

3913

本文对2004年由王鹏提出的LDPC码迭代编码算法[11]进行改进,转变为适用于多元LDPC码的编码算法,称为多元迭代编码算法;2005年,Hu Xiaoyu提出了渐进边增长(Progressive Edge Growth,PEG)构造算法[12],该算法译码性能好,但编码复杂度较高。

2018-09-23 08:59:00 5484

5484

,低密度奇偶校验码)编码,以水印方式嵌入到原始困像中;篡改检测时,同样对篡改图像进行线性随机投影,得到的测量值作为边信息,对提取的水印进行LDPC译码。通过估计原始图像和篡改图像的压缩测量值,并求解一个!范数问题,实现图像的篡改检测。仿真实验证明,该算法不仅

2018-11-29 14:29:01 4

4 LDPC码被认为是当今3D TLC和QLC存储器中提高错误率的解决方案。然而它们并不适合每个市场。

2019-10-21 17:23:27 2511

2511 由于并行解码性能与串行解码在性能上并无差别,只是占用更多的硬件资源来换取更快的速度,并且每一种并行结构只能针对具有某一特定校验矩阵的LDPC码。所以本文就以串行解码硬件实现方式进行实现分析。

2020-01-08 15:47:33 4473

4473

为块准循环结构,从而能够并行化处理译码算法的行与列操作。使用这个架构,我们在Xilinx Virtex-5 LX330 FPGA上实现了(8176,7154)有限几何LDPC码的译码器,在15次迭代的条件下其译码吞吐量达到800Mbps。

2021-01-22 15:08:39 9

9 随着硅片集成技术的高速发展,片上系统SoC(system-on-a-Chip)已经成为现代数字系统设计的必然趋势。SoC和一般数字系统最主要的区别是前者在单一硅片内集成了独立的嵌入式CPU,必要的存储器控制器也要求集成到SoC芯片内,所以对SoC系统的软硬件协同实时验证便成为SoC设计的难点。

2021-03-17 17:04:25 3142

3142

结构化LDPC码可进行相应扩展通过对编译码算法,优化编译码结构进行调整,降低了编译码嚣硬件实现中的关键路径迟延,并采用Xilinx公司的Virtex一4 VLX80 FPGA芯片实现了一个码长10 240,码率1/2的非正则结构化LDPC码编码器和译码器。实现结果表明:该编码器信息吞吐量为1.878 Gb/

2021-03-26 15:58:00 12

12 AD2S1210-EP:增强型产品数据表

2021-05-12 19:22:36 4

4 基于FPGA的800Mbps准循环LDPC码译码器

2021-06-08 10:31:31 26

26 瑞萨的RZ/A2M微处理器可以利用其独特的动态可配置处理器(DRP)完美解决这一问题,实现了1280x720(1百万)摄像头输入时,在8ms时间内完成QR ,Micro QR, DataMatrix, AZTec 和汉信码5种编码格式的快速识别,下面让我们看一下DRP是如何实现的。

2022-04-29 15:17:20 2535

2535

电子发烧友网站提供《基于FPGA的直接序列扩频和差错控制码编码系统的实现.pdf》资料免费下载

2023-11-06 15:57:52 0

0

![]()

![]()

![]()

电子发烧友App

电子发烧友App

评论