作者:李阳;刘政林;汤加跃;邹雪城

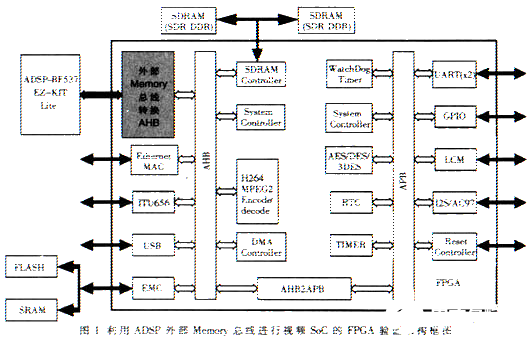

随着硅片集成技术的高速发展,片上系统SoC(system-on-a-Chip)已经成为现代数字系统设计的必然趋势。SoC和一般数字系统最主要的区别是前者在单一硅片内集成了独立的嵌入式CPU,必要的存储器控制器也要求集成到SoC芯片内,所以对SoC系统的软硬件协同实时验证便成为SoC设计的难点。基于IP的可重用设计方法已经成为数字系统设计工程师普遍采用的系统设计方法。于是,设计者采用第三方IP或自行设计的软核或两者的组合来搭建符合要求的系统。对于一个SoC系统,嵌入式CPU的选择至关重要。第三方提供CPU的方式有软核和固核,如果在设计过程中仅被授权采用第三方优化的固核(版图级),则前端FPGA实时验证问题自然凸现出来。解决的办法是选择相应CPU的验证开发板或者采用其他处理器。本文介绍一种利用嵌入Blackfin处理器的ADSP-BF537作为处理器进行SoC的FPGA实时验证的方案及其总线接口转换模块的设计。SoC系统验证平台结构框图如图1所示。

1 ADSP简介

ADSP是ADI(Analog Device Inc.)公司推出的一系列高性能低功耗DSP芯片,而基于Blackfin处理器的ADSP-BF533一经推出便被很多国家的设计人员立即采用,后续系列产品ADSP-BF5xx也被更多的系统设计厂家应用到各自的产品中。正是因为ADSP-BF5xx系列芯片是以功能强大性能卓越的Blackfin处理器为内核而推出的高效DSP芯片,使得人们可以采用ADSP-BF5xx系列芯片作为处理器进行视频SoC的FPGA实时验证。Blackfin处理器集成了一个由ADI公司和Intel公司联合开发的基于MSA(Micro Signal Architecture)的16/32位嵌入式处理器,支持32位RISC指令集,采用10级流水线,集成了两个16位乘法加速器,内核主频最高可以达到600MHz。

2 ADSP外部Momory总线介绍

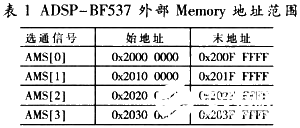

ADSP外部Memory总线可以进行同步或异步操作,前者是通过时钟输出端CLKOUT进行同步的。本文所采用的ADSP-BF537 Ez-kit Lite开发套件的外部Memory总线的可用地址仅为19位(ADDR[19:1]),并且采用AMS[3:0]选中相应的外部区域。ADSP-BF537的四个选通信号线对应的外部Memory地址范围如表1所示。可以看出,直接利用ADSP外部Memory总线操作的地址空间只有4MB容量,显然不能满足SoC的选址需求,必须进行接口总线的转换来提高寻址范围。

ADSP-BF537外部Memory读写时序波形如图2所示,其中的ARDY信号是由外设产生的。ADSP通过设置EBIU_AMBCTLx寄存器,允许传输过程中使用ARDY握手信号,用来增强系统运行的准确度。ARDY信号的有效电平是可以设置的。

EBIU_AMBCTLx寄存器还可以改变ADSP对外读写操作的时序,包括数据建立时间、读写通路时间以及数据保持时间。例如,图2所示的写操作建立时间、通路时间和保持时间分别是2个周期、2个周期和1个周期。如果使能ARDY信号,并设置为高电平有效,则在设定的读写时间内,ARDY为低电平表示外设不能写入或者读出数据,需要ADSP继续保持相应的读写等待状态,直到ARDY信号被拉为高电平;只有当ADSP检测到ARDY为高电平时,才能将DATA数据作为有效数据。上述过程如图2中的读操作,ARDY信号被拉低了一个周期。

ADSP-BF537的外部Memory地址总线位宽是ADDR[19:1],这样可以使ADSP灵活地对16/32位数据进行地址选址。例如,如果对连续地址进行16位数据的读写操作,ADDR[19:1]只需依次加1,而ADSP软件开发工具中相应的内部变量数据类型定义为short即可;类似地,如果要读写的数据类型为int(32位)数据,则每次访问外部地址时,ADSP会连续产生两次读写操作,并且地址总线ADDR[19:1]是连续的。

3 AHB总线介绍

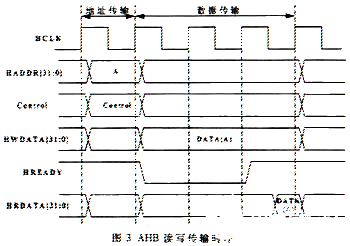

AHB(Advanced High-performance Bus)是AMBA总线中用途最为广泛的一种高速总线,因其协议简单、可综合性强、支持主频高、功耗低,已经被很多SoC芯片作为内部高速系统总线。大多数第三方IP厂商提供的功能模块的接口都支持AMBA总线协议。AHB基本传输时序如图3所示。

4消除信号的亚稳态现象

在本次视频SoC的FPGA验证方案中,采用ADSP的外部Memory总线,FPGA既可以利用同步时钟输出CLKOUT进行同步设计,也可以采用异步总线读写。如果不使用CLKOUT而采用异步设计,则在总线转换接口模块设计中,首先需要保证消除读写信号亚稳态现象。ADSP内核主频可以达到600MHz,外部Memory总线的采样时钟(CLKOUT)动态调整范围也很大,因此对异步输入信号可以采用增加同步触发器进行锁存延时的方法来消除亚稳态。具体实现方法是在异步输入信号的前端加2-3级同步触发器。FPGA验证证明:当CLKOUT频率为50MHz,FPGA系统主频为25MHz时,3级同步锁存完全可以消除亚稳态,从而保证ADSP在外部Memory总线上正确进行数据传输。

5总线转换状态机设计

目前,大多数采用AMBA总线的SoC系统内部的总线位宽是32位,多数嵌入式CPU和第三方IP核总线位宽也均为32位,因为32位地址总线和数据总线已经可以满足绝大多数SoC系统的存储器映射寄存器的地址分配和数据交换以及外部SDRAM和FLASH的寻址需求。ADSP-BF537的外部Memory数据总线是16位,并且地址总线只有19位,因此必须通过增加必要的状态来解决总线位宽的不匹配问题。

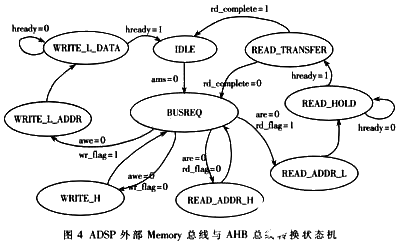

为了实现ADSP对外进行32位的地址操作和数据操作,可以利用Blackfin处理器分两次进行读写操作。写操作分两次进行,第一次写,先传输地址和数据的高16位,第二次写才将32位的地址和数据信号传输到AHB总线上;进行读操作时,需要AHB产生两次读动作,这样才能使有效的32位数据被Blackfin处理器正确接收。第一次读到有效的32位数据后传输高位,第二次读到后传输低位,并且每次读操作都需要Blackfin发出两次读动作,以便组合出AHB的32位地址。这样就可以突破ADSP-BF537对外只能进行4MB空间存取的限制。以上描述过程的状态机转换图如图4所示。

利用ADSP作为SoC系统处理器进行SoC验证时,ADSP进行的主要操作是读写系统内部各个功能模块的Memory映射控制寄存器,并且通过SDRAM控制器对SoC系统的外部SDRAM进行数据交换操作。因此总线转换状态机分成读传输和写传输两大部分。

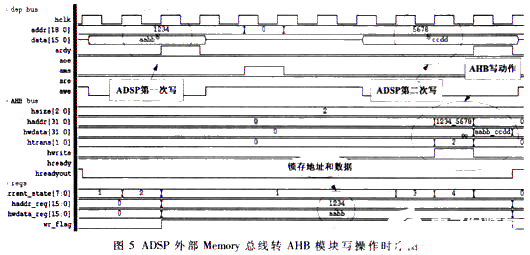

当ADSP需要进行外部Memory总线传输时,首先会把相应的ams信号拉低,这时总线转换状态机应该使AHB进入BUSREQ状态,要求仲裁器释放AHB总线给CPU(ADSP)。

对于一个写操作,需定义一个wr_flag标志位来确定是否产生AHB写动作。ams信号拉低后,经过可配置的写建立时间后,写控制信号awe被拉低,初始化的wr_flag为0,表明ADSP进行的是第一次写操作。进入的WRITE_H状态用来锁存写地址和写数据的高16位,同时会把wr_flag置为1,但并不向AHB总线发出写命令。一个周期后重新进入BUSREQ状态,等待ADSP下一个写命令。ADSP发出第二次写命令后,状态机检测到awe=0和wr_flag=1后进入WRITE_L_ADDR状态,表明需要向AHB发出写命令,包括hwrite、haddr、htrans、hsize等AHB控制信号。haddr是两次写操作地址(16位)组合而成的32位地址,htrans=2和hsize=2,表明是非连续传输,传输数据位宽是32位。下一个周期,状态进入WRITE_L_DATA,两次写操作数据也相应组合成32位。如果AHB slave的hready为高,则32位数据释放到AHB总线上,同时复位AHB控制信号,下一个周期返回IDLE状态;如果hready为低,则继续保持WRITE_L_DATA状态,直到AHB slave把hready拉高有效。如果等待时间过长,可以增加一个计数器使状态机在一定时间后自动返回IDLE状态,并标记相应的error状态寄存器。例如,需要通过ADSP向haddr[31:0]=0x1234_5678地址内写入hwdata[31:0]=0xaabb_ccdd,则测试平台(采用vmt slave)模拟ADSP对外进行两次写操作,第一次向addr[18:0]=0x1234内写0xaabb,第二次向addr[18:0]=0x5678内写0xccdd,如图5所示。第二次写操作后正确产生AHB写操作。

同样,对于一个读操作,状态机也需要两次对AHB发出读动作,把读到的slave数据分高低位两次传输给ADSP,不同的是,为了保证AHB读地址是32位,而不仅仅是ADSP外部Memory地址总线的19位,每次AHB的读命令,需要ADSP两次读动作,第一次读用来传输高位地址,第二次读才能把完整的32位地址传送到AHB上,使AHB产生读操作。上述过程的状态依次是图4中的READ_ADDR_H、READ_ADDR_L、READ_HOLD、READ_TRANSFER。标志位rd_complete用来区分AHB的两次读动作,为0时在READ_TRANSFER状态传输读取数据的高16位,被ADSP读取,下一个周期后进入BUSREQ状态等待下一个读命令;为1时在READ_TRANSTER状态传输读取数据的低16位,并返回IDLE状态。例如需要读取上述已经被写入地址haddr[31:0]=0x1235_5678的值时,第一次ADSP发出读addr[18:0]=0x1234,第二次发出读addr[18:0]=0x5678,这时ADSP的data只传输高位数据0xaabb,ADSP再发两次相同的读命令后,data才传输低位数据0xccdd。对应的读操作的仿真波形如图6所示。

如前所述,ADSP外部Memory总线在对外读写时可以通过EBIU_AMBCTlx寄存器来选择是否选通握手信号ARDY。为了提高传输的可靠性和准确度,在设计转换模块时需要考虑ARDY,如图5、图6中的读写操作时序图所示,在每一次数据传输完成的最后一个状态,需要将ARDY信号置1,然后在下一个IDLE或BUSREQ状态将ARDY清0,这样可以保证ADSP能正确读到ADSP外部Memory数据总线上的有效数据,防止因ADSP对外读写时序设置不合理而造成系统不能正常运行。

6 FPGA实现

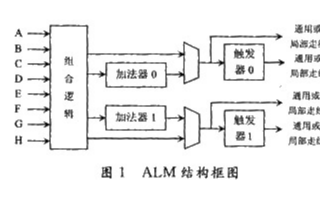

本模块的设计是用于FPGA验证用途的,对于大型视频SoC系统的FPGA实时验证,往往需要采用大容量的FPGA,因此本设计采用Altera Stratix II EP2S60器件进行FPGA验证。采用Quartus综合和布局布线后,一共需要140个ALUT和131个寄存器,最快时钟可以达到300MHz。因为ADSP可以设置外部Memory总线的读写时序,所以对外访问的速率不是惟一的。为了实现16位到32位的转换虽然增加了读写的次数,但因为ADSP外部Memory同步时钟频率调整范围很大,因此本设计完全可以满足IP核功能验证对频率的要求,对于视频SoC内部基本AHB总线和APB总线上的功能模块都能正确实时验证。基于ADSP-BF537内部嵌入的Blackfin处理器及其DSP接口,已经利用本接口模块成功地验证了AHB总线上的H264和MPEG一2的encode与decode加速器、Ethernet MAC控制器、SDRAM控制器以及APB总线上的UART、TIMER、AC97、GPIO和LCD控制器等低速外设。

随着验证环节在SoC产品开发过程中所占时间和开销的迅速增加,Altera和Xilinx在其大容量FPGA芯片产品中,都集成了特定类型的CPU作为系统处理器,但它们都受到特定FPGA器件的限制。因此利用ADSP内嵌的强大Blackfin处理器和丰富的DSP外设,可以有效地提高验证的效率和功能的完整性。本文的总线接口模块的设计对具有不同读写时序的验证板的正常工作起着重要的作用,SoC原型的搭建必然要求本模块能真实反映实际AHB总线的动作,这样对于保证各个功能模块的完整性和实时工作将起很大的作用。

责任编辑:gt

-

FPGA

+关注

关注

1655文章

22287浏览量

630317 -

嵌入式

+关注

关注

5186文章

20151浏览量

328896 -

soc

+关注

关注

38文章

4514浏览量

227631

发布评论请先 登录

Quartus II软件和Quartus II网络版的区别

基于Stratix II EP2S60改进中值滤波器的设计及实现,不看肯定后悔

Stratix II EP2S60 DSP Developm

针对Altera Stratix IV EP4SGX360和

针对Altera Stratix IV EP4SGX70和E

Altera推出业界密度最大的Stratix IV EP4S

一种线性卷积实时实现方案

基于Altera FPGA的视频信号处理的设计与实现

Altera推出Quartus II v13.0,支持实现世界上最快的FPGA设计

业界密度最大的Stratix IV EP4SE820 FPGA(Altera)

锆石FPGA A4_Nano开发板视频:NiOS II硬件框架结构深入剖析2

锆石FPGA A4_Nano开发板视频:NiOS II硬件框架结构深入剖析(2)

采用StratixⅡ FPGA器件提高加法树性能并实现设计

采用Altera Stratix II EP2S60器件实现SoC系统的FPGA实时验证

采用Altera Stratix II EP2S60器件实现SoC系统的FPGA实时验证

评论