锁相环电路

锁相环

2009-09-25 14:28:39 7723

7723

锁相环:在通信领域中,锁相环是一种利用反馈控制原理实现的频率及相位同步技术,其作用是将电路输出的时钟与其外部的参考时钟保持同步。

2023-06-30 15:53:39 6425

6425

大家都知道锁相环很重要,它是基石,锁相环决定了收发系统的基础指标,那么如此重要的锁相环选型原则有哪些呢?

2023-08-01 09:37:05 7303

7303

ADSP-BF531 - Blackfin Embedded Processor - Analog Devices

2022-11-04 17:22:44

ADSP-BF531 原理图和PCB图 附件下载

2011-02-17 14:59:17

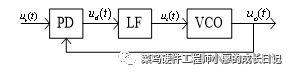

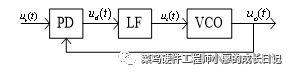

、压控振荡器(VCO) 四、环路滤波器(LPF) 五、固有频率ωn和阻尼系数x 的物 理意义 六、同步带和捕捉带 •第二部分:锁相环实验 •实验一、PLL参数测试 •一、压控灵敏度KO的测量 •二

2011-12-21 17:35:00

ADSP-BF531的SPORT0口上了,按照手册上的说明给A/D送设置数据,然后再接收它的数据,但是我发现在我刚送完Control Register 2的数据后还没有送Control Register 1的数据

2018-11-26 09:50:37

用于Blackfin处理器的ADZS-BF707-EZLITE,ADSP-BF70x EZ-KIT Lite评估系统。 ADSP-BF707处理器是Blackfin系列产品的成员。 Blackfin

2019-03-13 09:40:34

LabVIEW锁相环(PLL) 锁相环是一种反馈电路,其作用是使得电路上的时钟和某一外部时钟的相位同步。PLL通过比较外部信号的相位和由压控晶振(VCXO)的相位来实现同步的,在比较的过程中,锁相环

2022-05-31 19:58:27

原理实现的频率及相位的同步技术,其作用是将电路输出的时钟与其外部的参考时钟保持同步。当参考时钟的频率或相位发生改变时,锁相环会检测到这种变化,并且通过其内部的反馈系统来调节输出频率,直到两者

2021-11-04 08:57:18

MSM8940处理器是什么?MSM8940处理器有哪些特点?

2021-11-09 07:09:11

RK3399处理器与AR9201处理器有哪些不同之处呢?hi3559A处理器与RV1126处理器有哪些不同之处呢?

2022-02-21 07:29:27

和复位电路时钟电路F2812处理器上有基于PLL的时钟模块,为器件及各种外设提供时钟信号。锁相环有4位倍频设置位,可以为处理器提供各种频率的时钟。时钟模块提供两种操作模式,如图6所示。内部振荡器

2019-05-22 05:01:15

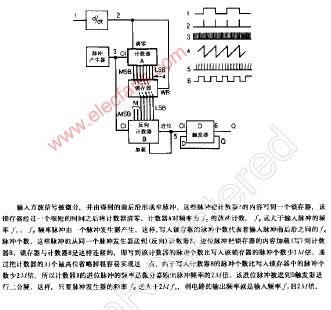

相同的方法用lead产生一个dec信号,用lag信号产生一个inc信号。至此,整个数字锁相环已经设计完毕。步骤中提到的计数器就相当于积分,phase的作用就是完成鉴相,第10步也就是一些有关数字锁相环的书籍

2012-01-12 15:29:12

怎么设计一种用于多路输出时钟缓冲器中的锁相环?锁相环主要结构包括哪些?

2021-04-20 06:27:26

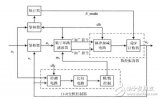

本文针对一款应用于大规模集成电路的CMOS高频锁相环时钟发生器,提出了一种可行的测试方案,重点讲述了锁相环的输出频率和锁定时间参数的测试,给出了具体的测试电路和测试方法。对于应用在大规模电路系统中的锁相环模块,该测试方案既可用于锁相环的性能评测,也可用于锁相环的生产测试。

2021-04-21 06:28:15

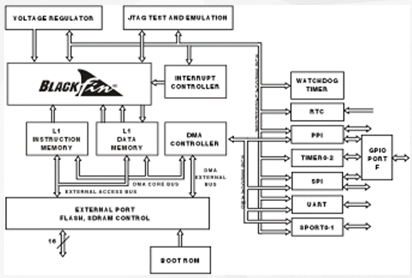

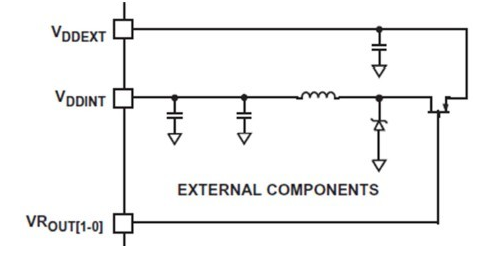

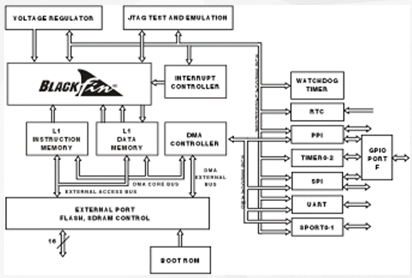

ADSP-BF53x 是主频高达600 MHz 高性能Blackfin 处理器内核包括:2 个16 位MAC,2 个40 位ALU,4 个8位视频ALU,以及1 个40 位移位器RISC 式寄存器和指令模型,编程简单,编译环境友好

2008-04-14 18:19:01 129

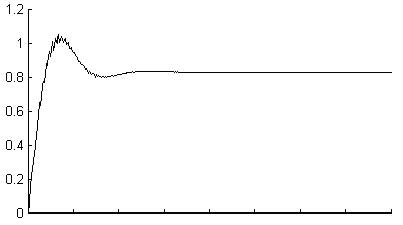

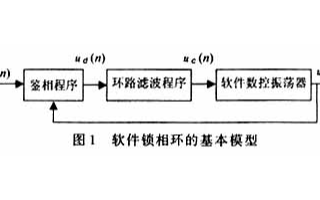

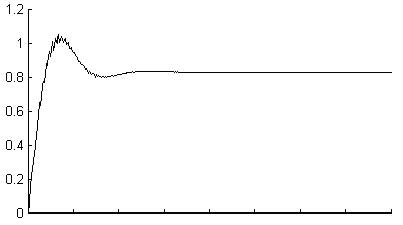

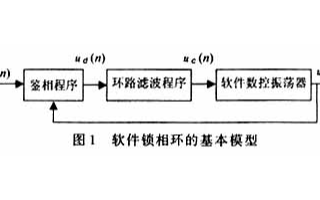

129 根据虚拟无线电技术的特点和锁相环的基本原理,提出一种适于计算机软件化实现的锁相环数学模型,分析不同参数对锁相环捕获和跟踪性能的影响,得出不同情况下参数设定的基

2008-08-15 12:36:19 101

101 一、实验目的1、掌握模拟锁相环的组成及工作原理。2、学习用集成锁相环构成锁相解调电路。3、学习用集成锁相环构成锁相倍频电路。

二、锁相环路的基本原理

2009-03-22 11:44:37 127

127 锁相环电路的设计:

2009-07-25 17:05:36 0

0 锁相环设计举例:锁相环设计主要包括:确定所需环的类型,选择适当的带宽,指出希望的稳定度。下面将举例说明要满足这些设计要求而常用的基本方法。

2009-09-05 08:51:42 105

105 基于ADSP-BF533 处理器的去方块滤波器的实现及优化关键词:视频编解码,去方块滤波,ADSP-BF533 处理器摘要:本文通过系统、算法及汇编3 个级别优化实现了H.264 中的去方块滤波

2010-01-26 17:58:39 19

19 加快图像处理算法和降低整体带宽要求而设计。其他特性包括高性能增强型基础设施、大型片内存储器和功能丰富的外设集,以及扩展的连接选项。此外,ADSP-BF608处理器内

2023-07-07 10:19:18

一维和二维DMA传送。处理器内核的高速与DMA控制器相结合,可实现音频、语音、视频和图像数据的有效处理。ADSP-BF525提供外围设备的灵活性来补充它的高性能处

2023-07-07 11:20:03

ADSP-BF542处理器专为满足注重系统性能和成本的汇聚多媒体应用的需求而设计。多媒体、人机接口和连接外设的集成与更高的系统带宽和更大的片上存储器相结合,为客户提供了一个用来设计要求最严苛

2023-07-07 11:27:36

ADSP-BF547处理器专为满足注重系统性能和成本的汇聚多媒体应用的需求而设计。多媒体、人机接口和连接外设的集成与更高的系统带宽和更大的片上存储器相结合,为客户提供了一个用来设计要求

2023-07-07 11:39:43

ADSP-BF549处理器专门针对融合汽车多媒体应用而设计;在这些应用中,系统性能和成本是关键考虑因素。该处理器集多媒体、人机界面、连接外设与更高的系统带宽和片内存储器于一体,为客户设计要求严苛

2023-07-07 11:47:10

ADI公司早期的ADSP-BF531、ADSP-BF532和ADSP-BF533产品系列具备Blackfin处理器的所有简单易用和架构上的特性。这三个处理器全部完全引脚兼容,仅在其性能和片上存储器

2023-07-07 13:31:10

ADI公司最初的产品系列ADSP-BF531、ADSP-BF532与ADSP-BF533可提供Blackfin处理器所有的易用性和架构特性。这三款处理器完全引脚兼容,区别仅在于性能和片上存储器

2023-07-07 13:34:28

ADSP-BF561扩展了Blackfin®处理器系列产品的性能。ADSP-BF561具有两个高性能Blackfin处理器内核、灵活的高速缓存架构、增强的DMA子系统,以及动态电源管理(DPM)功能

2023-07-07 13:37:38

描述 ADI公司最初的产品系列ADSP-BF531、ADSP-BF532与ADSP-BF533可提供Blackfin处理器所有的易用性和架构特性。这三款处理器完全引脚兼容,区别仅在于性能

2023-12-28 15:27:37

描述 ADI公司早期的ADSP-BF531、ADSP-BF532和ADSP-BF533产品系列具备Blackfin处理器的所有简单易用和架构上的特性。这三个处理器全部完全引脚兼容,仅在

2023-12-28 15:36:47

针对广播发射机数字音源的自动监测和切换,提出了一种基于ADSP-BF531的数字音频信号的监测与切换系统方案,通过对CS8420编程设置,实现多路AES3信号的自动监测,以及输出信号的

2010-12-14 10:16:39 48

48 锁相环原理

锁相环路是一种反馈电路,锁相环的英文全称是Phase-Locked Loop,简称PLL。其作用是使得电路上的时钟和某一外部时钟的相位同步。因锁相环可以

2007-08-21 14:46:04 5484

5484 应用于锁相环的脉宽调整电路的设计

前言

在锁相环PLL、DLL和时钟数据恢复电路CDR等电路的应用中,人们普遍要求输出时钟信号有50%的占空比,以便在时钟上升及下

2008-10-16 08:59:42 1504

1504

锁相环的研究和频率合成一、实验目的:1. 振荡器(VCO)的V—f 特性的研究2. 对称波锁相环基本特性的研究3. 利用锁相环实现频率合成二、锁相环原理:

2009-03-06 20:02:52 2529

2529

不带锁相环的倍频器

2009-09-17 16:11:00 1067

1067

锁相环(PLL),锁相环(PLL)是什么意思

PLL的概念

我们所说的PLL。其

2010-03-23 10:47:48 6368

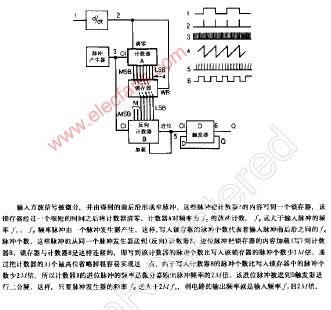

6368 数字锁相环(DPLL),数字锁相环(DPLL)是什么?

背景知识:

随着数字电路技术的发展,数字锁相环在调制解调、频率合成、FM 立体声解码、彩色副

2010-03-23 15:06:21 6110

6110 模拟锁相环,模拟锁相环原理解析

背景知识:

锁相技术是一种相位负反馈控制技术,它利用环路的反馈原理来产生新的频率点。它的主要

2010-03-23 15:08:20 6264

6264 本文涉及的锁相环路是基于相位控制的时钟恢复系统。目的是用锁相环电路-PLL和DLL实现USB2.0收发器宏单远UTM的时钟恢复木块。其中PLL环路构成的时钟发生器奖外部晶振的12MHZ的正弦信号

2011-03-03 14:58:34 51

51 B1acKfin ADSP-BF532是一款400 MHz的处理器,具有B4Kb的片内存储器, 是BlacKfin系列处理器中的一员, 由美国ADI(模拟器件公司)出品。BlacKfin系列处理器含有新型的16132比特嵌入式处理器,专门设

2011-09-30 15:14:03 50

50 锁相环英文为PLL,即PLL锁相环。可以分为模拟锁相环和数字锁相环。两种分类的锁相环原理有较大区别,通过不同的锁相环电路实现不同的功能。

2011-10-26 12:40:28

设计了一个嵌入式语音识别系统,该系统硬件平台以ADSP-BF531为核心,采用离散隐马尔可夫模型(DHMM)检测和识别算法完成了对非特定人的孤立词语音识别。试验结果表明,该系统对非特定

2012-07-12 14:02:32 0

0 有关锁相环的部分资料,对制作锁相环有一定的帮助。

2015-10-29 14:16:55 70

70 锁相环是电路功能中最通用的。它们用于时钟处理器(相当良性的情况),以及在固定和调谐频率发射机和接收机建立调谐。

2017-05-16 10:42:41 8

8 锁相环是指一种电路或者模块,它用于在通信的接收机中,其作用是对接收到的信号进行处理,并从其中提取某个时钟的相位信息。或者说,对于接收到的信号,仿制一个时钟信号,使得这两个信号从某种角度来看是同步的(或者说,相干的)。

2017-07-27 10:01:51 36955

36955

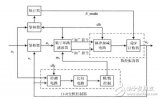

一、设计目标 基于锁相环的理论,以载波恢复环为依托搭建数字锁相环平台,并在FPGA中实现锁相环的基本功能。 在FPGA中实现锁相环的自动增益控制,锁定检测,锁定时间、失锁时间的统计计算,多普勒频偏

2017-10-16 11:36:45 19

19 引 言 ADSP-BF531处理器是ADI公司Blackfin系列产品的成员,专为满足当今嵌入式音频、视频和通信应用的计算要求和低功耗条件而设计的新型16位嵌入式处理器。它基于由ADI和Intel

2017-10-20 15:35:19 5

5 了解ADSP-21485处理器如何用于改善水平和垂直声级扩展,同时保持自然的声音音频。

2018-05-25 14:49:00 5270

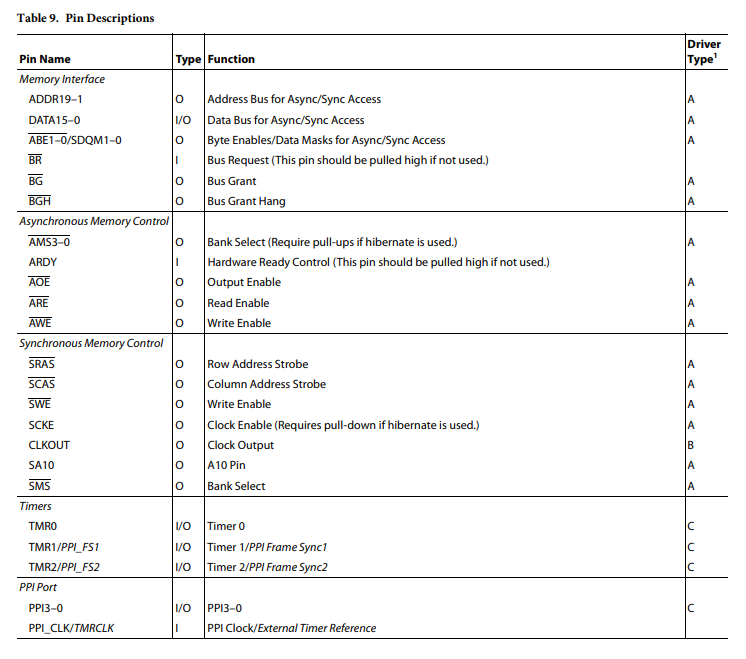

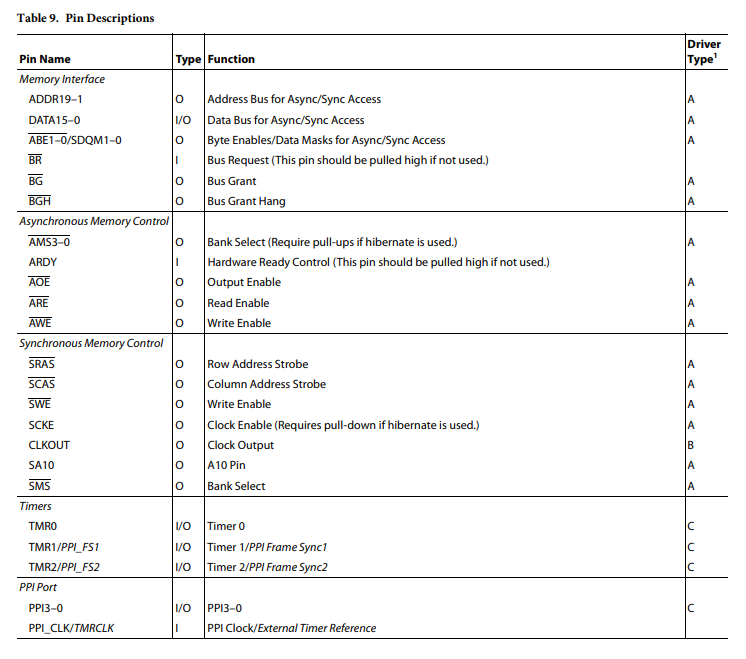

5270 电子发烧友网为你提供ADI(ti)ADSP-BF531相关产品参数、数据手册,更有ADSP-BF531的引脚图、接线图、封装手册、中文资料、英文资料,ADSP-BF531真值表,ADSP-BF531管脚等资料,希望可以帮助到广大的电子工程师们。

2019-02-22 14:51:34

了解ADSP-21485处理器如何用于改善水平和垂直声级扩展,同时保持自然的声音。

2019-07-22 06:02:00 3023

3023 本视频概要介绍新型Blackfin® BF592处理器,它是一款全新推出的低成本、高性能、低功耗、小尺寸处理器,属于ADI公司业界领先的Blackfin产品系列。

2019-06-10 06:29:00 3924

3924 随着大规模集成电路及高速数字信号处理器的发展,通信领域的信号处理越来越多地在数字域付诸实现。软件锁相技术是随着软件无线电的发展和高速DSP的出现而开展起来的一个研究课题。在软件无线电接收机中采用

2020-08-19 15:01:26 2775

2775

ADI公司推出的600MHz时钟每秒能进行12亿次乘法加法运算的处理器ADSP-BF533以及较低成本的时钟为300MHz每秒能进行6亿次乘法加法运算的处理器ADSP-BF531。两种

2021-01-15 10:19:00 2657

2657

ADSP-BF542/ADSP-BF544/ADSP-BF547/ADSP-BF548/ADSP-BF549:Blackfin嵌入式处理器数据手册

2021-03-18 23:49:13 1

1 ADSP-BF534/ADSP-BF536/ADSP-BF537:Blackfin嵌入式处理器数据手册

2021-03-19 00:44:53 9

9 ADSP-BF538/ADSP-BF538F:Blackfin嵌入式处理器数据手册

2021-03-19 00:53:41 6

6 ADSP-BF539/ADSP-BF539F:Blackfin嵌入式处理器数据手册

2021-03-19 03:16:27 8

8 ADSP-BF531/BF532/BF533 Blackfin®功耗估算(Rev 4, 12/2007)

2021-03-19 05:43:47 6

6 ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C:Blackfin嵌入式处理器数据手册

2021-03-19 10:15:10 11

11 AN-813: ADSP-BF533/ADSP-BF561 Blackn®处理器与高速并行ADC接口

2021-03-21 09:07:46 5

5 ADSP-BF522/ADSP-BF523/ADSP-BF524/ADSP-BF525/ADSP-BF526/ADSP-BF527:Blackfin嵌入式处理器数据手册

2021-03-21 16:01:26 10

10 ADSP-BF531/ADSP-BF532/ADSP-BF533:Blackfin嵌入式处理器数据表

2021-04-15 18:13:59 6

6 EE-197:ADSP-BF531/532/533 Blackfin®处理器多周期指令和延迟

2021-04-26 19:39:05 12

12 EE-129:ADSP-2192处理器间通信

2021-04-28 09:17:56 0

0 EE-298:评估ADSP-BF538/BF539 Blackfin®处理器的功耗

2021-05-10 11:57:57 5

5 ADSP-BF531/ADSP-BF532低功耗通用Blackfin处理器

2021-05-16 09:21:59 3

3 AD9576:双锁相环异步时钟发生器数据表

2021-05-16 12:57:55 0

0 ADSP-BF531/BF532/BF533黑球BSDL 169球PBGA包(02/2004)

2021-05-20 21:27:13 2

2 EE-153:ADSP-2191可编程锁相环

2021-05-21 08:05:41 0

0 ADSP-BF531/BF532/BF533黑丙烯BSDL 176-Pin LQFP包(02/2004)

2021-05-21 21:20:23 5

5 ADSP-BF531/BF532/BF533黑球BSDL 160型球CSP BGA包(02/2004)

2021-05-22 10:47:05 4

4 ADSP-2136x SHARC®处理器硬件参考(包括ADSP-21362/ADSP-21363/ADSP-21364/ADSP-21365/ADSP-21366处理器)

2021-05-23 18:48:17 3

3 ADSP-BF5xx/ADSP-BF60x Blackfin®处理器编程参考

2021-05-24 10:42:11 2

2 EE-297:评估ADSP-BF534/BF536/BF537 Blackfin®处理器的功耗

2021-05-26 11:21:42 0

0 ADSP-BF531/BF532/BF533修订版0.5、0.6的Blackfin异常列表

2021-05-27 11:00:59 0

0 ADSP-BF512/ADSP-BF514/ADSP-BF516/ADSP-BF518 Blackfin嵌入式处理器产品手册

2021-05-27 15:18:28 4

4 ADSP-BF533 EZ-KIT Lite为开发人员提供一种经济有效的方法,可以对ADSP-BF533 Blackfin处理器进行初步评估,适合包括音频和视频处理在内的各种应用。 该EZ-KIT

2021-06-03 12:06:42 2

2 ADSP-BF592 EZ-KIT Lite®是一种经济有效的评估套件,开发人员通过基于USB、可在PC中运行的工具集,便能对ADSP-BF592处理器进行初步评估。 利用该EZ-KIT Lite

2021-06-03 16:48:31 8

8 ADSP-BF531BF532BF533 2.53.3V IO Blackfin处理器IBIS数据文件160-Ball CSP BGA封装(092005)

2021-06-09 15:55:37 3

3 模拟锁相环和数字锁相环的主要区别在于它们的控制方式不同。模拟锁相环是通过模拟电路来控制频率和相位,而数字锁相环是通过数字信号处理技术来控制频率和相位。此外,模拟锁相环的精度较低,而数字锁相环的精度较高。

2023-02-15 13:47:53 6625

6625 pll锁相环倍频的原理 PLL锁相环倍频是一种重要的时钟信号处理技术,广泛应用于数字系统、通信系统、计算机等领域,具有高可靠性、高精度、快速跟踪等优点。PLL锁相环倍频的原理涉及到锁相环,倍频器

2023-09-02 14:59:24 4879

4879 信号倍频。在本文中,我们将详细探讨锁相环如何实现倍频。 锁相环的基本原理 在介绍锁相环如何实现倍频之前,我们先来回顾一下锁相环的基本原理。锁相环电路主要由三个部分组成:相位检测器(Phase Detector, PD)、环路滤波器(Loop Filter, LF)和振荡器(Voltage Cont

2023-09-02 14:59:37 5114

5114 的时序要求。尤其对于需要高速数据传输、信号采集处理等场景的数字信号处理系统而言,FPGA PLL的应用更是至关重要。本文将介绍FPGA锁相环PLL的基本原理、设计流程、常见问题及解决方法,以及该技术在外围芯片时钟提供方面的应用实例。 一、FPGA锁相环PLL基本原理 1.时钟频率的调

2023-09-02 15:12:34 5346

5346 基本PLL锁相环、整数型频率合成器和分数型频率合成器。下面将详细介绍这三种模式的作用和特点。 第一种:基本PLL锁相环 基本PLL锁相环是PLLf工作的最基本形式,它主要由比较器、低通滤波器、VCO和分频器组成。其基本工作原理是将输入信号和VCO输出的信号进行

2023-10-13 17:39:48 5281

5281 比较,通过不断调整内部振荡器的频率,使得输出信号的相位与参考信号的相位保持一致,从而实现同步。锁相环广泛应用于数字通信、音频解码、数字信号处理等领域。 在锁相环的基本结构中,包含一个相位检测器、一个积分环节、一个低通滤波器和一个控制振荡器。参考

2023-10-13 17:39:53 3088

3088 电子发烧友网站提供《ADSP-BF531在嵌入式语音识别系统中的应用.pdf》资料免费下载

2023-10-23 10:45:05 2

2 锁相环(PLL)基本原理 当锁相环无法锁定时该怎么处理的呢? 锁相环(Phase Locked Loop, PLL)是一种电路系统,它可以将输入信号的相位锁定到参考信号的相位。在锁相环中,反馈回路

2023-10-23 10:10:15 4763

4763 当锁相环无法锁定时,该怎么处理的呢?如何解决锁相环无法锁定? 锁相环作为一种常见的电路设计,具有广泛的应用领域。然而,在一些情况下,由于种种原因,锁相环可能无法正常锁定,这时需要进行一系列的测试

2023-10-30 10:16:33 3645

3645 频繁地开关锁相环芯片的电源会对锁相环有何影响? 锁相环(PLL)是一种被广泛应用在现代电子技术中的集成电路,它是一种反馈控制系统,可以将输入信号和本地参考信号同步。锁相环可用于电子时钟、数字信号处理

2023-10-30 10:16:40 1291

1291 锁相环到底锁相还是锁频? 锁相环(PLL)是一种常用的控制系统,主要用于同步时钟。它通过将被控信号的相位与稳定的参考信号进行比较,并产生相应的控制信号,使被控信号的相位保持与参考信号同步。这种控制

2024-01-31 15:25:00 4016

4016 电子发烧友网站提供《CDCVF2505时钟锁相环时钟驱动器数据表.pdf》资料免费下载

2024-08-21 12:17:52 0

0 解调和信号处理等方面。 锁相环PLL的工作原理 1. 基本组成 锁相环主要由三个部分组成:相位比较器(Phase Comparator)、低通滤波器(Low Pass Filter,LPF

2024-11-06 10:42:14 3778

3778 电子发烧友网站提供《ADSP-BF512/ADSP-BF514/ADSP-BF516/ADSP-BF518 Blackfin嵌入式处理器数据手册.pdf》资料免费下载

2025-01-03 15:37:04 0

0 电子发烧友网站提供《EE-229: ADSP-BF531/BF532/BF533 Blackfin功耗估算.pdf》资料免费下载

2025-01-06 15:22:15 0

0 电子发烧友网站提供《AN-813: ADSP-BF533/ADSP-BF561 Blackfin处理器与高速并行ADC接口.pdf》资料免费下载

2025-01-06 14:36:04 0

0 电子发烧友网站提供《EE-197:ADSP-BF531/532/533 Blackfin处理器多周期指令和延迟.pdf》资料免费下载

2025-01-08 14:39:05 0

0 ADI公司早期的ADSP-BF531、ADSP-BF532和ADSP-BF533产品系列具备Blackfin处理器的所有简单易用和架构上的特性。这三个处理器全部完全引脚兼容,仅在其性能和片上存储器

2025-05-12 16:27:46 1206

1206

电子发烧友App

电子发烧友App

评论