1. 背景 这篇文章主要介绍了DDR3IP核的写实现。 2. 写命令和数据总线介绍 DDR3 SDRAM控制器IP核主要预留了两组总线,一组可以直接绑定到DDR3 SDRAM芯片端口,一组是留给

2020-12-31 11:17:02 6783

6783

有谁需要ALTERA的ip核,qq57694560,cjfwindy@163.com [此贴子已经被作者于2009-10-14 14:26:18编辑过]

2008-11-16 19:50:33

我用的是CYCLONEIII的芯片,定制DDR2 IP核,之后直接用SINALTAP进行信号抓取,发现无法读写的原因是local_init_done 一直为低,就像XILINX里

2013-04-27 09:46:54

本帖最后由 dybttkl 于 2015-11-1 13:26 编辑

用的cycloneiii 里面的ddr2 ip核。感觉网上的资料很少,仿真的倒很多,但是真正到用户接口那段时序的解释却一个也没有。为何没人写个教程

2015-11-01 13:24:54

研究了很久,实在弄不出来了,有没有人用过Altera的PCIe IP核???急求!!!谢谢!!!求大神帮忙......

2016-05-26 09:12:33

小弟用的quartus ii软件,调用altera公司的一个乘法器lpm_mult,无结果输出,是不是调用的IP核都要收费呢,有没有办法破解呢????

2015-06-05 11:23:31

以下主题概述了Altera的外部内存接口解决方案。

Altera提供最快、最高效、延迟最低的内存接口IP核。Altera的外部存储器接口IP设计用于方便地与当今更高速的存储器设备接口。

Altera

2023-09-26 07:38:12

Altera系列FPGA芯片IP核详解

2020-06-28 13:51:01

Altera_IP核,仅供参考

2016-08-24 16:57:15

实现特权同学的例程 特权FPGA VIP视频图像开发套件例程详解2——DDR2控制器读写测试 时,进行IP核配置时,进入下一步配置参数时,变成黑屏重装软件也不行

2018-01-24 08:23:17

使用altera的FFTIP核的可变流结构进行FFT时,输出为什么跟实际情况是倍数关系

2016-09-20 19:18:10

最近在使用altera的FIR IP核做半带滤波器,quartus ii软件也破解了,firIP核也破解了,modelsin仿真也通过了,但是下载不了.sof文件到开发板,大家有用FIR IP核成功实现下板的经验吗,求大神指点呀。谢谢!

2018-05-11 16:01:15

altera公司IP核使用手册

2012-08-15 13:11:24

altera公司IP核使用手册,分享给想学习altera公司FPGA的IP核使用的亲们~~

2013-02-16 22:40:19

问题:采用altera公司的ep4ce6e22c8控制器的一对差分引脚实现差分输入输出配置功能尝试方法:尝试配置LVDS IP核,但发现只有单独的输入输出,如图

2019-10-20 22:13:05

机制对当前变长分组骨干网的流量控制还是具有重要的参考价值,所以有必要对ATM的流量控制及其实现方式进行深入的研究。 IP核是一段具有特定电路功能的硬件描述语言代码,该程序与集成电路工艺无关,因而

2011-09-27 11:54:25

CAN控制器IP核(可直接在Nios II中使用)

2016-08-24 16:54:21

(Intellectual Property Core)。本文介绍USB 2.0设备控制器IP中的AHB接口部分设计。1设计概述1.1协议概述 设计前首先需要了解USB和AHB数据传输的特点

2019-05-13 07:00:04

大家好,有没有谁比较熟悉ALTERA公司的VIP系列ip核,我们用该系列IP核中的某些模块(主要是scaler和interlacer)来实现高清图像转标清图像(具体就是1080p50转576i30

2015-04-13 14:12:18

modelsim 仿真 altera IP核(ROM,RAM实例)急求大神们ROM和RAM 的综合仿真代码

2015-11-19 21:02:57

本文介绍一款USB OTG IP核的设计与实现,该设备控制器可作为IP核用于SoC系统中,完成与主机控制器的通信,并能与普通的USB从设备进行通信。

2021-04-29 06:47:00

`例说FPGA连载41:DDR控制器集成与读写测试之DDR2 IP核接口描述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc 如图

2016-10-27 16:36:58

用 quartus 生成一个ddr2的ip核,选择了生成仿真模型,但生成不了,文件目录下没有example.v,只有一个对应 的sdc文件 。 另外生成报告里还有 一个warning ,,求指导

2017-09-07 11:48:09

Altera系列FPGA芯片IP核详解

2016-08-19 17:24:48

工具,经面向硬件电路的仿真验证,本文的方法可实现OC-48接口(2.5Gb/s)上线速分组的IP碎片重组,并具有硬件开销小,可扩展性好的特点。关键词: IP碎片;FPGA;RLDRAM控制器;最大传输

2008-10-07 11:00:19

PCI接口控制器兆核函数(即接口IP)及相关测试平台,通过选择合适的芯片速度,可以满足运行在33MHz或66MHzPCI时钟下的时序要求,支持Altera的Stratix II、Stratix

2018-12-04 10:35:21

此提供了新的解决方案。IP核(IP Core)是具有特定电路功能的硬件描述语言程序,可较方便地进行修改和定制,以提高设计效率[3]。本文研究了基于FPGA的数据采集控制器IP 核的设计方案和实现方法,该IP核既可以应用在独立IC芯片上,还可作为合成系统的子模块直接调用,实现IP核的复用。

2019-07-09 07:23:09

任务需求来定制显示控制功能,可以增强系统可靠性和设计灵活性,降低了成本。目前针对LCD 显示屏设计的控制器IP 核文章较多[1-2],但对于TFT-LCD 触控屏设计的控制器IP 核文章较少[3],而且

2018-11-07 15:59:27

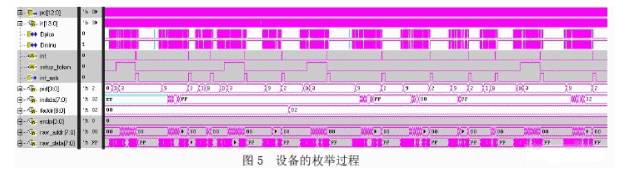

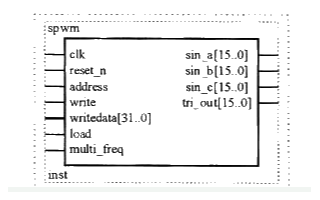

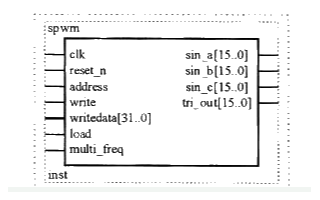

,以及对应的波形图和 Verilog HDL 实现。我们调取的 DDR3 SDRAM 控制器给用户端预留了接口,我们可以通过这些预留的接口总线实现对该 IP 核的控制,本章节将会讲解如何根据

2022-02-08 07:08:01

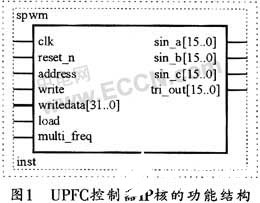

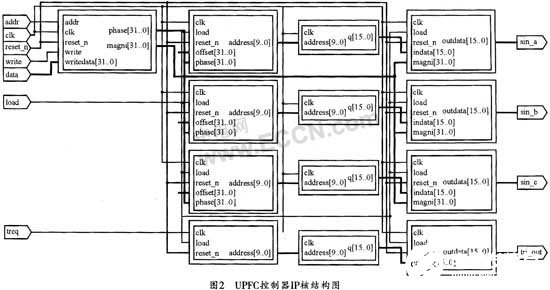

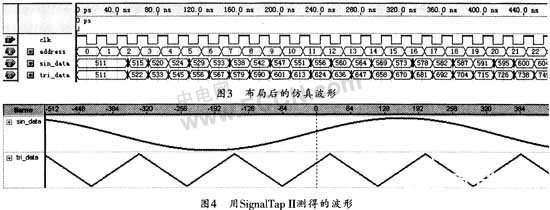

本文利用Altera公司的Quartus开发工具设计了一个基于Avalon总线接口的UPFC控制器IP核,以便于和NiosII组成一个完整的控制系统。

2021-04-08 06:25:12

本人想使用altera的以太网IP核tse核,发现Quartus里面并没有告诉怎样控制这个核。请问大家是怎样控制这个IP核的呢?完全用Verilog代码编写控制程序,好像很复杂呀,难道只能通过NiosII软核吗

2015-01-22 14:55:31

请问Altera RAM IP核怎么使用?

2022-01-18 06:59:33

本文介绍的在电能质量监测系统中信号采集模块控制器的 IP核,是采用硬件描述语言来实现的。

2021-04-08 06:33:16

系统级设计,设计人员现在使用SOPC Builder工具时,可以选择Freescale?、ARM?或者Altera软核处理器以及50多种其他的知识产权(IP)模块。 &

2008-06-17 11:40:12

IP核的Verilog程序进行综合时,可选用Altera公司的CycloneIIEP2C35评估板。该板有33216个逻辑单元,105个M4k存储模块,35个18×18乘法单元,4个PLL和475个I

2019-06-03 05:00:05

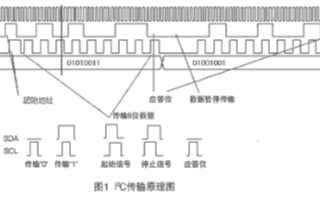

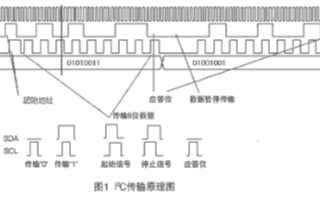

,我国也迫切需要发展自己的IP核。本文针对I2C的主方式串行扩展通信的特点,详细给出设计过程和结果。1 IP核简介 IP核是指:将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器、SDRAM

2019-04-12 07:00:09

I2C总线控制器 altera提供

The I2C Controller was designed for the MC68307 uC, provides a simplified

2008-05-20 10:25:01 251

251 TC35C25系列PWM控制器是目前取3525开关电源控制器的理想器件,本文介绍TC35C25系列pWM控制器的优点和特性外,重点讲述该控制器的输出级,振荡器及其同步软启动以及压锁定部分的工

2008-11-19 18:18:50 19

19 本文提出了一种运动控制器软IP 的设计方案,该控制器可以控制4 个轴的步进电机或数字伺服电机,可以进行各轴独立的定位控制、速度控制,也可任选2 轴或3 轴来进行直线、圆弧

2009-07-07 15:22:50 21

21 研究了C8051 微控制器IP 软核的参数化设计。首先介绍了指令系统的设计,其次从可重配置的存储器容量、可取舍的并行输入/输出端口、是否产生UART 和定时/计数器模块,以及可重

2009-07-30 11:12:33 17

17 本文介绍一款USB 设备控制器IP CORE 的设计与实现。论文首先介绍了USB 设备控制器的设计原理,模块划分及每个模块的功能。然后介绍了该IP CORE 在ModelsimSE 中的功能仿真及FPGA 验证结

2009-08-06 11:39:00 8

8 介绍了基于MicroBlaze 软核处理器的可编程片上系统结构。提出了一种LCD 控制器IP 核的设计方法。该控制器具有片上外设总线接口,和其它标准IP 核一起组成以MicroBlaze 为核心的片上系

2009-08-31 10:58:53 11

11 本文讨论了基于Avalon 总线流传输的配置LCD 显示控制器IP 核的设计,根据自顶向下的设计思想,将IP 核进行层次功能划分设计,并对IP 核的仿真验证,最后加入到NiosII 系统中。该I

2009-11-30 14:33:46 16

16 介绍了基于IP 的可重用的SOC 设计方法;选用MC8051 IP 核为核心控制器,自主开发了UART IP 核、I2C IP 核、USB IP 核,采用Wishbone 片上总线架构,集成了一个MCU 系统;同时设计了针对此MCU

2009-11-30 15:06:20 33

33 本文提出了一种运动控制器软IP 的设计方案,该控制器可以控制4 个轴的步进电机或数字伺服电机,可以进行各轴独立的定位控制、速度控制,也可任选2 轴或3 轴来进行直线、圆弧

2009-12-04 11:52:52 14

14 用硬件描述语言verilog HDL 设计实现了一种MCU&USB 设备控制器IP 核。论文首先简要介绍了设计的背景,重点对自主研发的将MCU&USB 控制器集成于一个芯片的设计和研究分析。最后

2010-01-20 11:44:09 22

22 基于Avalon总线的可配置LCD 控制器IP核的设计

本文讨论了基于Avalon 总线流传输的配置LCD 显示控制器IP 核的设计,根据自顶向下的设计思想,将IP 核进行层次功能

2010-02-09 09:34:44 27

27 本文以改善UPFC 动态性能为出发点,指出了UPFC 研究中存在的问题:1 目前针对UPFC 系统所建立的模型不完整,使得控制系统设计中存在缺陷;2 没有一个有效、合理的潮流调节器参数

2010-02-22 10:00:31 19

19 介绍了系统芯片SOC的概念和M8051 IP软核的原理,给出了视频字符叠加器VAD_SOC中M8051 IP软核的作用,详细介绍了I2C主控制器模块的设计,给出了功能仿真波形,最后对M8051IP软核在视频

2010-07-05 14:31:33 47

47 本文详述了一种基于AMBA总线接口的IIC总线控制器IP核设计,给出了该IP核的系统结构以及各个子模块的详细设计方法,并对该IP核进行了功能仿真、FPGA原型验证,可测性设计以

2010-07-17 16:20:22 21

21 提出了一种采用基于NiosII处理器的通用AD IP核来实现嵌入式数据采集系统的新方案。它能将市面上任意一款AD芯片制作成IP核并集成到NiosII系统中使用,且整个IP核的控制与运算逻辑由

2010-07-30 11:39:16 50

50 I2C器件接口IP核的CPLD设计

根据单片机I2C串行扩展的特点,在EDA软件MaxplusII的环境下,利用AHDL语言,建立IP核。此设计利用状态机实现,在给出设计的同时详细说明IP核的建立

2009-03-28 16:21:35 1351

1351

USB2.0设备控制器IP核的AHB接口技术

介绍了USB2.0设备控制器IP核的AHB接口的设计。解决了双时钟域问题;实现了多事务DMA控制,减少了块传输的中断次数;

2009-03-29 15:14:15 1990

1990

摘 要: 根据单片机I2C串行扩展的特点,在EDA软件MaxplusII的环境下,利用AHDL语言,建立IP核。此设计利用状态机实现,在给出设计的同时详细说明IP核的建立过程,并下载到

2009-06-20 13:36:12 1065

1065

基于PCI IP核的码流接收卡的设计

本文介绍了一种基于Altera公司的PCI接口IP核的DVB码流接收系统的硬件设计方案及设计要点的分析。该设计采用Altera公司的新一代FPGA

2009-09-26 18:02:08 912

912

MCU/USB设备控制器IP核的设计

1 引言

在传统的计算机系统上常采用串口(如RS232)和并口连接外围设备,但串口和并口都存在着通信速度 慢

2009-12-08 11:11:08 927

927

0 引言

NIOSⅡ是Altera公司推出的第二代IP软核处理器。它与其他IP核可构成SOPC系统的主要部分。Altera SOPC Builder提供有NiosⅡ处理器及一些常用外设接口,因此,对于一

2010-08-16 09:44:23 1734

1734

提出了一种基于 PicoBlaze 的Nand Flash控制器的实现方法。PicoBlaze是Xilinx公司开发的8位嵌入式微控制器IP核。首先介绍了PicoBlaze的概念和实现方式,接着详细描述了基于PicoBlaze核心的控制器

2011-06-13 15:48:36 41

41 本内容写出了CAN总线控制器IP核的代码,并做出了详细分析

2011-06-28 11:39:42 6798

6798 为满足嵌入式系统中专用芯片功能不能达到系统要求的现状,设计出一种功能可扩展的I2C slave控制器,这种控制器与传统的专用I2C芯片不同。专用的I2C芯片的功能具有固定性,只能实现

2011-10-25 16:58:02 60

60 本文侧重于介绍IP 模块中组件控制器的设计和实现。一个基于FPGA 的LCD 控制器设计作为例子被介绍。这个组件控制器设计属于固核IP 设计,也就是软硬结合的方法。设计内容主要包括电

2011-12-22 14:00:11 1634

1634

根据Nios II处理器的Avalon总线规范,设计了一款面向步进电机的控制器IP核。该定制IP核采用软、硬件协同设计的方法,功能符合Avalon总线的读写传输时序,具有完备的步进电机驱动能力。仿

2011-12-23 14:02:32 44

44 随着可编程逻辑器件的不断进步和发展,FPGA在嵌入式系统中发挥着越来越重要的作用。本文介绍的在电能质量监测系统中信号采集模块控制器的 IP核,是采用硬件描述语言来实现的。

2012-05-22 16:01:22 1808

1808

介绍一款基于SOPC的TFT-LCD触控屏控制器IP核的设计与实现。采用Verilog HDL作控制器的模块设计,并用ModelSim仿真测试,验证其正确性;利用嵌入式SOPC开发工具,在开发板上完成触控屏显示

2012-08-13 17:22:18 53

53 altera公司IP核使用手册(英文版),需要的可下载 Chapter 1. About this MegaCore Function Release Information

2012-08-15 15:15:31 0

0 IP核生成文件:(Xilinx/Altera 同) IP核生成器生成 ip 后有两个文件对我们比较有用,假设生成了一个 asyn_fifo 的核,则asyn_fifo.veo 给出了例化该核方式(或者在 Edit-》Language Template-》C

2012-08-15 15:57:09 35

35 本设计基于FPGA的彩色触摸屏控制器能够实现颜色深度为24 bit,分辨率为480×272的TFT-LCD控制和ADS7843芯片的时序控制,为后续IP核的编写工作打下了基础。

2013-01-07 11:08:20 3441

3441

基于SOPC的步进电机加减速PWM控制器IP核设计

2016-05-03 13:52:59 18

18 TC35C25系列PWM控制器是目前取代3525开关电源控制器的理想器件。本文除介绍TC35C25系列PWM控制器的优点和特性外,重点讲述该控制器的输出级、振荡器及其同步、软启动以及欠压锁定部分的工作原理;同时还给出了有关的重要参数及典型电路。

2016-05-10 14:24:39 8

8 基于Avalon总线的非标准以太网控制器IP核设计_薛毅

2017-03-19 11:33:11 1

1 提出一种便于用户操作并能快速运用到产品的DDR2控制器IP核的FPGA实现,使用户不需要了解DDR2的原理和操作方式的情况下,依然可以通过IP核控制DDR2。简单介绍了DDR2的特点和操作原理,并

2017-11-22 07:20:50 5930

5930

DMA控制器是常见的总线设备之一,很多厂商都有自己的DMA控制器IP核。比如嵌入式处理器的龙头ARM公司就有自己的DMA控制器解决方案提供给客户,另外像Freescale,Fujitsu等芯片

2017-12-06 13:41:59 4363

4363

策略对UPFC性能的影响。首先基于UPFC的基本结构系统介绍了2种控制策略的控制思路,然后利用相对增益矩阵方法和阻尼转矩分析方法分别比较了两种控制策略下对UPFC交互影响的情况和其阻尼控制器向系统提供阻尼的情况。最后,通过4机2区域系统的计算,发现相角控制下UPFC交互影响更大

2018-01-31 10:15:37 3

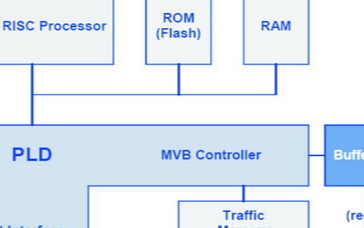

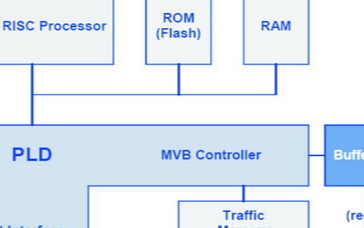

3 本设计正是基于SOPC的思想,开发实现自主知识产权的MVB收发控制器IP核,借助于QuartersII开发工具,集成至Altera FPGA器件内部,构建SOC片上系统实现MVB网卡基本功能,相比传统国外的MVB网卡,大大简化了系统的结构,降低了开发难度。

2020-04-18 08:08:00 4682

4682

随着IC产业的发展,IP核的需求越来越高。微控制器MCU(Micro Control Unit)是嵌入式系统的核心,8位MCU IP核具有很高的通用性和灵活性,广泛地应用于工业控制、机械设备、家用电器以及汽车等各个领域。本文设计的MCU IP核与Microchip公司的PIC16C57完全兼容。

2020-01-10 07:59:00 3247

3247

该控制器具有Avalon总线接口,可与其它标准IP 核一起构成以NiosⅡ为核心的片上系统,并可编写驱动程序。 NIOSⅡ是Altera公司推出的第二代IP软核处理器。它与其他IP核可构成SOPC系统的主要部分。

2018-09-29 08:35:00 7652

7652

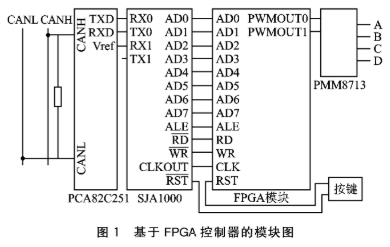

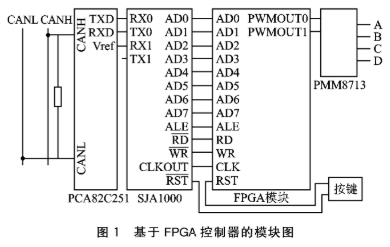

和Altera 公司部分FPGA 上的资源利用和性能情况。此外,基于SOPC技术将处理器软核和CAN 控制器软核集成在单片FPGA 中,构建了一种新型的CAN 总线系统,并在该系统中完成了对控制器软核的测试验证。

2019-07-19 17:48:41 27

27 学完SDRAM控制器后,可以感受到SDRAM的控制器的书写是十分麻烦的,因此在xilinx一些FPGA芯片内已经集成了相应的IP核来控制这些SDRAM,所以熟悉此类IP核的调取和使用是非常必要的。下面我们以A7的DDR3 IP核作为例子进行IP核调取。

2019-11-10 10:28:45 5993

5993

统一潮流控制器(Unified Power Flow Con-troller,简称UPFC)是一种可以较大范围地控制电流使之按指定路经流动的设备,它可在保证输电线输送容量接近热稳定极限的同时又不

2020-03-19 10:00:47 2622

2622

由于CPLD数字设计结构化的趋势,将出现针对CPLD不同层次的IP(Intellectual Property)核。各个IP核可重复利用,可大大提高设计能力和效率。国外各大公司都推出了专门的IP核,我国也迫切需要发展自己的IP核。本文针对I2C的主方式串行扩展通信的特点,详细给出设计过程和结果。

2020-04-07 09:54:10 4073

4073

分析了CAN控制器SJA1000的特点及CAN协议通信格式。设计了控制器SJA1000的IP软核,能为应用提供一个性能优良的、易于移植的控制器SJA1000,实现了对步进电机的控制。

2020-04-12 10:55:00 3579

3579

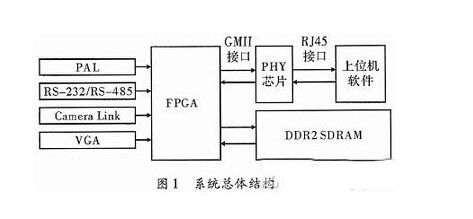

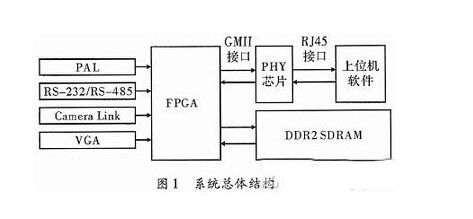

图2显示了系统FPGA模块的具体结构,以及各个子模块之间的关系。为缩短设计周期,提高设计质量,在模块中分别调用了Altera公司现有的以太网控制器IP核和DDR2控制器IP核资源。

2020-10-07 10:58:00 2112

2112

2014.4 1、IP Catalog中搜索MIG,点击相应IP进入如下配置界面。 (1)DDR控制器的个数,根据你的实际需求而定,需要几个控制器,你心里应该清楚吧。 (2)MIG IP核的用户侧

2020-11-26 15:02:11 10426

10426

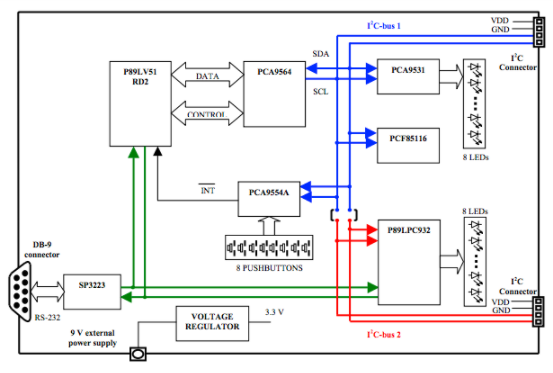

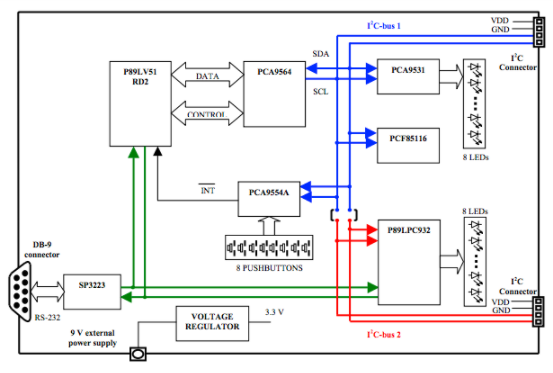

PCA9564 评估板展示了飞利浦 PCA9564 I2 C 总线控制器在主设备(连接到其并行总线及其控制信号)与任何连接到其 I2 C 总线的主设备和从设备之间进行接口的能力。评估板装有以下器件

2021-06-17 17:26:46 4264

4264

本文的目的是使用基于智能控制器的 UPFC 设备提高电力系统的稳定性和可靠性。 UPFC 设备在各种故障条件下由模糊逻辑控制器控制。 模糊逻辑控制器将电压、相角等电力系统参数与参考值进行比较,产生

2021-11-29 16:04:59 0

0 电子发烧友网站提供《TPS2359双插槽ATCA AdvancdMC控制器,带I2C评估模块.pdf》资料免费下载

2024-12-20 15:48:07 0

0

![]()

电子发烧友App

电子发烧友App

评论